アドバンスト・マイクロ・ディバイシズ・インコーポレイテッドにより出願された特許

431 - 439 / 439

パッドコンディショナーのセンサー信号を用いて化学機械研磨をコントロールするための方法とシステム

本発明によれば、パッドコンディショニングシステムのドライブアセンブリから得られたモータ電流信号のようなセンサ信号が、CMPシステムにおける一つあるいはそれ以上の消耗品(113)の状態を推定するように用いられるシステム及び方法が提供される。  (もっと読む)

(もっと読む)

抵抗構造を形成するための方法

半導体基板を覆うように形成された抵抗構造(102)は、シリサイドブロック層(120)でマスクされ、シリサイド化されない抵抗構造部分とシリサイド化される抵抗構造の部分を限定する。シリサイドブロック層(120)は異なるプロセスを容易にするように変更される。  (もっと読む)

(もっと読む)

読み込みマージンの寿命を改善するためのデュアルセルメモリデバイスの動作方法

第1電荷格納セル(38、40)及び第2電荷格納セル(38、40)を有するデュアルセルメモリデバイス(6)にプログラミングを行う方法である。この方法の一局面によれば、この方法は、前記第1電荷格納セル及び前記第2電荷格納セルを過消去し、前記メモリデバイスの消去状態の電圧閾値を通常状態の電圧閾値よりも低下させる工程を備えることができる。この方法の他の局面によれば、この方法は、前記第1電荷格納セル及び前記第2電荷格納セルが同一のデータ状態になるようにプログラミングし、そして、プログラミングが行われた前記第2電荷格納セルが前記データ状態に対応する電荷を格納することを検証する工程を備えることができる。検証できない場合は、両方の電荷格納セルに再度パルスを印加する。  (もっと読む)

(もっと読む)

フラッシュメモリデバイスの特性を改善する方法

半導体デバイスを製造する方法において、シリコン基板(62)上にゲート酸化膜(60)を提供する。このゲート酸化膜(60)上に第1ポリシリコン層(64)を提供し、第1ポリシリコン層(64)上に絶縁層(66)を提供し、またこの絶縁層(66)上に第2ポリシリコン層(68)を提供する。適切なマスキングを実行した後にエッチングステップが実行されると、シリコン基板を露出させ、かつこのシリコン基板上にスタックゲート構造を形成すべく、第2ポリシリコン層、絶縁層、第1ポリシリコン層、およびゲート酸化膜の一部を除去するようにこれらの層がエッチングされる。スタックゲート構造(72)上に薄い酸化膜(80)を成長させるべく、短時間(例えば10秒から20秒)の急速熱アニールを実行する。それから、急速熱アニールによって形成された酸化膜(80)上に第2酸化膜(82)をたい積する。

(もっと読む)

(もっと読む)

高精度メモリ読み出しオペレーション用選択回路

メモリ読み出しオペレーション中に、ターゲットセル(305)における電流を検知する選択回路が開示される。一実施形態によれば、検知回路は、検知回路(360)に接続された検知回路セレクタ(364)と、グラウンドに接地された接地セレクタ(362)と、を含む。接地セレクタ(362)は、ターゲットセル(305)の第1ビット線(316)をグラウンドに接続し、検知回路セレクタ(364)は、ターゲットセル(305)の第2ビット線(321)を検知回路(360)に接続する。検知回路セレクタ(364)は、読み出しオペレーション中に、検知回路(360)に第1隣接セル(355)の第3ビット線(341)を更に接続する。第1隣接セル(355)は、第2ビット線(321)をターゲットセル(305)と共有する。  (もっと読む)

(もっと読む)

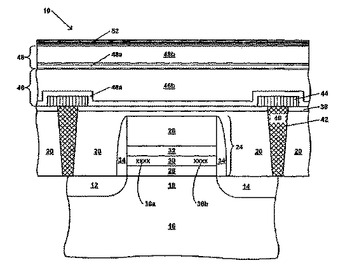

BEOLプロセスにおいて、UVによって誘発されたSONOSデュアルビットのフラッシュメモリデバイスの電荷を低減するUVブロック層

SONOSフラッシュメモリセル(24)をUVにより誘発される電荷から保護する方法であって、SONOSフラッシュメモリセル(24)を半導体デバイス(10、50)に製造するステップと、SONOSフラッシュメモリセル(24)上に、少なくとも1つのUV保護層(38、46、48、又は52)を蒸着させるステップとを含み、UV保護層には実質的にUV不透過性の材料が含まれる。SONOSフラッシュメモリセル(24)と、少なくとも1つのUV保護層(38、46、48又は52)(UV保護層には実質的にUV不透過性の材料が含まれる)を含むSONOSフラッシュメモリデバイス(10、50)が提供される。  (もっと読む)

(もっと読む)

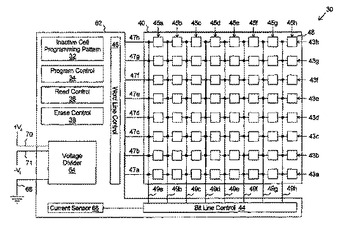

非揮発性メモリセルアレイの非活性領域に隣接する非揮発性メモリセルを読み出すための改善された方法

メモリセル48のアレイ30にデータパターンをストアし、再生するための方法であり、活性コラム45b及び45gと、不活性コラム45c及び45fとを含み、活性コラム45b及び45gにデータパターンをストアする。不活性メモリセルプログラミングパターン32が識別される。バルク消去中、過消去及び活性メモリセル48への電流リークを回避するために定期的に電荷をストアする目的で電荷がストアされる、不活性コラム45c及び45fのメモリセル48の全てあるいは選択された複数のメモリセルを、前述の不活性メモリセルプログラミングパターン32が識別する。  (もっと読む)

(もっと読む)

二重用途レジスタを識別しているアドレス指定パターンに基づいたデータ投機

システムは、メモリファイル(136)と実行コア(124)とを備え得る。メモリファイル(136)は、アドレス指定パターン(406)およびタグ(408)を記憶するように構成されたエントリ(420)を有し得る。メモリファイル(136)は、メモリオペレーションのアドレス指定パターンとエントリ(420)に記憶されているアドレス指定パターン(406)とが一致する場合に、タグ(408)が識別するデータ値をメモリオペレーションの投機的な結果にリンクするように構成され得る。メモリオペレーションのアドレス指定パターンは論理レジスタの識別子を含み、メモリファイル(136)は、メモリオペレーションのアドレス指定パターンとエントリ(420)に記憶されているアドレス指定パターン(406)とが一致するかどうかを判定するために、論理レジスタが、汎用レジスタまたはスタックフレームポインタレジスタかいずれとして指定されるかを予測するように構成され得る。実行コア(124)は、このメモリオペレーションに依存する別のオペレーションを実行するときに、投機的な結果にアクセスするように構成され得る。  (もっと読む)

(もっと読む)

配線構造およびその製造方法

【目的】 プラズマ金属エッチングにおける配線のアンダーカットを防止し得る配線構造およびその製造方法を提供する。

【構成】 窒素を含むチタン層(Tix Ny 層)22を、チタン層12と酸化物基板14との間、または、チタン層12とアルミニウム層16との間に介在させる。

(もっと読む)

431 - 439 / 439

[ Back to top ]