チャータード・セミコンダクター・マニュファクチャリング・リミテッドにより出願された特許

1 - 8 / 8

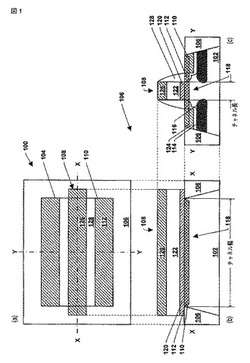

電界効果トランジスタ及びその製造方法

【課題】高品質な特性を有する電界効果トランジスタ及びその方法を提供する。

【解決手段】素子分離領域106間のソース/ドレイン領域114、及びポケット領域116を含んでいる半導体基板102と、素子分離領域間の半導体基板の上面のトレンチ110内にあって、(100)面を有する底面及び上面と、2つ以上の平面を有する側面とを有するシリコンゲルマニウム層112と、ゲート絶縁層120、ゲート電極122、及びサイドスペーサ128を含むシリコンゲルマニウム層上のゲート構造と、ゲート構造によって覆われていないシリコンゲルマニウム層及び半導体基板の上部分上のメタルシリサイド124とを備え、シリコンゲルマニウム層は、チャネル長方向において、ゲート構造の下で側面を有していない。

(もっと読む)

半導体集積回路装置の製造方法

【課題】本発明が解決しようとする技術的な課題は、安定したエッチングが可能な半導体集積回路装置の製造方法を提供するものである。

【解決手段】半導体集積回路装置の製造方法が提供される。前記半導体集積回路装置の製造方法は、ゲート電極120と、前記ゲート電極の両側壁に形成された犠牲窒化膜スペーサ150と、前記犠牲窒化膜スペーサにセルフアラインされたソース/ドレーン領域160とを含む電界効果トランジスタを形成し、酸化膜に対する窒化膜の選択比が1を超えるフッ酸により前記犠牲窒化膜スペーサを選択的に除去し、前記ゲート電極の両側壁上に、前記電界効果トランジスタのチャネル領域内に引張あるいは圧縮ストレスを誘導するストレス膜を形成することを含む。

(もっと読む)

電界効果トランジスタデバイスおよびその製造方法

【課題】電界効果トランジスタ(FET)を製造する方法を提供する。

【解決手段】この方法は、半導体基板上にゲート構造を形成するステップと、基板内に凹部を形成して、凹部内に第2の半導体材料を埋め込むステップとを含む。ゲート構造は、ゲート誘電体層、導電層、および絶縁層を含む。前記ゲート構造の形成は、ゲート構造内の導電層を凹ませるステップを含み、導電層を凹ませるステップと、基板内に凹部を形成するステップとは、単一ステップで実行される。また、FETデバイスが提供される。

(もっと読む)

埋め込み型L字形スペーサを使用して半導体デバイスを形成する方法およびその半導体デバイス

【課題】L字形スペーサを埋め込んだ半導体デバイスを形成する方法を提供する。

【解決手段】この方法は、基板のゲート領域の各側にL字形スペーサを画成するステップと、L字形スペーサを酸化膜に埋め込んで、酸化膜がL字形スペーサの側縁から所定の距離まで基板の一部を覆うようにするステップとを含む。さらに、酸化膜を除去して、L字形スペーサを露出させる。

(もっと読む)

半導体デバイスでの2応力記憶技術

【課題】nFETとpFETの両方のためのSMT(応力記憶技術)を提供すること。

【解決手段】nFET104の上に引っ張り応力層120を、pFET106の上に圧縮応力層122を形成すること、半導体デバイスに応力を記憶するようにアニール150すること、および応力層を除去することを含む。圧縮応力層122は、高密度プラズマ(HDP)堆積方法を使用して堆積された高応力窒化珪素を含むことができる。アニールするステップは、ほぼ400〜1200℃の温度を使用することを含むことができる。高応力圧縮性窒化珪素またはアニール温度あるいはその両方によって、圧縮応力記憶がpFET106に維持されることが保証される。

(もっと読む)

集積回路応力制御システム

【課題】NMOSデバイス性能を劣化させることなくPMOSデバイス性能を高めるように浅いトレンチ分離部が取り入れられるようにする集積回路応力制御システムを提供する。

【解決手段】集積回路応力制御システム(400)が提供される。基板(106)の上にゲート(108)が形成され、基板(106)にチャネル(112)が形成される。ゲート(108)の周りにソース/ドレイン(118)が形成される。基板(106)に浅いトレンチ分離部(132)が形成され、浅いトレンチ分離部(132)はチャネル(112)上に歪を生じさせる。基板(106)に応力抑制構成物(134)が形成される。

(もっと読む)

半導体装置、および半導体装置を製造する方法

【課題】半導体装置(100)を製造するための方法(800)および機器は、第1の領域(108)および第2の領域(106)を有する基板(102)を提供する。

【解決手段】第1の領域に犠牲第1ゲート(112)が形成される。第1の領域にソース/ドレイン(204)が形成される。第2の領域に第2の領域のゲート誘電体(306)が形成される。第2の領域のゲート誘電体上に第2の領域のゲート(302)が形成される。第2の領域に第2の領域のソース/ドレイン(304)が形成される。犠牲第1ゲート、ソース/ドレイン、第1の領域、および第2の領域の真上に犠牲層(314)が形成される。犠牲第1ゲート(112)が露出される。犠牲第1ゲートを除去することによってゲートスペース(502)が形成される。ゲートスペース内に第1の領域のゲート誘電体(504)が形成される。第1の領域のゲート誘電体上に第1の領域のゲート(506)が形成される。犠牲層が除去される。

(もっと読む)

位相シフトマスクを製作するための方法および位相シフトマスク

【課題】位相シフトマスク(104)を製作するための方法(1100)を提供する。

【解決手段】遮光層の部分(206)を上に有する、溝のある位相シフトマスク(104)が形成される(1102)。次に、反射防止材料からなる層(802)が、溝のある位相シフトマスク(104)および遮光層の部分(206)上に形成される(1104)。次いで、反射防止材料(802)は、溝のある位相シフトマスク(104)の水平表面上、および遮光層の部分(206)の水平表面上で除去される(1106)。

(もっと読む)

1 - 8 / 8

[ Back to top ]