Fターム[2G132AE21]の内容

電子回路の試験 (32,879) | 試験装置(テストヘッドを除く) (4,743) | 実使用時環境を達成するための回路 (32)

Fターム[2G132AE21]に分類される特許

1 - 20 / 32

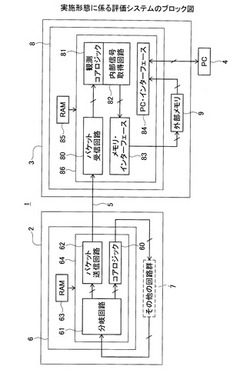

評価システム

【課題】製品ボードに搭載される製品FPGAの端子数に制限されず、内部信号の観測を可能とし、製品FPGAを製品ボードに搭載された実使用状態で論理検証することが可能な評価システムを提供することを課題とする。

【解決手段】評価システム1は、製品ボード2、評価ボード3、およびそれらを接続するシリアル・インターフェース5を備える。製品ボード2に搭載される製品FPGA6はコアロジック60に入力される外部入力信号を分岐する分岐回路61を備える。評価ボード3は観測FPGA8を備える。観測FPGA8はコアロジック60と論理的に等価な観測コアロジック81および観測コアロジック81の内部信号を取得する内部信号取得回路82を備える。コアロジック60の実動作に供される外部入力信号が評価ボード3に送られ観測コアロジック81がコアロジック60の実動作と等価に動作する。その時の内部信号を取り出し論理検証を行う。

(もっと読む)

試験装置

【課題】高速多値信号を試験可能な試験装置を提供する。

【解決手段】パターン発生器PGは、I/O端子PIOに入力される被試験信号S1と比較すべきしきい値電圧Vthを指定する制御データS11を発生するとともに、被試験信号S1としきい値電圧Vthの比較結果の期待値を示す期待値データEXP2を発生する。しきい値電圧発生器10は、制御データS11に応じた電圧レベルを有するしきい値電圧Vthを、第1タイミング信号St1が指定する設定タイミングtVごとに生成する。レベルコンパレータCpは、被試験信号S1の電圧レベルをそれと対応するしきい値電圧Vthと比較する。タイミングコンパレータTCは、レベルコンパレータCpの出力S3を、第2タイミング信号St2が指定するストローブタイミングでラッチし、比較信号S4を生成する。タイミング調節部50は第1タイミング信号St1の位相を調節する。

(もっと読む)

半導体試験装置及びそのテスト方法

【課題】メモリのテスト時の消費電流を抑え、メモリテスト時の周波数を高速化する。

【解決手段】制御回路103は、第1及び第2のテストパタンジェネレータ104、105によるテストがともにライトの場合、一方のテストパタンジェネレータによるテストシーケンスの実行を許可し、他方のテストパタンジェネレータに対してテストシーケンスの実行を不許可とし、一方のテストパタンジェネレータからメモリグループ101、102の対応する一方のグループに対してライトのテストパタンを出力し、他方のグループに対するライトの実行を、一方のグループのライトのテストサイクル単位で時間的にずらし、一方のテストパタンジェネレータによる一方のグループのライトの終了後、他方のテストパタンジェネレータによるテストシーケンスの実行を許可し、他方のテストパタンジェネレータから対応する他方のグループに対するライトのテストパタンを出力する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】バーンイン中のトグル率を向上させることにより、バーンイン後で行う検査において初期不良の検出率を上げる。

【解決手段】アプリケーション実行部20にアプリケーションを実行させる(第1工程)。続いて、当該アプリケーションによって動作しているアプリリソース40とアプリケーション実行部20との各動作状態のデータをRAM33に記憶する(第2工程)。次に、アプリケーション実行部20が実行していたアプリケーションと同一のアプリケーションをバーンイン実行部30に実行させ、同一のアプリケーションによって動作するアプリリソース40に対してバーンイン動作を行わせる(第3工程)。この後、RAM33に記憶したデータに基づいてアプリケーション実行部20およびアプリリソース40を元の動作状態に復帰させる(第4工程)。これら第1〜第4工程を複数のアプリケーション毎に繰り返す。

(もっと読む)

半導体テスト装置および半導体装置の製造方法

【課題】半導体装置のテスト用電源電圧として、複雑なパターンの電源波形を短時間で、高精度に生成する。

【解決手段】マルチプレクサ16から出力された電圧変化値ΔVは加算器17により電圧設定値保持部19に格納された電圧値が加算される。この加算結果は電圧設定値保持部19に格納される。加算回路20は加算器17の加算結果に、電圧初期値格納部18の初期値データを加算する。この加算結果は、補正器21が補正情報に基づいて補正する。制御回路26は比較器24の比較結果に基づいて補正器21のデジタルデータが上限/下限電圧になったかを判定し、到達していない場合、補正器21の信号を時間情報格納部25のデータ転送時間間隔ΔTに基づいて出力する。D/A変換器12は、その信号をアナログ信号に変換し、デバイス供給電源アナログ回路13に増幅されて電源電圧VCCとして出力される。

(もっと読む)

半導体回路

【課題】簡単な回路構成で故障検出のための試験を行うことができる半導体回路を提供する。

【解決手段】シフトレジスタを有しシリアル−パラレル変換を行う変換回路24の故障検出を行うための試験時に、シフトレジスタの初段のフリップフロップFF1AのD入力に、その/Q出力BS2Aを供給することで、クロック信号CLKのサイクル毎に0、1を交互に繰り返す信号を試験パターンとして生成し、この試験パターンを用いて変換回路24の試験を行うようにして、回路規模の大きな試験回路を搭載しなくとも、簡単な回路構成で故障検出のための試験を行えるようにする。

(もっと読む)

プリント基板試験装置

【課題】システムバスに接続された複数のプリント基板の試験を確実に行なうことを目的とする。

【解決手段】バウンダリスキャンテストソフトウェアを搭載しているコンピュータと、コンピュータの指示に基づいてJTAG信号を生成するJTAGコントローラと、ボードID判定とI/O制御を行なう第1の制御回路と、第1の制御回路によって制御される第1のI/Oバッファと、第1の制御回路に接続された第1のコネクタと、ボードID判定とI/O制御を行なう第2の制御回路と、第2の制御回路によって制御される第2のI/Oバッファと、第2の制御回路に接続された第2のコネクタと、JTAGバスと、システムバスと、システムバスを流れる信号をスキャンするシステムバススキャン回路と、を備えているプリント基板試験装置。システムバスとJTAGバスとシステムバススキャン回路はバックプレーンに実装されている。

(もっと読む)

半導体回路装置、半導体回路装置の測定方法

【課題】マイクロバンプに対応した測定用のパッドを有する半導体回路装置のアクセス時間tACの測定がより高精度に行えるようにする。

【解決手段】測定クロック生成回路200はメモリ部140の動作クロックCLK2のタイミングを変化させることで測定クロックCLK3を生成する。フリップフロップ154と排他的論理和ゲート155から成る部位は、比較結果信号XOR1として、出力データDoutの位相が測定クロックCLKに対して進んでいるときと遅れているときとで異なる値の信号を出力するように動作する。そこで、測定クロックCLK3のタイミングを変化させながら出力データDoutと測定クロックCLKの位相が一致するタイミングを特定し、アクセス時間tACを求める。

(もっと読む)

汎用プロトコルエンジン

一実施形態では、自動テスト装置用のプロトコルエンジン回路は、プロトコル固有データを取り込んで、被試験デバイスに対応して選択されたプロトコル定義を用いて、被試験デバイスのテストのためにプロトコル固有データをフォーマットするように構成された、プロトコル生成回路を含む。このプロトコル生成回路は、プロトコル定義テーブルから、選択されるプロトコル定義を取り込むように構成することができる。  (もっと読む)

(もっと読む)

半導体試験装置

【課題】テストヘッドとプローブカードとの間、或いはこれらを中継する中継部材との間を接離可能に構成した半導体試験装置において、光を用いた完全な非接触式の信号伝送を行うことで、半導体デバイスの試験を高速に且つ安定して行うことを目的とする。

【解決手段】半導体ウェハWに接触するプローブ針8を有するプローブカード5とこのプローブカード5に対して接離可能に設けられるテストヘッド2とを備える半導体試験装置であって、プローブカード5とテストヘッド2との間、およびパフォーマンスボード3との間で光空間伝送により信号伝送を行うために、光送信ユニット11、14、15、18と受光ユニット12、13、16、17とを備えている。

(もっと読む)

回路試験装置及び回路試験システム

【課題】集積回路間の相互接続性の検証に関わる工数及び費用を削減可能な回路試験装置等を提供する。

【解決手段】本開示の回路試験装置10は、2つの集積回路12、14の間の相互接続性を試験することができる。装置10は、出力側の集積回路14に所定の動作をさせるためのテストパターンデータを、入力側の集積回路12のデータバッファ16へ書き込むデータ書き込み部104と、入力側の集積回路12に、データバッファ16からテストパターンデータを読み出して、そのテストパターンデータを出力側の集積回路14へ供給するよう作動させるテスト制御信号を生成するテスト制御信号生成部106とを有する。

(もっと読む)

シリアル信号生成装置及びデバイス試験装置

【課題】受信デバイスの実動作周波数での試験を可能とするシリアル信号を生成するシリアル信号生成装置、及び当該シリアル信号を用いて受信デバイスの多種多様な試験を効率的に行うことができるデバイス試験装置を提供する。

【解決手段】デバイス試験装置1は、デバイスの試験を行う汎用の試験装置である試験装置本体10とシリアル信号を生成するシリアル信号生成装置20とを備えており、受信デバイスであるDUT40の試験を行う。シリアル信号生成装置20は、試験装置本体10から出力される試験データD1を記憶する送信制御部22と、ジッタ低減部21から出力されるクロック信号CK2に同期して送信制御部22から読み出される試験データD1を、クロック信号CK2の周波数と試験データD1のビット数とに応じたデータ転送速度を有するシリアル信号に変換する送信モジュール23とを備える。

(もっと読む)

再構成可能なテスターでのテストのための方法

いくつかの実装では、テスターで第一のタイプの試験下デバイスについての機能的動作環境をシミュレーションすることを含む、テストのための方法が提供される。これは、所定のプロトコルを有する不確定的応答信号を認識することと、第一のタイプの試験下デバイスから不確定的応答信号を受け取ることと、所定のプロトコルに基づいて不確定的応答信号から第一のタイプの試験下デバイスに転送すべき期待された刺激信号を確定することと、第一のタイプの試験下デバイスへの期待された刺激信号の送信を始動することとを含む。方法は更に、第一のタイプの試験下デバイスをテストした後に、テスターで第二のタイプの試験下デバイスについての機能的動作環境をシミュレーションすることを含む。  (もっと読む)

(もっと読む)

プロトコル認識デジタルチャネル装置

一実施形態では、試験下デバイスが機能的テストのためにその中に置かれる機能的動作環境をシミュレーションするプロトコル特定回路が提供される。プロトコル特定回路は、試験下デバイスによって通信された不確定的信号を受け取り、不確定的信号に応答してテスト刺激信号の試験下デバイスへの転送を制御するように構築されたプロトコル認識回路を含む。  (もっと読む)

(もっと読む)

RFソース・レシーバとその自己診断装置

【課題】RF信号を出力するRFソースと、RF信号を受信するRFレシーバで構成されるRFソース・レシーバを自己診断するために、ケーブルを用いてポートを繋ぎかえる手間が必要であり、また切り替えスイッチを制御する制御回路を具備した複雑な自己診断回路が必要であったという課題を解決する。

【解決手段】RFソース・レシーバのポートにパワーデバイダを接続し、使用しないRFソースに対応するポートは終端処理するようにした。RFソース・レシーバ側だけでループバックパスを切り換えることができ、かつ市販のパワーデバイダを用いることができるので、安価に自己診断ができる。

(もっと読む)

ドライバ回路

【課題】複雑な回路構成を必要とすることなく、伝送損失を受けた信号を模擬した模擬信号を可変的に生成し、DUTに内蔵された高域強調回路の正確な試験を実現することができるドライバ回路を提供する。

【解決手段】入力信号に応じて、伝送損失を受けた信号を模擬した模擬信号を出力するドライバ回路10において、入力信号が入力され、入力信号と同一波形の信号を出力信号として出力するメインドライバ18と、入力信号が入力され、入力信号を反転した波形の信号を出力信号として出力するサブドライバ20と、サブドライバ20の出力信号が入力され、サブドライバ20の出力信号の高域を強調した信号を出力信号として出力する高域強調回路22と、メインドライバ18の出力信号と高域強調回路22の出力信号とを加算した模擬信号を出力する加算回路24とを有している。

(もっと読む)

ICテストシステム及びIC試験方法

【課題】実際の使用状態と同じ環境で試験が行えるICテストシステム及びIC試験方法を実現することを目的にする。

【解決手段】本発明は、有機ELドライバを試験するICテストシステムに改良を加えたものである。本装置は、有機ELドライバの階調電流出力ピンに一端が電気的に接続される1以上の抵抗と、この抵抗の他端に、有機ELドライバの階調電流出力と同期し、有機ELドライバの期待電流出力に応じた電圧を与える電圧発生部とを備え、抵抗の一端の電圧により試験を行うことを特徴とする装置である。

(もっと読む)

検証装置および方法、プログラム、並びに記録媒体

【課題】ICチップの動作検証を、より効率的に行うことができるようにする。

【解決手段】PC220には、検証ツール221と、SAM制御ツール222が実装される。検証ツール221は、デフォルトデータ231およびスクリプトパラメータ232を利用してICチップ311の動作検証を行うテストスクリプト241を生成し、SAM271を稼動させるためにSAM設定スクリプト244を生成し、SAM制御ツール222に供給する。SAM制御ツール222は、テストスクリプト241に従って、SAM271から、ICチップ311へのコマンドなどのデータを、ドライバ251等を介して送信する。SAM制御ツール222が受信したICチップ311からの応答コマンドは、実行ログ243として検証ツール221により分析されて、ICチップ311が期待通りに動作したか否かが判定される。

(もっと読む)

テストシステム

【課題】ICテスタにより、TMDS信号を入力する被試験対象のダイナミック特性試験が行えるテストシステムを実現することを目的にする。

【解決手段】本発明は、ICテスタにより、TMDS信号を入力する被試験対象を試験するテストシステムに改良を加えたものである。本システムは、ICテスタのパラレル出力をシリアル信号に変換するパラレル/シリアル変換器と、このパラレル/シリアル変換器の出力を差動電流信号に変換し、被試験対象に出力する第1の差動電流ドライバとを備えたことを特徴とするシステムである。

(もっと読む)

テストパターン生成装置及びその方法

【課題】LSI機能をシミュレートさせるためのテストベンチが大規模複雑化し、これらをシミュレートするためのシミュレーション時間が増大する。

【解決手段】評価対象とするLSIチップ101を搭載する実機セットボード装置100でLSIチップ101を動作させ、そのLSI端子信号111〜116,124,125をプローブし、そのプローブ信号118〜123,127を任意のフォーマットのテストパターン170へ変換することで、簡便にかつ短時間でのテストパターン生成が可能となる。

(もっと読む)

1 - 20 / 32

[ Back to top ]