Fターム[2G132AE29]の内容

電子回路の試験 (32,879) | 試験装置(テストヘッドを除く) (4,743) | 小型チェッカー、ロジックチェッカー (5)

Fターム[2G132AE29]に分類される特許

1 - 5 / 5

評価基板

【課題】評価環境を簡易化し、評価の効率化を図ることができる評価基板を得る。

【解決手段】評価基板1はパワーモジュール2を評価するために用いられる。パワーモジュール2は、パワー半導体装置3と、パワー半導体装置3の特性を検出する温度検出部4及び電圧検出部5とを有する。評価基板1の1枚の基板7に、電源回路8、フォトカプラ駆動回路9、及び表示部10が設けられている。電源回路8はパワーモジュール2に電力を供給する。フォトカプラ駆動回路9はパワー半導体装置3を駆動する。表示部10は温度検出部4及び電圧検出部5から入力した検出信号を表示する。

(もっと読む)

ICチップ、半導体部品、検査用プローブ、ハンディマルチテスター、及び通信装置

【課題】TDR検査を安価な構成で実現できるICチップを得ること。

【解決手段】ICチップは、TDR(Time Domain Reflectometry)検査のためのICチップであって、クロック信号を生成するクロック生成部と、前記クロック信号をトリガとしてパルスを発生して検査対象へ出力するパルス発生部と、前記クロック信号を逓倍して逓倍クロック信号を生成する逓倍部と、前記逓倍クロック信号に同期して、前記検査対象からの反射信号をA/D変換して反射データとしてサンプリングするA/Dコンバータと、前記サンプリングされた反射データを記憶するメモリと、外部から読み出しコマンドを受け、前記読み出しコマンドに応じて前記メモリに記憶された反射データを外部に出力する通信制御部とを備えている。

(もっと読む)

基板検査装置および画像処理装置

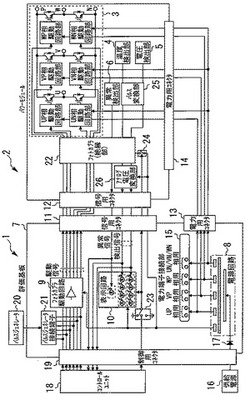

【課題】検査プログラムと製品プログラムを別々に記憶することにより、検査プログラムによる効率のよい検査を可能としながら、製品プログラムに対する検査も行えるようにする。

【解決手段】基板検査装置(基板チェッカ)20は、検査プログラムを記憶した検査用メモリ32を備える。基板チェッカ24に接続される検査対象基板20は、製品プログラムを記憶した製品用メモリ31を備える。基板チェッカ24の検査制御部33は、検査時に検査対象基板20のCPU23と製品用メモリ31とを結ぶラインを遮断し、CPU23と検査用メモリ32とを結ぶラインを形成する。検査対象基板20において動作するプログラムが製品プログラムから検査プログラムに切り替わり、検査プログラムによる基板の検査が行われる。

(もっと読む)

JTAGテストシステム

【課題】シリアルデータをパラレルデータに変換することによりトレース量がそれほど多くないロジックアナライザなどのテストデータ収集部でも十分なデータを収集できるようにするとともに、トレースデータの解析の一部をデータ収集中にリアルタイムで行うことにより、最終的な解析時間を大幅に短縮できるJTAGテストシステムを提供すること。

【解決手段】TAPコントローラとクロックに同期してテストデータ収集を行うテストデータ収集部とJTAG解析ソフトウェア処理実行部とを含むJTAGテストシステムであって、TAPコントローラとテストデータ収集部の間に、TAPステート解析をリアルタイムで実行するTAPステート解析処理部を設けたことを特徴とするもの。

(もっと読む)

信号波形測定装置、信号波形測定システム及びサンプリングタイミング信号発生器

【課題】チップ内部の多観測点における波形を高速かつ高精度に取得できる信号波形測定装置を提供する。

【解決手段】ICチップ上に設けられ、その上の複数の検出点の信号波形を測定するマルチチャンネルの信号波形測定装置102が提供される。複数の信号検出フロントエンド回路30は複数の検出点33に対応して設けられ、イネーブルタイミング信号に基づいて各検出点の電圧を緩衝増幅した後、緩衝増幅した電圧を各参照電圧と比較してその比較結果を2値デジタル出力信号にデジタル化して出力する。マルチプレクサ36は各信号検出フロントエンド回路30からの2値デジタル出力信号を時分割多重化して多重化デジタル出力信号を出力する。データ処理ユニット40はマルチプレクサ36から出力される多重化した2値デジタル出力信号の所定値の数を計数することにより上記検出された各検出点33の検出電圧についての判定出力確率を算出して出力する。

(もっと読む)

1 - 5 / 5

[ Back to top ]