株式会社半導体理工学研究センターにより出願された特許

1 - 10 / 150

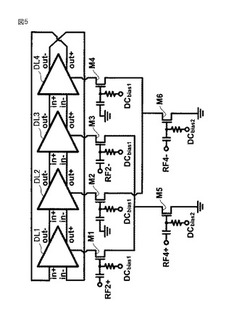

分周回路およびPLL回路

【課題】2分周、8分周、さらには8分周可能な回路規模の小さな低消費電力の注入同期型分周回路の実現。

【解決手段】偶数個Mの遅延要素DL1-DL4を有するリングオシレータ11と、入力発振信号から同期信号を生成して複数個の遅延要素の少なくとも一部に注入する同期信号注入回路と、を有し、入力発振信号の分周信号を出力する分周回路であって、遅延要素のオン・オフする分周トランジスタの一方の被制御端子が注入ノードであり、同期信号注入回路は、M/2個離れた2つの遅延要素の注入ノードに接続されるように並列に設けられた2個の補助注入トランジスタを有する注入差動対M1-M4と、入力発振信号RF4+,RF4-が制御端子に入力され、注入差動対の注入ノードとの接続ノードに、入力発振信号の差動信号を発生するように注入差動対に接続された信号注入トランジスタM5,M6と、を有する分周回路。

(もっと読む)

時間差増幅回路

【課題】時間差増幅回路の時間差オフセットを低減する。

【解決手段】複数の時間差増幅器が多段接続された時間差増幅回路100であって、複数の時間差増幅器は、第1の正入力端子1a、第1の負入力端子1b、第1の正出力端子1c及び第1の負出力端子1dを有する第1の時間差増幅器TDA1と、第2の正入力端子2a、第2の負入力端子2b、第2の正出力端子2c及び第2の負出力端子2dを有し、第1の時間差増幅器の出力信号が入力される第2の時間差増幅器TDA2と、第2の正入力端子2aに第1又は第4の配線I1,I2を接続させる第1の選択素子S1と、第2の負入力端子2bに第2又は第3の配線I2、I3を接続させる第2の選択素子S2を有する選択回路10aと、選択回路10aを制御する制御回路50を具備する。

(もっと読む)

スタティックランダムアクセスメモリセルの電圧特性調整方法。

【課題】より簡易な方法でスタティックランダムアクセスメモリセルの電圧特性を向上する。

【解決手段】スタティックランダムアクセスメモリセルにおいて、電源電圧印加点と一方のビット線との間の電圧差を通常の電圧差V1より高い電圧差V1hとすると共にワード線と一方のビット線との間の電圧差をパスゲートトランジスタの閾値電圧より若干高い電圧差Vwdとして、一方のビット線に接続されているパスゲートトランジスタのソース,ドレインとなる拡散層のうちメモリセルを構成するインバータの出力端子に接続されているほうの拡散層近傍の絶縁層へエレクトロンを注入する(ステップS110)。これにより、より簡易な方法でメモリセルの電圧特性の向上を図ることができる。

(もっと読む)

抵抗変化型メモリ

【課題】従来技術に比較して高い再現性で確実に抵抗のヒステリシス特性及びメモリ特性を発現させることができる抵抗変化型メモリとその製造方法を提供する。

【解決手段】PrxCa1−xMnO3にてなるPCMO層を下部電極と上部電極とにより挟設してなる抵抗変化型メモリにおいて、上記PCMO層と上記上部電極もしくは下部電極との間に金属酸化物層を挿入形成した。ここで、上記金属酸化物は上記上部電極の金属の酸化物であり、上記上部電極と下部電極の少なくとも一方はタングステン(W)、モリブデン(Mo)、クロム(Cr)、アルミニウム(Al)、銀(Ag)のうちのいずれかにてなる。上記抵抗変化型メモリは、正の直流電圧領域において、上記第1の低抵抗状態と上記第1の高抵抗状態の2値を有するとともに、負の直流電圧領域において、上記第2の高抵抗状態と上記第2の低抵抗状態の2値を有することにより、合計4値の情報を記憶する。

(もっと読む)

昇圧回路

【課題】損失を抑制すると共により迅速に昇圧を行なう。

【解決手段】チャージポンプ20からの出力電圧VCがトリガ電圧を超えると、スイッチ70がオンし、クロック信号供給回路30は出力電圧VCの振幅のクロック信号CKmos,CKBmosをチャージポンプ20に出力し、クロック信号供給回路40は出力電圧VCの振幅のクロック信号CKmosを用いてクロック信号CKcap,CKBcapを生成してチャージポンプ20に出力し、チャージポンプ20では、各トランジスタのゲートへ出力電圧VCの振幅のクロック信号CKmos,CKBmosが供給され、各キャパシタの他端へ立ち上がり時間の小さいクロック信号CKcap,CKBcapが供給される。これにより、昇圧回路10全体の損失を抑制すると共により迅速に出力電圧VCを目標出力電圧に昇圧することができる。

(もっと読む)

半導体装置

【課題】少しの設計方法の変更で設計できる、一層低消費電力化した半導体装置の実現。

【解決手段】複数の電源供給領域23と、複数の電源供給領域に供給する電源の電圧を切り替える複数の電源切替ユニットSWA,SWBと、を有し、複数の電源供給領域に含まれる回路要素を組み合わせて少なくとも1つの機能ブロックが形成され、少なくとも1つの機能ブロックは、内部に異なる電圧で動作する回路要素を含む半導体装置。

(もっと読む)

パイプライン型A/D変換回路

【課題】セットリング誤差を線形化でき、高速で消費電力の小さいパイプライン型A/D変換回路を提供する。

【解決手段】パイプライン型A/D変換回路において、各段のA/D変換回路部に、複数の比較器を含み、入力信号をA/D変換するサブA/D変換回路と、サブA/D変換回路からのデジタル信号を、正負の参照電圧を基準値として用いて生成したアナログ制御信号にD/A変換し、アナログ制御信号に基づき、入力信号を、複数のサンプリングキャパシタを用いてサンプリングし、ホールドし、増幅してD/A変換する乗算型D/A変換回路と、後段側の乗算型D/A変換回路でサンプリングをする前に、後段側のサンプリングキャパシタを、サブA/D変換回路に含まれる複数の比較器の出力する比較結果信号に応じて、正負の参照電圧の中間電圧値に予め充電するプリチャージ回路と、を設け、セットリング誤差を線形化する。

(もっと読む)

弛張発振回路

【課題】従来技術に比較して周波数が一定のクロックを発生できる弛張発振回路を提供する。

【解決手段】クロック発生サブ回路1は、基準電圧Vrefとコンパレータ14の誤差電圧ΔV1とを含む比較電圧Vcmp1を発生して出力電圧Vsub1としてコンパレータ14の反転入力端子に出力する比較電圧発生期間と、電流電圧変換回路11からの出力電圧Vc1を比較電圧Vcmp1と比較するクロック発生期間とを交互で繰り返すように制御される。クロック発生サブ回路2も、クロック発生サブ回路1と同様のクロック発生期間とを交互で繰り返すように制御される。制御回路5は、クロック発生サブ回路1及び2を、一方の回路が比較電圧発生期間であるときに他方の回路がクロック発生期間であるように制御する。

(もっと読む)

センサネットワークシステムとその通信方法

【課題】センサネットワークシステムにおいてデータ集約を効率的に行うことができ、ネットワークトラフィックを大幅に削減する。

【解決手段】既知の位置情報を有する複数のノードが相互に伝搬経路を介するネットワーク上で接続されかつ時間同期されたセンサネットワークシステムを用いて、各ノードで測定されたデータを1つの基地局に集約するように収集するセンサネットワークシステムにおいて、基地局は各ノードからの信号の角度推定値と各ノードの位置情報とに基づいて、信号源の位置を計算し、信号源に最も近いノードをクラスタヘッドノードに指定し、信号源の位置とクラスタヘッドノードの情報とを各ノードに送信して各クラスタヘッドノードからホップ数内に位置する各ノードを各クラスタに所属するノードとしてクラスタリングし、指定されたクラスタに属する各ノード毎に、センサアレイで受信した信号に対して強調処理して基地局に送信する。

(もっと読む)

ラマン散乱による結晶内部応力または表面応力の測定法

【課題】Si基板の内部応力または表面応力の測定方法において、結晶基板に導入された応力の立体成分についても測定可能な技術を提供する。

【解決手段】結晶基板の応力測定方法であって、前記結晶基板に、その結晶基板に垂直な方向の偏光を含むレーザー光を照射するステップと、前記レーザー光を照射した前記結晶基板から出射する散乱光を分光して、その散乱光に含まれるラマン散乱光の波数シフトΔω1とΔω2とΔω3とのうち二つ以上とを計測するステップと、計測した波数シフトΔω1とΔω2とΔω3とのうち二つ以上と、前記結晶基板の種類によって定まる係数a及びbとから、前記結晶基板の応力の立体成分σxx、σyy、σzzのうち二つ以上を算出するステップと、を含む。

(もっと読む)

1 - 10 / 150

[ Back to top ]