Fターム[4E351BB32]の内容

プリント基板への印刷部品(厚膜薄膜部品) (19,111) | 印刷電気部品の種類と構造 (5,073) | 構造一般 (3,045) | 印刷層の形態 (2,419) | 薄膜 (122)

Fターム[4E351BB32]に分類される特許

121 - 122 / 122

プリント配線板

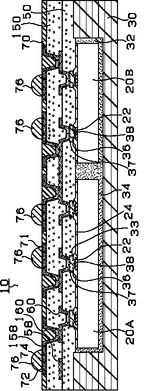

【課題】 リード部品を介さないで、ICチップと直接電気的接続し得る多層プリント配線板を提案する。

【解決手段】 多層プリント配線板は、コア基板30にICチップ(CPU)20A及びICチップ(キャッシュメモリ)20Bを予め内蔵させて、該ICチップ20A、20Bのダイパッド24には、トラジション層38を配設させている。このため、リード部品や封止樹脂を用いず、ICチップと多層プリント配線板との電気的接続を取ることができる。また、アルミダイパッド24上にトラジション層38を設けることで、ダイパッド24上の樹脂残りを防ぐことができ、ダイパッド24とバイアホール60との接続性や信頼性を向上させる。また、複数のICチップを内蔵させることで、高集積化を達成できる。

(もっと読む)

高周波モジュール装置及びその製造方法

【課題】 高精度、高機能で薄型化され、パッケージの小型化、低価格を図るようにする。

【解決手段】 耐熱特性や高周波特性を有する有機基材により成形したコア基材5の第1の主面5a上にパターン配線層6を形成するとともに最上層に平坦化処理を施して高周波素子層形成面3を形成してなるベース基板部2と、高周波素子層形成面3上に、薄膜技術或いは厚膜技術によって形成され、誘電絶縁層30を介してベース基板部2側から電源或いは信号の供給を受ける抵抗体27、キャパシタ26からなる受動素子を層内に構成した高周波素子層部4とからなる。

(もっと読む)

121 - 122 / 122

[ Back to top ]