Fターム[4M104BB22]の内容

半導体の電極 (138,591) | 電極材料 (41,517) | 遷移金属のシリサイド (5,826) | PtSi (542)

Fターム[4M104BB22]に分類される特許

541 - 542 / 542

接点の製作方法とその接点を持つ電子部品

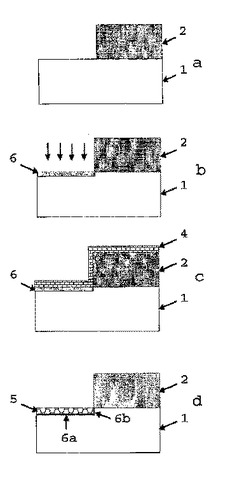

この発明は、ケイ化物(5)などの第一の層とそれに隣接する層との間に、不活性化した境界面(6a,6b)を製作する方法に関する。この方法の間には、S、Se、Teなどの不活性化元素を、この層構造の中に組み入れるとともに、温度処理の間に、少なくとも第一の層の隣接層との境界面において濃縮させる。こうすることによって、ショットキー障壁を低下させるとともに、遷移域の仕事関数を調節すことに成功した。例えば、ソース接点とドレイン接点の両方又は一方のショットキー障壁が低い又はそれどころか負であるショットキー障壁MOSFETとスピントランジスターの素子を開示している。  (もっと読む)

(もっと読む)

半導体デバイスおよびその製造方法

集積回路での使用に適した歪み半導体デバイスおよび歪み半導体デバイスの製造方法。半導体−オン−インシュレータ基板からメサ分離構造が形成される。このメサ分離構造にゲート構造が形成される。このゲート構造は、ゲート絶縁材料に配置されたゲートと、対向する2組の側壁を有する。ゲート構造の対向する第1の組の側壁に隣接するメサ分離構造の一部に、半導体材料が選択的に成長され、ドープが行われる。ドープされた半導体材料がシリサイド化されて、絶縁材料によって保護される。ゲートがシリサイド化され、このシリサイドが、対向する第2の組の側壁を覆っており、チャネル領域に応力を付与する。  (もっと読む)

(もっと読む)

541 - 542 / 542

[ Back to top ]