Fターム[4M104FF24]の内容

半導体の電極 (138,591) | 構造 (12,435) | コンタクトホールの孔埋め構造 (1,175) | 2以上の物質で孔埋め (943) | 側面のみ他物質で処理 (58) | 他物質がポリシリコン (6)

Fターム[4M104FF24]に分類される特許

1 - 6 / 6

基板貫通バイアを有する半導体構造および製造方法

【課題】基板を貫通するバイアホールを与える。

【解決手段】半導体デバイス構造は、第1の濃度および第1の導電型のバックグラウンドドーピングを有する基板を含んでなる。基板貫通バイアは基板を貫通している。デバイスは基板の第1の面上に第2の導電型の第1のドープ領域を有する。第2のドープ領域が基板貫通バイアの周りにある。第2のドープ領域は、第1の濃度よりも大きい第2の濃度にドーピングされており、第1の導電型を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチパワーDMOSトランジスタにおいて、ソース引き出し電極とゲート引き出し電極の短絡を確実に防止する。併せて上記DMOSトランジスタのサイズの縮小を図ること及びソース・ドレイン間絶縁破壊電圧VDSの低下を防止する。

【解決手段】N+型ソース層13の底面の直下のP型ベース層9内に形成されたP+型コンタクト層14を、コンタクト用開口25の内の少なくとも一部の該コンタクト用開口25の底面に露出するN+型ソース層13を貫通するくぼみ部16に露出させる。次にコンタクト用開口25の底面に露出するN+型ソース層13及びくぼみ部16に露出するN+型ソース層13、P+型コンタクト層14に接続し、コンタクト用開口25内をその上端まで埋設して延在するソース引き出し電極17aを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセルトランジスタのコンタクト抵抗を低減する。

【解決手段】半導体装置70には、半導体基板1上に複数の絶縁ゲート型電界効果トランジスタが設けられる。絶縁ゲート型電界効果トランジスタのゲートの間に形成され、側面が側壁絶縁膜8及び絶縁膜9により絶縁ゲート型電界効果トランジスタのゲートと分離された自己整合コンタクト開口部の底部には凹部形状のポリシリコンプラグ11が設けられる。ポリシリコンプラグ11上にはバリアメタル膜12が設けられる。バリアメタル膜12上には、自己整合コンタクト開口部を覆うように金属プラグ13が埋設される。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクトホール下部において、シリコン基板へのメタルの拡散を防ぎ、メタルの侵入による消費電流の増大を無くした半導体装置を提供する。

【解決手段】層間絶縁膜103に形成されたコンタクトホール104の側壁部にポリシリコン層105を設ける。この上にチタン106とチタン窒化膜107からなるバリア膜、アルミニウム合金108を形成する。これによって、チタン窒化膜が薄くなった部分からアルミニウムがシリコン基板101の高不純物ドープ活性領域102へ侵入するのを防止する。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクトホール内に形成される配線層の抵抗値を抑制する。

【解決手段】コンタクトホールHが、変曲位置H1から下方に向けて径が小さいテーパ孔形状に形成されていると共に変曲位置H1から上方に向けてシリコン基板2の表面に対して垂直柱状に形成されている。また、このコンタクトホールH内にポリプラグ8および金属プラグ9が形成されている。

(もっと読む)

半導体装置

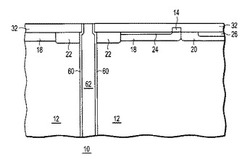

【課題】メモリセルと周辺回路を備えた半導体装置において、周辺回路領域にキャパシタを、マスク工程を増加させることなく形成する。

【解決手段】

メモリセルと周辺回路を備えた半導体装置において、前記周辺回路領域に形成されるキャパシタは、前記メモリセル領域のゲート電極と同時に形成される下部電極と、前記メモリセル領域において前記コンタクトホール内壁面を覆う絶縁膜と同時に形成される容量絶縁膜と、前記コンタクトホールに形成されるコンタクトプラグと同時に形成される上部電極とを備える。

(もっと読む)

1 - 6 / 6

[ Back to top ]