Fターム[4M119DD23]の内容

MRAM・スピンメモリ技術 (17,699) | セル構成 (5,615) | 記憶素子 (3,263) | 記憶素子の平面形状 (699) | 十字型 (27)

Fターム[4M119DD23]に分類される特許

1 - 20 / 27

磁気記憶素子および磁気記憶装置

【課題】半選択状態になった磁気記憶素子のデータの誤反転を抑制することにより信頼性の高い書き込み動作を行うことができる磁気記憶素子、およびこれを用いた磁気記憶装置を提供する。

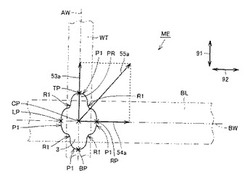

【解決手段】磁化容易軸91と磁化困難軸92とを有する記録層3は、平面視においてすべての領域が第1導電層WTまたは第2導電層BLの少なくとも一方と重なる。磁化容易軸91に沿い、記録層3と平面視において重なる寸法が最大となる第1の線分の第1の端点TP,BPは、第2導電層BLと平面視において重ならない。上記第1の線分の中点を通り、平面視において第1の線分に直交し、記録層3と平面視において重なる第2の線分の1対の端点である第2の端点LP,RPのうち少なくとも一方は、第1導電層WTと平面視において重ならない。

(もっと読む)

磁気ランダムアクセスメモリ及びその製造方法

【課題】 書き込み電流の低減を図る。

【解決手段】 実施形態による磁気ランダムアクセスメモリは、メモリセルに磁気抵抗素子100を備えた磁気ランダムアクセスメモリであって、磁気抵抗素子100は、第1の金属磁性層24と、第2の金属磁性層26と、第1及び第2の金属磁性層24、26に挟まれた絶縁層25と、を具備し、第1及び第2の金属磁性層24、26の各面積は、絶縁層25の面積より小さい。

(もっと読む)

磁気抵抗効果素子のデータ書き込み方法及び磁気ランダムアクセスメモリ

【課題】誤書き込みの発生が少ない、安定したスピン注入磁化反転によるデータ書き込みを実現する。

【解決手段】本発明の実施形態に係る磁気抵抗効果素子のデータ書き込み方法は、磁化方向が不変な第1の磁性層と、磁化方向が可変な第2の磁性層と、前記第1の磁性層と前記第2の磁性層の間に設けられたトンネルバリア層とを有する磁気抵抗効果素子のデータの書き込み方法であって、電流の立ち下がり期間Tfが、電流の立ち上がり期間よりも長い書き込み電流Iwを、磁気抵抗効果素子に流して、第1の磁性層の磁化方向と第2の磁性層の磁化方向との関係を変化させる。

(もっと読む)

磁気抵抗効果素子のデータ書き込み方法及び磁気ランダムアクセスメモリ

【課題】実効的な書き込み電流の低減及び書き込み時間の短縮を実現する。

【解決手段】本発明の例に係る磁気抵抗効果素子のデータ書き込み方法は、磁化方向が不変な第1の磁性層と、磁化方向が可変な第2の磁性層と、第1の磁性層と第2の磁性層の間に設けられたトンネルバリア層とを有する磁気抵抗効果素子のデータの書き込み方法であって、パルス形状の書き込み電流Iwを磁気抵抗効果素子に流して、第1の磁性層の磁化方向と第2の磁性層の磁化方向との関係を変化させることを具備し、書き込み電流Iwのパルス幅WPは、その電流の立ち上がりの開始から第1の時間tosまでの第1の期間W1と、第1の期間W1に続く第2の期間W2とを含み、書き込み電流Iwは、第2の期間W2内に出力される電流値i1と、第1の期間W1内に出力され電流値i1より大きい電流値i2とを含んでいる。

(もっと読む)

半導体メモリ

【課題】半導体装置のプロセスマージンを向上できる。

【解決手段】本発明の例の半導体メモリは、同一の配線層内に設けられる2つのビット線BL1,BL2と、メモリセルアレイ内に設けられるアクティブ領域AA2と、アクティブ領域AA2と交差する2つのワード線WL1,WL2と、ゲートがワード線WL1,WL2にそれぞれ接続されアクティブ領域AA2上に設けられる第1及び第2のトランジスタTr1,Tr2と、ビット線BL2とトランジスタTr1のソース/ドレインとに接続される第1の抵抗性記憶素子MTJ1と、ビット線BL2とトランジスタTr2のソース/ドレインとに接続される第2の抵抗性記憶素子MTJ2と、ビット線BL1と2つのトランジスタTr1,Tr2の共有ノードに接続され、ワード線WL1,WL2間に配置される配線層M2とを具備し、アクティブ領域AA2はメモリセルアレイの一端から他端まで延在する。

(もっと読む)

磁気ランダムアクセスメモリ及びその書き込み方法

【課題】コストの増加を抑制しつつ、磁化反転をアシストする。

【解決手段】スピン注入型の磁気ランダムアクセスメモリは、固定層11と記録層13と非磁性層12とを有し、固定層及び記録層の磁化は膜面に対して垂直方向を向く磁気抵抗効果素子10aと、磁気抵抗効果素子の一端に接続されたソース線SLaと、磁気抵抗効果素子の他端に電流経路の一端が接続されたトランジスタTraと、トランジスタの電流経路の他端に接続され、ソース線と平行に延在されたビット線BLと、磁気抵抗効果素子及びトランジスタを介してビット線及びソース線間に書き込み電流Iを流し、ビット線を通過した書き込み電流によって発生された磁場の磁気抵抗効果素子に対する印加方向が磁気抵抗効果素子を通過する書き込み電流の方向と反対であるソース/シンカとを具備する。

(もっと読む)

データストレージデバイスおよびデータストレージ方法

各データ担持ナノワイヤが、そのナノワイヤの全長に沿って複数の交差するナノワイヤを有して、磁壁ピン留めサイトを構成する交差接合部を形成する。データは、交差するナノワイヤとの整列と反整列の間で交番する磁界の作用の下で磁区を動かすことによって、各データ担持ナノワイヤを通って送られる。データは、上向きキラリティ横磁壁および下向きキラリティ横磁壁が、0および1を符号化するのに使用されて、磁壁のキラリティに符号化される。データは、事前定義されたキラリティの磁壁を有する磁区を核形成することができる適切な核形成磁界発生器を使用して、各ナノワイヤの中にクロック制御されて入れられる。データは、このキラリティを検知する適切な磁界センサを使用して、各ナノワイヤからクロック制御されて出される。  (もっと読む)

(もっと読む)

ホール効果装置及びその動作方法

【課題】 強磁性体構成要素を含む改良されたホール効果素子であって、例えば、ディジタルの組合わせ可能なタスクを実行する論理応用例や、磁界センサ等においてディジタル情報の不揮発性記憶装置用のメモリ素子として使用可能なホール効果素子を提供する。

【解決手段】 ホール・プレート520の一部を覆って該ホール・プレート520から電気的に絶縁されている強磁性体層510を含む。ホール・プレート520上のこの強磁性体層510は、外部的に印加された磁界によって変更可能であり、この素子がメモリ要素として用いられると、当該素子が2つの異なるデータ値(0或いは1)に対応し得る2つの安定磁化状態(正及び負)を異方性軸に沿って有することを可能としている。

(もっと読む)

磁気ランダムアクセスメモリ及びその製造方法

【課題】セル面積を縮小する。

【解決手段】磁気ランダムアクセスメモリは、側面と上面とを有する段差部が形成された半導体基板11と、段差部の側面上にゲート絶縁膜20を介して形成されたゲート電極Gと、段差部の上面内に形成されたドレイン拡散層24と、ドレイン拡散層より下方の半導体基板内にドレイン拡散層と離間して形成されたソース拡散層18と、ドレイン拡散層に接続され、磁化方向が固定された固定層31と磁化方向が反転可能な記録層33と固定層及び記録層の間に設けられた非磁性層32とを有し、固定層及び記録層の間に流す電流の向きに応じて固定層及び記録層の磁化方向が平行状態又は反平行状態となる磁気抵抗効果素子MTJと、磁気抵抗効果素子に接続されたビット線BLを具備する。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】高温処理を行った場合でも素子の信頼性の劣化を抑制する。

【解決手段】磁気ランダムアクセスメモリは、磁化方向が固定された固定層11と磁化方向が反転可能な記録層13と固定層及び記録層の間に設けられた非磁性層12とを有する磁気抵抗効果素子MTJを具備するメモリセルアレイであって、磁気抵抗効果素子の下方に配置された前記メモリセルアレイ内の全ての導電層2、4、5は、W、Mo、Ta、Ti、Zr、Nb、Cr、Hf、V、Co、Niからなる群の中から選択された元素を含む材料で形成されている。

(もっと読む)

磁気ランダムアクセスメモリ及びその書き込み方法

【課題】磁気抵抗効果素子の加工ばらつきを抑制する。

【解決手段】磁気ランダムアクセスメモリは、第1の方向に延在された第1及び第2のビット線BL1、BL2と、第1のビット線に接続され、磁化方向が固定された第1の固定層と磁化方向が反転可能な第1の記録層と第1の固定層及び第1の記録層の間に設けられた第1の非磁性層とを有し、第1の固定層及び第1の記録層の間に流す第1の電流の向きに応じて第1の固定層及び第1の記録層の磁化方向が平行状態又は反平行状態となる第1の磁気抵抗効果素子MTJ1と、第2のビット線に接続され、磁化方向が固定された第2の固定層と磁化方向が反転可能な第2の記録層と第2の固定層及び第2の記録層の間に設けられた第2の非磁性層とを有し、第1及び第2の記録層は同じ第1の層13で形成され、第2の固定層及び第2の記録層の間に流す第2の電流の向きに応じて第2の固定層及び第2の記録層の磁化方向が平行状態又は反平行状態となる第2の磁気抵抗効果素子MTJ2とを具備する。

(もっと読む)

半導体記憶装置及びそのデータ書き込み/読み出し方法

【課題】1ビットあたりのメモリセル面積を縮小する。

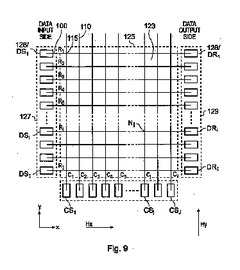

【解決手段】半導体記憶装置は、メモリセルMCを構成する第1乃至第3の抵抗性記憶素子MTJ1、MTJ2、MTJ3と、第1のソース/ドレイン電極が第1の抵抗性記憶素子の一端に接続され、第2のソース/ドレイン電極が第3の抵抗性記憶素子の一端に接続された第1のトランジスタTr1と、第3のソース/ドレイン電極が第2の抵抗性記憶素子の一端に接続され、第4のソース/ドレイン電極が第3の抵抗性記憶素子の一端に接続された第2のトランジスタTr2と、第3の抵抗性記憶素子の他端に接続された第1のビット線BL1と、第1及び第2の抵抗性記憶素子の他端に接続された第2のビット線BL2と、第1のトランジスタのゲート電極に接続された第1のワード線WL1と、第2のトランジスタのゲート電極に接続された第2のワード線WL2とを具備する。

(もっと読む)

磁気ランダムアクセスメモリ及びその書き込み方法

【課題】セルの高集積化を図ることが可能な磁気ランダムアクセスメモリ及びその書き込み方法を提供する。

【解決手段】磁気ランダムアクセスメモリは、第1の方向に延在された第1の配線BLと、第1の方向と交差する第2の方向に延在された第2の配線WLと、第1及び第2の配線間の第1及び第2の配線の交点に配置され、第1の配線に接続された一端を有し、固定層と記録層と固定層及び記録層の間に設けられた非磁性層とを有し、固定層の膜厚は記録層の膜厚よりも厚く、固定層の幅は記録層の幅より広く、固定層及び記録層の間に第1の電流を流すことで記録層の磁化方向が反転する磁気抵抗効果素子MTJと、磁気抵抗効果素子の他端に接続された一端と第2の配線に接続された他端とを有し、第1の電流を一方向のみに流すダイオードDとを具備する。

(もっと読む)

半導体記憶装置

【課題】メモリセル面積を増大することなく、プロセスコストの低減とチップ作成工期の短縮を図る。

【解決手段】半導体記憶装置は、同一配線層で形成された第1及び第2のビット線BL1、BL2と、第1及び第2のビット線と交差する第1及び第2のワード線WL1、WL2と、第1のワード線を挟んでBL2下に配置された第1及び第2のソース/ドレイン拡散層S/D1、S/D2を有する第1のトランジスタTr1と、第2のワード線を挟んでBL2下に配置された第2及び第3のソース/ドレイン拡散層S/D2、S/D3を有し、第2のソース/ドレイン拡散層が第1のビット線に接続された第2のトランジスタTr2と、両端が第2のビット線及び第1のソース/ドレイン拡散層にそれぞれ接続された第1の抵抗性記憶素子MTJ1と、両端が第2のビット線及び第3のソース/ドレイン拡散層にそれぞれ接続された第2の抵抗性記憶素子MTJ2とを具備する。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】セルサイズを縮小することを可能とする。

【解決手段】磁気ランダムアクセスメモリは、第1及び第2のビット線BLと、第1及び第2のビット線を有するグループGPに対して1つ設けられ、第1のビット線と隣り合い、第1及び第2のビット線と同じ第1の方向に延在されたソース線SLと、第1のビット線に接続された第1の磁気抵抗効果素子MTJaと、第2のビット線に接続された第2の磁気抵抗効果素子MTJcと、第1の磁気抵抗効果素子と直列接続された第1のトランジスタTraと、第2の磁気抵抗効果素子と直列接続された第2のトランジスタTrcとを具備し、第1の磁気抵抗効果素子と第1のトランジスタとを有する第1のセルと第2の磁気抵抗効果素子と第2のトランジスタとを有する第2のセルがソース線に共通接続されている。

(もっと読む)

磁気ランダムアクセスメモリ及びその書き込み方法

【課題】書き込み特性を向上する。

【解決手段】磁気ランダムアクセスメモリは、磁化方向が固定された固定層と第1の閾値に基づいて磁化方向が反転可能な記録層と固定層及び記録層の間に設けられた非磁性層とを有し、固定層及び記録層の間に流す電流の向きに応じて固定層及び記録層の磁化方向が平行状態又は反平行状態となるメモリセル素子MTJmと、メモリセル素子の一端に接続された第1の配線BLと、電流経路の一端がメモリセル素子の他端に接続されたトランジスタTrと、電流経路の他端に接続された第2の配線SLと、メモリセル素子に電気的に接続され、第1の閾値と異なる第2の閾値に基づいて抵抗値が変化する抵抗変化素子AFとを具備する。

(もっと読む)

半導体記憶装置

【課題】メモリセルの高密度化を図れるMRAMやPRAM等の半導体記憶装置を提供する。

【解決手段】間隔を有して順に配置され、膜面に対して垂直方向に電流を流すことで記録が行われる第1乃至第4の抵抗変化素子MTJ1〜MTJ4と、第1及び第2の抵抗変化素子を接続する第1の電極15と、第3及び第4の抵抗変化素子を接続する第2の電極15と、第2及び第3の抵抗変化素子を接続するビット線BL2と、抵抗変化素子と対をなし、第1及び第2の電極と離間して配置されたワード線WL1〜WL4と、第1乃至第4の抵抗変化素子の中の選択素子にデータを書き込む時、第1乃至第4の抵抗変化素子と第1及び第2の電極とビット線とを有するチェーン構造部に第1の電流Iw1を流す第1の電流源と、選択素子にデータを書き込む時、選択素子に対応する第1乃至第4のワード線の中の選択ワード線に第2の電流Iw2を流す第2の電流源とを具備する。

(もっと読む)

磁気ランダムアクセスメモリの製造方法

【課題】層間膜のアウトガスから磁気抵抗効果素子を保護し、磁気特性の劣化を抑制する。

【解決手段】磁気ランダムアクセスメモリの製造方法は、磁気抵抗効果素子23となる材料層を形成する工程と、材料層の少なくとも一部を加工し、磁気抵抗効果素子23を形成する工程と、材料層の少なくとも一部を加工した装置内において、真空一貫状態で、磁気抵抗効果素子23の側面を覆う保護膜24を形成する工程と具備する。

(もっと読む)

磁気ランダムアクセスメモリ及びその製造方法

【課題】スピン注入磁化反転型の磁気抵抗効果素子に流す書き込み電流を低減する。

【解決手段】磁気ランダムアクセスメモリは、磁化方向が固定された固定層11と磁化方向が反転可能な記録層13と固定層及び記録層の間に設けられた非磁性層12とを有し、固定層及び記録層の間に流す電流の向きに応じて固定層及び記録層の前記磁化方向が平行状態又は反平行状態となる磁気抵抗効果素子MTJと、記録層に接続され、記録層との接触面積が記録層の面積よりも小さいコンタクト30と、コンタクトと記録層との間に設けられ、記録層の抵抗よりも高い抵抗を有するキャップ層20とを具備する。

(もっと読む)

磁気ランダムアクセスメモリ及びその製造方法

【課題】磁気抵抗効果素子の磁性特性の劣化を抑制する。

【解決手段】磁気ランダムアクセスメモリは、コンタクトホール21を有する層間絶縁膜20と、コンタクトホール内に形成されたコンタクト23と、コンタクトの上面上に形成され、コンタクトホール内に埋め込まれたバリアメタル膜25と、一端がバリアメタル膜と接続され、磁化方向が固定された固定層11と磁化方向が反転可能な記録層13と固定層及び記録層の間に設けられた非磁性層12とを有し、固定層及び記録層の間に流す電流の向きに応じて固定層及び記録層の磁化方向が平行状態又は反平行状態となる磁気抵抗効果素子MTJと、磁気抵抗効果素子の他端に接続された配線31と、コンタクト及びバリアメタル膜を介して磁気抵抗効果素子に接続されたトランジスタTrとを具備する。

(もっと読む)

1 - 20 / 27

[ Back to top ]