Fターム[4M119DD43]の内容

MRAM・スピンメモリ技術 (17,699) | セル構成 (5,615) | アーキテクチャ (1,063) | クロスポイント方式 (193) | 1セルに複数の記憶素子を含むもの (13)

Fターム[4M119DD43]に分類される特許

1 - 13 / 13

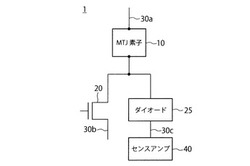

磁気抵抗効果素子、ダイオードおよびトランジスタを用いた磁気ランダムアクセスメモリ

【課題】高速動作を可能にする磁気メモリを提供する。

【解決手段】本実施形態の磁気メモリは、スピン注入書込みによって磁化の方向が不変の第1磁性層と、磁化の方向が可変の第2磁性層と、前記第1磁性層と前記第2磁性層との間に設けられたトンネル障壁層とを有する磁気抵抗効果素子と、前記磁気抵抗効果素子の前記第1および第2磁性層の一方の磁性層に電気的に接続された第1配線と、ソース/ドレインの一方が前記磁気抵抗素子の前記第1および第2磁性層の他方に電気的に接続された選択トランジスタと、前記選択トランジスタのソース/ドレインの他方に電気的に接続された第2配線と、前記磁気抵抗素子の前記第1および第2磁性層の他方に電気的に一端子が電気的に接続されたダイオードと、前記ダイオードの他の端子に電気的に接続された第3配線と、前記第3配線に電気的に接続されたセンスアンプと、を備えている。

(もっと読む)

アナログ/デジタル変換器

【課題】変換精度が高いアナログ/デジタル変換器を提供する。

【解決手段】実施形態のアナログ/デジタル変換器は、電圧生成部と複数の比較器とを備える。電圧生成部は、基準電圧を、複数の可変抵抗器で分圧して複数の比較用電圧を生成する。複数の可変抵抗器の各々は、直列に接続されるとともに、外部信号に応じて各々の抵抗値が可変に設定される複数の可変抵抗素子を含む。各比較器は、複数の比較用電圧のうちの何れかの比較用電圧とアナログの入力電圧とを比較し、その比較結果に応じたデジタル信号を出力する。

(もっと読む)

マルチレベルセル(MLC)磁気メモリセルを有する装置およびマルチレベルセル磁気メモリにデータを記憶させる方法

【課題】スピントルク注入ランダムアクセスメモリ(STRAM)メモリセルのような磁気メモリ素子にデータを書込むための方法および装置を提供する。

【解決手段】さまざまな実施の形態に従うと、マルチレベルセル(MLC)磁気メモリセルスタックは、第1の制御線に接続された第1および第2の磁気メモリ素子と、第2の制御線に接続されたスイッチング素子とを有する。第1のメモリ素子は並列に第2のメモリ素子と接続され、第1および第2のメモリ素子はスイッチング素子に直列に接続される。第1および第2のメモリ素子は、さらに、スタック内において、異なる、重ならない高さに配置される。プログラミング電流が第1および第2の制御線の間に流れて、第1および第2の磁気メモリ素子を、異なるプログラムされた抵抗に同時に設定する。

(もっと読む)

磁気トンネル接合デバイスを形成する方法

基板内にトレンチを形成することと、トレンチ内に導電性端子を堆積することと、トレンチ内に磁気トンネル接合(MTJ)ストラクチャを堆積することと、を含んでいる磁気トンネル接合デバイスを製造する方法が開示されている。MTJストラクチャは、固定された磁化方向を有する固定磁性層、トンネル接合層、および設定を変えられる磁化方向を有する自由磁性層を含んでいる。固定磁性層は、基板の表面に実質的に垂直に伸びるインターフェースに沿って導電性端子につながれる。導電性端子に隣接している自由磁性層は、デジタル値を格納するのに適した磁区を運ぶ。 (もっと読む)

磁気抵抗ラム

【課題】ワードラインとP−Nダイオードとの間にMTJ(Magnetic Tunnel Junction)を結合して2つ以上のデータを記憶させ、構造が簡単でセルサイズが小さい磁気抵抗ラム(MRAM)用セルを具現する。

【解決手段】半導体基板にドーピングされたN+領域と、前記N+領域のライン上にドーピングされたP型の不純物領域でなるP−Nダイオード、前記P型の不純物領域の上に積層されたバリヤー導電層、前記バリヤー導電層の上部に積層されたMTJ(Magnetic Tunnel Junction)、及び前記MTJの上部に積層されたワードライン、を備えるMRAMセルを含み、前記ワードラインに印加される電圧の大きさに従って前記MTJに流れる電流を制御し、前記MRAMセルにデータを書き込み、読み出すことを特徴とする。

【選択図】図3  (もっと読む)

(もっと読む)

半導体記憶装置及びそのデータ書き込み/読み出し方法

【課題】1ビットあたりのメモリセル面積を縮小する。

【解決手段】半導体記憶装置は、メモリセルMCを構成する第1乃至第3の抵抗性記憶素子MTJ1、MTJ2、MTJ3と、第1のソース/ドレイン電極が第1の抵抗性記憶素子の一端に接続され、第2のソース/ドレイン電極が第3の抵抗性記憶素子の一端に接続された第1のトランジスタTr1と、第3のソース/ドレイン電極が第2の抵抗性記憶素子の一端に接続され、第4のソース/ドレイン電極が第3の抵抗性記憶素子の一端に接続された第2のトランジスタTr2と、第3の抵抗性記憶素子の他端に接続された第1のビット線BL1と、第1及び第2の抵抗性記憶素子の他端に接続された第2のビット線BL2と、第1のトランジスタのゲート電極に接続された第1のワード線WL1と、第2のトランジスタのゲート電極に接続された第2のワード線WL2とを具備する。

(もっと読む)

磁気抵抗効果素子及びMRAM

【課題】スピン注入方式の磁気抵抗効果素子に対する書き込み電流を低減すること。

【解決手段】磁気抵抗効果素子1は、固定磁化MP1を有する第1磁化固定層13と、非磁性層14を介して第1磁化固定層13に接続された第1磁化自由層15と、固定磁化MP2を有する第2磁化固定層23と、非磁性層24を介して第2磁化固定層23に接続された第2磁化自由層25と、磁化自由層15、25の間に介在する中間配線層50とを備える。磁化自由層15、25の磁化容易軸はX方向に沿っている。固定磁化MP1、MP2は、X方向に沿った向きに固定されている。磁化自由層15、25は、中間配線層50を介して磁気的に結合している。中間配線層50は、磁化自由層15、25とオーバラップする第1領域R1から所定の方向に延びている。その所定の方向は、X方向に直角なY方向の成分を少なくとも含んでいる。

(もっと読む)

4F2のセルサイズで2Rメモリを有する3次元RRAMの製造方法

【課題】4F2のセルサイズで2Rメモリを有する3次元RRAMの製造方法を提供する。

【解決手段】多値3次元メモリアレイの製造方法は、ウェハと前記ウェハ上に周辺回路を準備する工程18と、Au、Ag、Pt、W、Cu、Ti、Ir、及び、TiNx等から成る第1金属層と、第1巨大磁気抵抗(CMR:Colossal Magnetoresistance)層、或いは、他の適切なメモリ抵抗体材料層を堆積させ、続いて、Au、Ag、Pt、W、Cu、Ti、Ir、及び、TiNx等から成る第2金属層を堆積させる工程22と、パターニングし、エッチングする工程24を備える。各工程はN段のメモリセルアレイを製造するために繰り返し行われる。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】MRAMの誤書き込み耐性及び製造歩留りの向上を図る。

【解決手段】本発明の例に関わる磁気ランダムアクセスメモリは、互いに交差する第1及び第2書き込み線Wupi,Wdownjと、第1及び第2書き込み線Wupi,Wdownjの上部からみて、中心点O1が第1及び第2書き込み線Wupi,Wdownjの交差部に重ならない磁気抵抗効果素子MTJとを備え、磁気抵抗効果素子MTJの磁化容易軸方向の中心線Ceと第1及び第2書き込み線Wupi,Wdownjの中心線C1,C2とが三角形を構成する。

(もっと読む)

磁気メモリ素子

【課題】メタルラインを利用し、情報の書き込みと読み取りとの機能を具現した磁気メモリ素子を提供する。

【解決手段】プラスチック基板上で磁化方向がスイッチングされる連続したマグネチックドメインD1〜D8が形成され、並んで配置された複数の第1メタルライン100と、第1メタルライン100と直交して配置され、第1メタルライン100を覆うトンネルを形成する複数の第2メタルライン200と、第1メタルライン100に連結され、マグネチックドメインD1〜D8をドラッギングする電流を供給する第1入力部500と、第2メタルライン200に連結され、トンネル内のマグネチックドメインD1〜D8の磁化方向をスイッチングする電流を印加する第2入力部600と、第2メタルライン200に連結され、トンネルを通過するマグネチックドメインウォールによる起電力をセンシングするセンシング部700とを具備する磁気メモリ素子である。

(もっと読む)

磁気記憶装置

【課題】 簡単な構成により3ビット動作が可能なMRAM装置を提供する。

【解決手段】 第1及び第2の磁気抵抗素子13、14と、第1及び第2の磁気抵抗素子13、14を直列に接続するワード線15と、直列に接続された第1及び第2の磁気抵抗素子13、14と並列に、ワード線15により直列に接続される第1及び第2の抵抗を具備したメモリセル1と、第1及び第2の磁気抵抗素子間16の電圧の変動を検出する電圧変動検出手段2、3を備える。

(もっと読む)

磁気記憶装置

【課題】集積度を高めたMRAMを提供する。

【解決手段】メモリセルMC(m,n)およびMC(m+1,n)は、ワード線WLnにそれぞれの一方端が接続された磁気トンネル接合素子MR1およびMR11を有し、磁気トンネル接合素子MR1およびMR11のそれぞれの他方端は、ビット線BLmおよびBLm+1に接続されている。また、メモリセルMC(m,n+1)およびMC(m+1,n+1)は、ワード線WLn+1にそれぞれの一方端が接続された磁気トンネル接合素子MR3およびMR31を有し、磁気トンネル接合素子MR3およびMR31のそれぞれの他方端は、ビット線BLmおよびBLm+1に接続されている。

(もっと読む)

電気機械メモリ、それを用いた電気回路及び電気機械メモリの駆動方法

【課題】従来の半導体プロセスとの親和性が高く、機械的に電気的導通路を完全遮断するスイッチング機能を有し、かつ不揮発性の情報記録を可能とするメモリ素子を実現する。

【解決手段】基板上に形成された電気機械メモリであって、メモリセルを電極で挟む形で形成されており、ポスト部を介して中空に架橋された梁である可動電極を具備した電気機械メモリを実現する。この構成により、簡易な構造で不揮発性メモリを実現することが可能となり、従来実現困難であった低消費電力、低コストの高性能電気機械メモリおよびそれを用いた電気機器が実現可能となる。

(もっと読む)

1 - 13 / 13

[ Back to top ]