Fターム[5B001AA14]の内容

Fターム[5B001AA14]に分類される特許

1 - 20 / 36

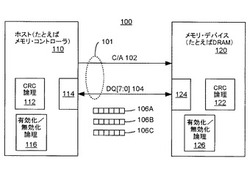

共有されるエラー・ビット・コードをもつ共通フレームにおいてデータおよびデータ・マスク・ビットを転送するためのシステム、方法および装置

【課題】共有されるエラー・ビット・コードをもつ共通フレームにおいてデータおよびデータ・マスク・ビットを転送するためのシステム、方法および装置を提供する。

【解決手段】メモリ・システム100は、ホスト110とメモリ・デバイス120との間でデータを転送するためにデータ・フレームを使用する。いくつかの場合には、システムは(別個のビット・レーンを介してではなく)データ・フレーム内で一つまたは複数のデータ・マスク・ビットも転送してもよい。システムは、データ・ビットおよびデータ・マスク・ビットをカバーするエラー・ビット・チェックサム(巡回冗長符号すなわちCRCのような)を生成してもよい。いくつかの実施形態では、データ・ビット、データ・マスク・ビットおよびチェックサム・ビットは共通フレームにおいて転送される。

(もっと読む)

情報処理システム、データエラー検出方法、プログラム及び記憶媒体

【課題】データの冗長化を行わずにデータを書き換えながらデータエラーの検出を行うことである。

【解決手段】情報記憶装置の中の監視対象領域にあるデータの整合性を確認するための第一チェック値を算出する第一チェック値算出手段と、第一チェック値を算出している途中で監視対象領域にあるデータを書き換える場合にその書き換えによる第一チェック値の変化を表す情報を作成する変化情報作成手段と、第一チェック値の算出が完了したときに第一チェック値及び変化情報作成手段により得られる第一チェック値の変化を表す情報から第二チェック値を繰り返し算出する第二チェック値算出手段と、第二チェック値算出手段で得られた第二チェック値とそれ以前に得られた第二チェック値とを比較することによりデータエラーを判定するデータエラー判定手段とを備える。

(もっと読む)

車両用電装部品の制御装置およびその制御方法

【課題】内容の異なる第1のプログラムがインストールされたマイクロコンピュータに対して記憶部全体の検査を容易に行え、マイクロコンピュータの動作の信頼性を確保することができる車両用電装部品の制御装置およびその制御方法を提供する。

【解決手段】第1記憶部31には調整データ記憶領域33が設けられ、基本プログラム記憶領域32に記憶される基本プログラムのバージョンに応じた調整データが記憶される。調整データは、第1記憶部31に対する検査プログラムによる検査結果(検査値)が、基本プログラムのバージョンによらず、同値となるように調整される。よって、検査プログラムによるフラッシュメモリ30のすべての記憶領域の検査のため、基本プログラムのバージョンに応じた検査プログラムを用意する必要がない。

(もっと読む)

車両制御システム

【課題】多数のECUがネットワークを介して協調動作を行う車両制御システムにおいて

、低コストでネットワーク内の障害ノードを正確に特定する。

【解決手段】各ノードは、ネットワーク内ノード状態判定手段,自ノードによるノード状

態判定結果送信手段および他ノードによるノード状態判定結果受信手段、および障害ノー

ド特定手段から構成され、前記ネットワーク内ノード状態判定手段による判定結果を他ノ

ードと相互に交換することにより、障害ノードを特定する。

(もっと読む)

情報処理装置および情報処理方法

【課題】動作に重要なプログラムが書き込まれているフラッシュROM上の物理的な記憶領域のデータが不良になっている場合にもプログラムを実行できるようにする。

【解決手段】この情報処理装置は、複数のカラムを一単位とするブロック単位にデータを記憶可能な物理的な記憶領域を有するフラッシュメモリと、プログラムデータを複数のブロックに分けて前記物理的な記憶領域に書き込み、各ブロックに付与した第1のエラー訂正符号を前記物理的な記憶領域に書き込み、前記プログラムデータに付与した第2のエラー訂正符号を前記フラッシュメモリに書き込む書き込み装置とを備える。

(もっと読む)

ストレージデバイス内のエラーデータを追跡するシステムおよび方法

エラーデータを追跡するシステムおよび方法を開示する。この方法が、第1のエラー訂正コード演算のエラー場所に関連づけられた第1のチェックサムを受信するステップと、第2のエラー訂正コード演算のエラー場所に関連づけられた第2のチェックサムを受信するステップとを含む。第1のチェックサムは、第2のチェックサムと比較され、その比較結果に基づいてメモリアレイの領域に動作が開始される。  (もっと読む)

(もっと読む)

半導体集積回路及び半導体集積回路の故障診断方法

【課題】CPUのパフォーマンスに影響を及ぼすことなく、故障診断を行うことを可能にする半導体集積回路を提供する。

【解決手段】通常動作において利用される第1のバスBUSA、及びそれとは異なる第2のバスBUSAに接続されたCPU1から第2のバスを介して出力される診断情報に基づいて、診断マクロ6が誤り検出情報を求め、プログラムの実行に応じて求められた最終の誤り検出情報と保持している1つの期待値との比較によりCPUが故障しているか否かを判定するようにして、通常動作に利用される第1のバスの負荷を増加させずに、故障診断を行えるようにする。

(もっと読む)

レジューム方法および情報処理装置

【課題】 情報処理装置等のサスペンド状態からの速やかなレジューム動作に関する技術を提供する。

【解決手段】 レジューム機能を備える情報処理装置であって、前記情報処理装置で稼動するアプリケーションと、前記アプリケーションが動作するメモリ領域と、前記メモリ領域の内容が保持されているかレジューム時に点検する点検手段と、サスペンド要求を受信した場合、サスペンド状態に移行する手段と、サスペンド状態からの復帰要求を受信した場合、サスペンド状態からの復帰処理を行う復帰手段とを備え、レジューム時は前記点検手段と前記復帰手段とが並列動作することを特徴とする情報処理装置。

(もっと読む)

分散的な記憶及び通信

a)データを複数のデータサブセット(A,B)に分割し、b)複数のデータサブセット(A,B)からパリティデータ(P)を生成することで、前記複数のデータサブセットのうちの1つ又は複数のデータサブセットが、残りデータサブセットとパリティデータ(P)とから再生成されるようにすることにより、データを記憶、検索、送信、又は受信する。ステップaとbとが、前記複数のデータサブセット及び前記パリティデータの各々に対して繰り返されることにより、更なるデータサブセットと更なるパリティデータとが生成され、d)前記更なるデータサブセットと前記更なるパリティデータとが別々の記憶場所(380)に記憶されるか、又は送信される。 (もっと読む)

データ書換方法、データ書換装置及びデータ管理装置

【課題】より正確にメモリの書き換えを行うことができるデータ書換方法等を提供する。

【解決手段】データ数、データ部及びサムチェック部を有する形式の更新用のデータをデータ管理装置に対して送信するデータ書換装置を有するデータ書換システムにおけるデータ書換方法であって、データ書換装置は、更新用のデータが、データ部及びサムチェック部についてはデータ圧縮後の値であり且つデータ数についてはデータ圧縮前の値である圧縮データか否かを判定し(S2)、圧縮データであると判定されると、更新用のデータをデータ管理装置に対して送信する(S3)。また、データ管理装置は、受信した更新用のデータのデータ部を解凍し(S4)、解凍された更新用のデータが正しいデータ形式であるか否かを判定し(S5)、正しいデータ形式であると判定されると、解凍された更新用のデータに基づき自装置が管理するデータを書き換える(S6)。

(もっと読む)

共有されるエラー・ビット・コードをもつ共通フレームにおいてデータおよびデータ・マスク・ビットを転送するためのシステム、方法および装置

【課題】共有されたエラー・ビット・コードをもつ共通フレームにおいてデータおよびデータ・マスク・ビットを転送するシステム、方法および装置を提供する。

【解決手段】メモリ・システムは、ホストとメモリ・デバイスとの間でデータを転送するためにデータ・フレームを使用する。システムは(別個のビット・レーンを介してではなく)データ・フレーム内で一つまたは複数のデータ・マスク・ビットも転送してもよい。システムは、データ・ビットおよびデータ・マスク・ビットをカバーするエラー・ビット・チェックサム(巡回冗長符号すなわちCRCのような)を生成してもよい。データ・ビット、データ・マスク・ビットおよびチェックサム・ビットは共通フレームにおいて転送される。

(もっと読む)

データ完全性検証メカニズム

【課題】データの完全性を保守するための方法および装置が提供される。

【解決手段】ある局面の方法に従うと、物理的なチェックサム計算がデータブロック上で行なわれる(404)。物理的なチェックサム計算を行なった後、論理チェックが、データブロック内に含まれるデータ上で行なわれる(406)。データブロックが論理チェックをパスすると、データブロックは不揮発性メモリに書込まれ得る(410)。その後、データブロックが不揮発性メモリから読出されると、物理的なチェックサム検証手順がデータブロック上で行なわれて(412)、データブロック内に含まれるデータ上で論理チェックが行なわれた後にデータブロックが破損したかが判断される。

(もっと読む)

マイクロプロセッサおよびシグネチャ生成方法ならびに多重化システムおよび多重化実行検証方法

【課題】命令実行がプログラム順序に関係なく行われるマイクロプロセッサを用いた多重化システムにおいて、容易にシグネチャ生成できるようにする。

【解決手段】命令実行がプログラム順序に関係なく行われるマイクロプロセッサにおいて、命令が実行され、実行終了した命令の結果がプログラム順に並べ直されて命令実行が確定された、ということを示す完了命令情報を用いてシグネチャを生成する。

(もっと読む)

画像形成装置

【課題】自装置に格納されたファームウェアの書き換え作業を確実に行なうことができる画像形成装置を提供する。

【解決手段】画像形成動作を制御するためのファームウェアを自装置に格納し、かつファームウェアを書き換え可能な画像形成装置であって、書き換え元となるファームウェアを一時的に保持する一次記憶バッファと、画像形成装置で実行される対象となるファームウェアを記憶している書き換え可能な不揮発性メモリと、記憶媒体に記憶されているファームウェアを読み取り、一次記憶バッファに書き込むファームウェア読み取り部と、ファームウェア読み取り部で読み取られ、一次記憶バッファに記憶されているファームウェアに含まれる書き換えプログラムを実行することにより、不揮発性メモリに記憶されているファームウェアを、一次記憶バッファに記憶されているファームウェアで書き換えるファームウェア書き換え部とを備える。

(もっと読む)

二重化システムにおける記憶装置の制御方法

【課題】二重化したNVRAMの情報が不一致状態でもどちらのNVRAMの情報を採用すべきか判断できるようにする。

【解決手段】各BMC21,31に含まれないNVRAM11,12を設け、BMC21内部にバックアップNVRAM211を、BMC31内部にバックアップNVRAM311を設け、BMC21(31)がNVRAM11,12にデータを書き込む際、バックアップNVRAM211(311)にもデータから算出したハッシュ値(またはチェックサム)を書き込む。BMC21(31)初期化時はNVRAM11,12のデータを比較し、一致ならそのデータをそのまま使用、一致しない場合、バックアップNVRAM211(311)とハッシュ値(またはチェックサム)の比較を行い、NVRAM11,12のうち一致する方のデータを使用する。どちらとも一致しない場合、NVRAM11,12を規定の値で初期化する。

(もっと読む)

演算回路

【課題】(1)任意のデータ数を入力とする演算に対応することができ処理効率の良い演算回路(アクセラレータ)の実現、(2)演算回路内に具備するデータレジスタ(処理用バッファ)のサイズを小さくしてコスト削減、の2つを実現できる技術を提供する。

【解決手段】演算回路103は、ディスクリプタ制御に従い、DMA転送を用いて、任意数の入力データを演算して結果を出力するものであり、任意数の入力データを一度に演算せずに、複数に分割して演算処理する。演算回路103は、前記分割した演算毎の途中結果を、一旦外部記憶装置102に格納し、次の演算処理にて前記途中結果を読み込んで演算処理し、その繰り返しにより、最終結果を得る。演算回路103に具備するアドレスレジスタ130の数に対応した周期的な処理単位で演算を行う。

(もっと読む)

データ記憶装置及びデータ記憶装置からのデータ読み出し方法

【課題】記憶容量を高い効率で利用すると共に、高い信頼性を有してデータを記憶することのできるデータ記憶装置を提供する。

【解決手段】1つのデータが2ビット以上の所定のビット数からなる複数のメインデータDTと、メインデータDTの誤りを訂正可能な1つ又は複数の誤り訂正データECと、メインデータDT及び誤り訂正データECの少なくとも1つに誤りがあるか否かを検出可能である1つの行誤り検出データHDと、からなる1つの行データセット10を複数行備える。行データセット20を構成する1つのデータの複数行に亘る集合である1つの列データセット20に対して、少なくとも1つのデータに誤りがあるか否を検出可能な1つの列誤り検出データVDを、各列データセット20に備える。

(もっと読む)

プログラマブル論理回路更新装置、更新方法、データ処理装置およびネットワーク装置

【課題】メモリに書き込まれた新たなコンフィギュレーションデータの誤りを簡易な構成で検出する。

【解決手段】FPGA110の内部回路として構成されたチェック論理回路114は、CPU140からフラッシュメモリ130に新たなコンフィギュレーションデータが書き込まれると、このデータを読み出し、チェックサムデータを算出する。フラッシュメモリ130には、新たなコンフィギュレーションデータとともに、予め算出されたチェックサムデータが記録されている。そのため、チェック論理回路114は、この予め記録されたチェックサムデータと、コンフィギュレーションデータの読み込みによって算出したチェックサムデータとを比較することにより、フラッシュメモリ130に対して、新たなコンフィギュレーションデータが正しく書き込まれているかを自立的に検出することができる。

(もっと読む)

保護制御装置、保護制御方法及び保護制御プログラム

【課題】第1の記憶手段から第2の記憶手段にロードするアドレスが予め予測できない場合であっても、故障確率の低い簡素な構造としながら、メモリの破壊検出による異常動作の未然防止が可能な保護制御技術を提供する。

【解決手段】プログラムを記憶するためのハードディスク1及びRAM2、ハードディスク1からRAM2に、実行するプログラムをロードするローダ51、ローダ51がプログラムをロードした時に、当該プログラムのチェックサム値を計算するサム値演算部51a、チェックサム値を格納するプログラムチェックサムテーブル22、サム値演算部51aに対して、チェックサム値の再計算を指示する再計算指示部51c、プログラムチェックサムテーブル22に格納されたチェックサム値と、再計算されたチェックサム値とを比較することにより、プログラム破壊による異常の有無をチェックするサム値チェック処理部53を有する。

(もっと読む)

データ更新方法、データ更新プログラム、及びそれらを用いた情報端末装置

【課題】書き換え可能な記憶素子に格納されるプログラムやデータの更新時において、更新するデータの誤り検出の誤判定を回避するデータ更新方法を提供する。

【解決手段】記憶素子が保持する第1のデータを第2のデータへ書き換える際に更新データを用いて書き換えを行うデータの更新方法であって、更新データは、前記第1のデータの計算領域情報と計算値とを有し、前記更新データが有する前記計算領域情報に基づいて前記第1のデータから算出した値と、前記更新データが有する計算値とを比較し、比較結果に応じて、前記更新データを用いて前記第2のデータへ書き換えることを特徴とするデータ更新方法。

(もっと読む)

1 - 20 / 36

[ Back to top ]