Fターム[5B005MM36]の内容

階層構造のメモリシステム (9,317) | 階層メモリの種類 (2,100) | 仮想メモリ (220) | 多重仮想メモリ (120) | 仮想計算機 (66)

Fターム[5B005MM36]に分類される特許

1 - 20 / 66

アドレス変換装置、アドレス変換装置の制御方法及び演算処理装置

【課題】エントリのヒット率の低下を抑制できるようにする。

【解決手段】仮想アドレスと物理アドレスとの対応関係を示すアドレス情報がそれぞれ記憶される複数のCAM回路を有するCAM部と、新たなアドレス情報を記憶させる場合に書込みポインタが示しているCAM回路にアドレス情報の書込みを指示する書込み制御部とを有するマイクロTLBにおいて、書込みポインタが示しているCAM回路に記憶されているアドレス情報が、アドレス変換に使用されたことが示されている場合には書込みポインタをインクリメントするようにして、アドレス情報の使用が示されたCAM回路に新たなアドレス情報が書込まれることを回避して最近使用されているアドレス情報を保持し、ヒット率の低下を抑制する。

(もっと読む)

演算処理装置及び演算処理装置の制御方法

【課題】使用頻度の高い論理アドレス空間が頻繁に入れ替わることを防止する演算処理装置を提供することを課題とする。

【解決手段】アドレス変換対を記憶するバッファ領域を有する記憶装置に接続される演算処理装置において、複数の論理アドレスレジスタのうち使用履歴が最も古い論理アドレスレジスタの番号を保持するLRUレジスタと、記憶装置に対するアクセス要求に含まれる論理アドレスが、下限論理アドレスレジスタが保持する下限論理アドレスから上限論理アドレスレジスタが保持する上限論理アドレスまでの論理アドレス空間の範囲に入っていない場合、LRUレジスタが保持する論理アドレスレジスタの番号を読み出す読み出し部(S502)と、読み出された番号の論理アドレスレジスタを無効にし、アクセス要求に含まれる論理アドレスに対応する論理アドレス空間を、無効にした論理アドレスレジスタに設定する設定部(S410)を有する。

(もっと読む)

仮想計算機システム、仮想計算機システムのメモリ管理方法およびメモリ管理プログラム

【課題】稼動中のゲストOSの性能を低下させず、かつ、高速でゲストOSを起動させる。

【解決手段】仮想計算機システムは、実計算機で複数のオペレーティングシステムを同時実行可能な仮想計算機システムであって、停止したオペレーティングシステム用の主メモリを、稼働中のオペレーティングシステム用のキャッシュ領域に割り当てるキャッシュ割当手段11と、稼働中のオペレーティングシステム用のキャッシュ領域におけるクリーン領域を、起動するオペレーティングシステムの主メモリに割り当てる主メモリ割当手段12とを備える。

(もっと読む)

ページ属性サポートのある仮想アドレスから物理アドレスへの変換

【課題】ページ属性サポートのある仮想アドレスから物理アドレスへの変換のためのシステム、方法及び装置を提供する。

【解決手段】仮想メモリ・ポインタをあるメモリ位置についての物理的なメモリ・アドレスに変換する命令を受領する段階502と、仮想メモリ・ポインタをページ・テーブル情報に基づいて物理的なメモリ・アドレスに変換する段階504と、物理的なメモリ・アドレスおよび一つまたは複数のページ属性を返す段階506を含む。

(もっと読む)

仮想計算機システムにおけるメモリ割り当て方法

【課題】 アドレス変換機構を持ったIOデバイスを含む仮想計算機システムにおいて、IOデバイスのハードウェア上の制限を回避し、柔軟なゲストメモリ割り当てを可能とする。

【解決手段】 IOデバイス内のアドレス変換機構とチップセット内のアドレス変換機構を併用し、ゲスト物理アドレスからホスト物理アドレスへの変換を行う際には、仮想的なアドレスである仮アドレスを経由する。仮アドレスでゲストメモリ領域の分散を抑え、IOデバイス内のアドレス変換テーブルエントリを節約することで、フラグメント化によるゲストメモリ割り当て失敗を抑える。また、仮アドレスからホスト物理アドレスへの変換にチップセット内のアドレス変換機構を用いることで、仮想計算機に割り当てるメモリサイズを細かく指定できるようになる。

(もっと読む)

バーチャルマシーンシステムの物理的メモリのバーチャル化

【課題】 本発明は、上記問題点を解決するバーチャルシステムについてのプロセッサ、方法及びシステムを提供する。

【解決手段】

上記課題を解決するため、本発明は、バーチャルシステムを有するプロセッサであって、前記バーチャルシステムは、当該プロセッサが動作可能なホストマシーン上で実行可能なバーチャルマシーン上で実行可能なゲストソフトウェアによるゲスト物理的メモリの参照を前記ホストマシーンのホスト物理的メモリの参照にマップする拡張ページングテーブルを有するメモリバーチャル化サポートシステムを有することを特徴とするプロセッサを提供する。

(もっと読む)

翻訳ルックアサイドバッファと拡張ページングテーブルとの同期化

【課題】仮想マシンにおける効率的なアドレス変換が可能な手法を提供する。

【解決手段】プロセッサ318は、仮想化に基づくシステムのゲストの物理アドレス(ゲスト物理アドレス)から仮想化に基づくシステムのホストの物理アドレス(ホスト物理アドレス)までの翻訳ルックアサイドバッファ(TLB)323に格納されたマッピングを仮想化に基づくシステムの拡張ページングテーブル(EPT)328に格納された対応するマッピングを同期させる命令を実行するロジック322を含む。

(もっと読む)

パーティション分割されたシステムにおいて、デバイスがメモリにアクセスするための、ゲスト・アドレスからホスト・アドレスへの変換

【課題】パーティション分割されたシステムの仮想化機能を向上させる。

【解決手段】装置がインターフェース、パーティション分割論理190、第一のアドレス変換論理131および第二のアドレス変換論理132を含む。インターフェースがパーティション分割されたシステムにおいてメモリにアクセスする要求をデバイスから受け取る。パーティション分割論理190は、前記デバイスが第一のパーティションに割り当てられているか、第二のパーティションに割り当てられているかを判別する。第一のアドレス変換論理131は、第一のパーティション内の第一のゲスト・アドレスを第一のホスト・アドレスに変換する。第二のアドレス変換論理132は、第二のパーティション内の第二のゲスト・アドレスを第二のホスト・アドレスに変換する。

(もっと読む)

計算機システム

【課題】高速化による性能向上、および機能ごとの独立性能設計の容易化を実現しつつ、大容量のキャッシュメモリの搭載を必要としない計算機システムを提供する。

【解決手段】主記憶装置101と、複数の仮想プロセッサ上で実行される処理を逐次実行する処理実行部111と、複数の仮想プロセッサ間で共用される1次キャッシュメモリ113と、仮想プロセッサのプロセッサ数に応じて分割された複数の記憶領域を有し、各仮想プロセッサに各記憶領域が対応付けられ、各記憶領域が、当該記憶領域に対応付けられた仮想プロセッサが利用するデータを記憶する2次キャッシュメモリ107と、仮想プロセッサごとのコンテキストを記憶しているコンテキストメモリ103と、仮想プロセッサのコンテキストの退避及び復帰を行う仮想プロセッサ制御部104と、1次キャッシュ制御部112と、2次キャッシュ制御部106とを備える。

(もっと読む)

情報処理装置及び情報処理プログラム

【課題】複数のOSが動作する情報処理装置にあって、共有メモリ内にあるプログラムからそのプログラムが動作しているOSが提供するプログラムを呼び出せるようにした情報処理装置を提供する。

【解決手段】共有メモリ設定手段は、第1のOSにおける仮想メモリ空間と第2のOSにおける仮想メモリ空間で共有されているメモリであって、それぞれの仮想メモリ空間における同じアドレスでメモリをアクセスできる共有メモリを設定し、呼出手段は、第1のOSが提供する第1のプログラムと第2のOSが提供する第2のプログラムを呼び出し、呼出手段が呼び出す第1のプログラムと第2のプログラムは、同じ機能を有しているが、異なる実装方法であり、呼出手段は、共有メモリにあって、第1のOS又は第2のOSで動作している第3のプログラムからの呼び出しによって、第3のプログラムが動作しているOSに応じて第1又は第2のプログラムのいずれかを呼び出す。

(もっと読む)

メモリ共有装置

【課題】仮想化環境にて共有メモリを用いたメモリ共有装置の作成をおこなう。

【解決手段】 共有メモリの実体である共有ページと、各共有ページのインデックス値を集めたデータである共有設定ページと、各共有設定ページのページフレーム番号とインデックス値を対応付けて記憶するグラントテーブルとを有するサーバと、グラントテーブルのインデックス値を管理するデータベースを有するホストと、前記共有ページ及び共有設定ページがマップされる共有ページ領域、及び共有設定ページ領域を有するクライアントとを有することを特徴とするメモリ共有装置。

(もっと読む)

DMAセキュリティチェック回路及びDMAセキュリティチェック方法

【課題】IO TLB(I/O Translation Look aside Buffer)でキャッシュミスした場合にDMAが待たされることを防止する。

【解決手段】IOV(I/O Virtualization) HBA(Host Bus Adapter)に対応したDMA(Direct Memory Access)セキュリティチェック回路が、HBAからのDMAリード要求に対しディスクリプタフェッチを検知した場合に、当該DMAリード要求のリプライデータの中から抽出した論理アドレスと、当該リプライデータに含まれるリクエストIDとが同じゲスト空間のものであるかを判定し、同じゲスト空間のものである場合に当該リプライデータに含まれるアドレスが適切であると判断する。

(もっと読む)

仮想ディスク制御システム、方法及びプログラム

【課題】ゲストOSに依らず、仮想化環境において物理メモリを有効的に活用することができる仮想ディスク制御システムを提供することを目的とする。

【解決手段】物理マシン上で動作する仮想マシンが所定のデータを仮想ディスクに格納する際に、データの物理的な格納先を物理マシンが搭載する物理メモリに指定する格納先指定手段101と、格納先指定手段101の指定に基づいて、データを物理メモリに格納するとともに、仮想ディスクにおける仮想の格納領域を示す格納領域情報と物理メモリにおける実際の格納場所を示す格納場所情報とを対応付ける対応付け手段201とを含む。

(もっと読む)

仮想化処理システムにおけるアドレスマッピング

階層的な変換テーブル制御

アーキテクチャイベントの間のプロセッサリソースの保持

【課題】アドレス空間のコンテクストの切り替えに関連するオーバヘッドを低減する。

【解決手段】本発明のプロセッサは、アドレス空間に対応するページディレクトリに基づくアドレスを記憶する制御レジスタ、アドレス空間識別子のフィールドを含むエントリを有する変換ルックアサイドバッファ、及び変換ルックアサイドバッファをフラッシュすることなしにアドレス空間の間で切り替えを行うため、「MOV to 制御レジスタ」命令を実行する実行ロジック、を備える。

(もっと読む)

ドメインベースのキャッシュ・コヒーレンス・プロトコル

簡単にいうと、ドメインベースのキャッシュ・コヒーレンス・プロトコルを用いてキャッシュ内のデータブロックにアクセスするための技術が概説される。第1のタイル、第1のドメインの第1のプロセッサはデータブロックにアクセスするよう求める要求を評価するように構成することができる。第1のドメインの第2のタイルのキャッシュは、データブロックが第2のタイルにキャッシュされているときに、第1のタイルにデータブロックを送るように構成することができる。第1のプロセッサは、キャッシュされた位置が第1のプロセッサのドメインの外部にあるときに、別のドメインの第3のタイルに要求を送るように構成することができる。第3のプロセッサは、データブロックのキャッシュされた位置と関連付けられたデータドメインを判定し、そこに要求を送るように構成することができる。第4のタイルは、要求を受け取り、第1のタイルにデータブロックを送るように構成することができる。  (もっと読む)

(もっと読む)

仮想マシンの対称型ライブ・マイグレーション

【課題】 仮想マシンの対称型ライブ・マイグレーションのための方法、情報処理システム及びコンピュータ・プログラムを提供する。

【解決手段】 第1の仮想マシンの一組のメモリ・ページについての第1の最長時間未使用マップを生成する。第1の最長時間未使用マップは、メモリ・ページの物理アドレス位置情報を含んだメタデータを含む。第1の仮想マシンの動作中、第1の仮想マシンのメモリ・ページの第1のもの及び第1のメモリ・ページについてのメタデータを、第1の仮想マシンから第2の仮想マシンに送る。第2の仮想マシンの第1のメモリ・ページ及びそれと関連したメタデータを、第1の仮想マシンにおいて第2の仮想マシンから受け取る。第1の仮想マシンのメモリ・ページは、第1の仮想マシンのメモリ・ページの各々がどのくらい最近に使用されたかに基づいて、第1の最長時間未使用マップの第1の位置から第1の最長時間未使用マップの最後の位置に配列される。

(もっと読む)

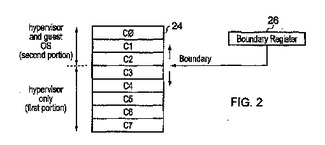

データ処理システム内のハードウェア資源管理

性能モニタ(12)およびコンテキストポインタ(18)等の複数のハードウェア資源を伴う、プロセッサ(6)を提供する。境界指示回路(14、20)は、プログラム可能であり、ハードウェア資源を第1の部分と第2の部分とに分割する境界位置を指示する、境界値を記憶する。資源制御回路(16、22)は、プログラム実行回路(8)が第1のプログラムを実行しているとき、複数のハードウェア資源のうちのいくつが存在するかについての問い合わせに、第1の値を返すように応答し、一方、プログラム実行回路が第2のプログラムを実行しているとき、第2の部分内のこれらのハードウェア資源に対応する値を返すことによって、そのような問い合わせに応答するように、ハードウェア資源へのアクセスを制御する。  (もっと読む)

(もっと読む)

マルチプロセッサ仮想マシン環境においてアドレス変換をサポートする方法及び装置

【課題】ゲスト変換データ構造におけるどのエントリが仮想マシンによって修正されたかを判定する。

【解決手段】判定は、シャドウ変換データ構造におけるエントリに関連付けられた属性、及び仮想マシン・モニタによってメンテナンスが行われるシャドウ変換データ構造から抽出されたメタデータに基づいて行われる。方法は、ゲスト変換データ構造における修正されたエントリに対応するシャドウ変換データ構造におけるエントリを、ゲスト変換データ構造における修正されたエントリと同期化させる工程と、アクティブ・エントリ・リストにおける各エントリを複数のプロセッサの何れが保有するかを識別するシャドウ変換データ構造における対応するエントリに関連付けられた属性に少なくとも部分的に基づいて、アクティブ・エントリ・リストにおいてどのエントリを保つかを判定する工程とを含む。

(もっと読む)

1 - 20 / 66

[ Back to top ]