Fターム[5B013AA14]の内容

Fターム[5B013AA14]に分類される特許

1 - 20 / 74

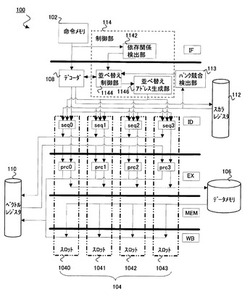

プロセッサ、及びプロセッサの制御方法

【課題】複数のパイプラインを有するプロセッサにおいて、処理効率を低下させることなくバンク競合を回避する。

【解決手段】メモリの複数のバンクに第1のバンクアクセス順序でアクセスする第1の処理部と、前記第1の処理部のアクセスの開始に続いて第2のバンクアクセス順序で前記複数のバンクにアクセスを開始する第2の処理部と、前記第1の処理部及び前記第2の処理部による前記複数のバンクへのアクセスが競合する場合に、前記第2のバンクアクセス順序を前記競合が生じない第3のバンクアクセス順序に並べ替えて前記第2の処理部を前記複数のバンクにアクセスさせる制御部とをプロセッサに備えることで、処理効率を低下させることなくバンク競合を回避できる。

(もっと読む)

プロセッサ、システムおよびプロセッサの動作方法

【課題】実行サイクルが動的に変化する命令を実行するときに、不要な命令が実行されることを防止し、プロセッサの演算処理の性能を向上する。

【解決手段】プロセッサは、実行サイクル数が動的に変化する第1の命令を実行するために、最大の実行サイクル数に対応する数の複数の第1の命令である命令群が格納されている命令メモリから第1の命令をフェッチするフェッチ部と、命令群の次の命令が格納されている命令メモリのアドレスが保持されるアドレスレジスタと、フェッチ部によりフェッチされた命令を解読するデコード部と、デコード部により解読された命令を受けて演算を実行し、第1の命令の実行に必要な演算の完了を判断したときに終了信号を出力する演算部とを備え、フェッチ部は、終了信号に応答してアドレスレジスタ内のアドレスを用いて次の命令を命令メモリからフェッチする。

(もっと読む)

ベクトル処理装置、システムおよびベクトル処理装置の動作方法

【課題】 ベクトル長が小さい場合にも、ベクトルレジスタファイルを効率よく使用し、ベクトル処理装置の性能を向上する。

【解決手段】 ベクトル処理装置は、ベクトルデータを各々格納する複数のデータレジスタが割り当てられるベクトルレジスタファイルと、ベクトルレジスタファイル内に割り当てられ、命令に含まれるオペランドにより指定可能な最大数のデータレジスタを各々有し、ベクトル長に応じてサイズが変化する複数のレジスタセットと、レジスタセットのうち、ベクトル演算に使用するベクトルデータを保持するレジスタセットである有効レジスタセットを示す情報が格納される制御レジスタと、ベクトル長に応じて変化する有効レジスタセットの開始位置を基準にしてオペランドにより指定されるデータレジスタを用いてベクトル演算を実行する実行部とを有している。

(もっと読む)

メモリアクセス命令の追い越し制御によるプログラムの高速化方法

【課題】プログラムを高速に実行する手法を提供する。

【解決手段】ロード命令の追い越しの許可/不許可を示す追い越し許可フラグをもつストア命令、ロード命令の追い越しをブロックする命令を含む命令セットをもつCPUと、そのフラグを設定する追い越し許可フラグ設定手段、その命令を生成する追い越しブロック命令生成手段をもつコンパイラと、追い越しをブロックする命令を命令リオーダバッファに登録する追い越しブロック命令登録手段、追い越し許可フラグの設定されたストア命令を参照しながら、メモリアクセス命令を命令リオーダバッファに登録する命令バイパス手段をもつ命令リオーダユニットを有する。

(もっと読む)

ベクトル処理装置、ベクトル処理方法、及び、プログラム

【課題】命令パケットを制御することにより処理性能を向上させるのに好適なベクトル処理装置等を提供する。

【解決手段】命令パケットバッファ部11b2は、スカラプロセッシング部11により発行される第1の命令パケットを格納する。アドレス比較・バッファ制御部11b1は、第1の命令パケット及び第1の命令パケットの後に発行される第2の命令パケットの種類を判別し、第1の命令パケットが指定する第1のアドレスと第2の命令パケットが指定する第2のアドレスとを比較し、第1及び第2の命令パケットを結合する指示を出力する。アドレス比較・バッファ制御部11b1は、第1の命令パケットの命令がスカラストア命令であり、第2の命令パケットの命令がスカラストア命令であって、第1及び第2の命令パケットのアドレスが一致する場合、結合処理部11b3に結合する指示を出力し、結合処理部11b3は、第1及び第2の命令パケットを結合する。

(もっと読む)

プロセッサ装置及びその演算方法

【課題】複数のPEを備えた並列型SIMDプロセッサにおいて並列性の高い行列転置方法等を提供する。

【解決手段】プロセッサ装置は、各PE方向に行ベクトルデータが配列され、かつ各PE内レジスタ方向に列ベクトルデータがそれぞれ配列された複数個の行列データの数学的転置を行うときに、各PE間のレジスタ参照、格納又は移動を行う単一命令複数データ型の演算命令を用いて、対角位置の要素データ又はベクトルデータの移動をして交換を行うステップを含み、行列に含まれる2のべき乗次の部分行列を対象にして、最小2次の行列(2×2要素)では対角要素データの移動又は交換を行い、上位のべき乗次数の部分行列では対角位置の下位の部分行列の要素データ群をブロックとして一括に移動又は交換し、これらの手順を上位次数から最小次数まで、又は最小次数から上位次数まで順次繰り返して行って複数の行列データを一括して並列同時に転置処理する。

(もっと読む)

ディジタル信号処理装置

【課題】積和演算の処理能力を向上する。

【解決手段】ディジタル信号処理装置は、複数のレジスタと、クロック信号に同期して時系列的に前記複数のレジスタにデータを格納するデータ転送部と、同じタイミングで前記複数のレジスタに格納されたデータに対して演算を実行する演算部とを備える。前記データ転送部は、与えられた命令に応じて、前記クロック信号の或るタイミングで前記複数のレジスタのうちの或るレジスタに格納された前記データを、次のタイミングで前記複数のレジスタのうちの指定された他のレジスタに格納するように転送する。SIMDによるフィルタ演算の処理能力を向上することができる。

(もっと読む)

ベクトル命令制御回路及びリストベクトルの追い越し制御方法

【課題】メモリアクセスの性能及びプログラムの処理速度への影響を抑えた上で、リストベクトルの追い越し制御を実現すること。

【解決手段】本発明にかかるベクトル命令制御回路は、外部から受け付けた複数の命令に関する情報を、アクセス先のメモリのアドレスを含めて命令単位に受け付け順に保持する命令保持回路と、受け付けた複数の命令のうち複数のアドレスの指定を含むリストアドレスを有するリストベクトル命令について、当該リストアドレス内のアドレスを比較して最大アドレス及び最小アドレスを抽出し、当該抽出された最大アドレス及び最小アドレスを当該リストベクトル命令に対応付けて、命令保持回路に格納するアドレス抽出回路と、命令保持回路に格納された最大アドレス及び最小アドレスに基づき、リストベクトル命令と、当該リストベクトル命令の後続命令との追い越し判定を行う追い越し判定回路と、を備える。

(もっと読む)

ベクトルマスク設定技術

【課題】本発明の課題は、マイクロプロセッサアーキテクチャの命令セットアーキテクチャにおいて使用される効果的なベクトルマスク生成技術を提供することである。

【解決手段】本発明によると、上記課題は、ベクトルマスクを格納するための第1処理を検出する第1ロジックと、前記第1処理より以前のベクトルマスク値を生成するための最新の第2処理を特定する第2ロジックと、前記第2処理が特定される場合、前記第1処理の実行を回避する第3ロジックとから構成されることを特徴とするプロセッサにより解決される。

(もっと読む)

ベクトル演算処理装置、ベクトル演算処理方法およびベクトル演算処理プログラム

【課題】キャッシュメモリと主記憶装置との間の負荷を軽減し、ロードバッファの解放タイミングを早める。

【解決手段】投機的に実行されるベクトルロード命令が発行された場合に、ベクトルデータのバッファ領域M2を確保するロードバッファ管理部31と、メモリアクセスリクエストに基づいて要素データをキャッシュメモリM1又は主記憶装置9から読み出し、読み出した要素データをバッファ領域M2に格納させるキャッシュ処理部4と、投機的実行に成功した場合にバッファ領域の要素データをベクトルレジスタM3に転送してからバッファ領域M2を解放し、一方、投機的実行に失敗した場合にバッファ領域M2の要素データをベクトルレジスタM3に転送せずにバッファ領域M2を解放するベクトル処理部6とを備え、キャッシュ処理部4は投機的実行に失敗した場合に要素データの主記憶装置9からの読み出しを抑止する。

(もっと読む)

ベクトル処理回路、命令発行制御方法、及びプロセッサシステム

【課題】本実施例に係るベクトル処理回路は、データ語長が異なる命令に対してレジスタ干渉の有無の判定を正確に行い、後続命令の発行タイミングを適切に調整し、命令実行の効率化を図ることを目的とする。

【解決手段】本実施例に係るベクトル処理回路で、各パイプライン演算器が、1つの命令に対して、ソースとして指定された複数の配列要素のデータを複数のサイクルに分けて演算し、演算結果をディスティネーションとして指定された複数の配列要素に複数のサイクルに分けて格納し、命令発行制御回路が、命令のデータ語長に応じて配列要素のデータサイズを変化させ、先行命令のデータ語長が後続命令のデータ語長より長いとき、先行命令の非先頭のサイクルで処理される少なくとも1つの配列要素と後続命令の先頭サイクルで処理される配列要素との間でレジスタ干渉の有無を判定し、レジスタ干渉の判定結果に基づいて後続命令の発行タイミングを調整する。

(もっと読む)

プロセッサ及びベクトルロード命令の実行方法

【課題】ベクトルロード命令を投機的に実行して、メモリアクセスのレイテンシを隠蔽すること。

【解決手段】本発明のプロセッサは、分岐命令における分岐先の分岐予測に基づき、主記憶装置から読み出されたベクトルロード命令を発行する命令発行部と、発行されたベクトルロード命令に基づく複数のベクトルデータを主記憶装置から取得するための複数の取得要求の発行を開始するデータ取得部と、分岐命令による分岐先が確定した後に、分岐予測の成否を判定する判定部と、判定部により、分岐予測が成功したと判定された場合、複数の取得要求に基づく全てのベクトルデータを取得し終えた後に、ベクトルレジスタに対して当該全てのベクトルデータを転送し、分岐予測が失敗したと判定された場合、データ取得部により発行された取得要求により取得されたベクトルデータを廃棄するベクトルロード管理部と、を備える。

(もっと読む)

情報処理装置

【課題】処理速度、或いは、プログラムの実行速度を向上させることができる情報処理装置の提供を図る。

【解決手段】ベクトルレジスタファイル(32)がベクトル長により物理番号と論理番号が変化する情報処理装置であって、ベクトル長を指定するベクトル長レジスタ31と、前記ベクトル長レジスタによるベクトル長の第1値VLと、ベクトル長を変化させる命令によるベクトル長の第2値VL’を比較する比較器21と、前記比較器からの比較結果に従って、実行中の先行命令に続く後続命令の発行可否を判定する発行可否判定回路22と、を有するように構成する。

(もっと読む)

分岐なし高速ベクトル除算計算

単一命令複数データ(SIMD)コンピュータプラットフォームにおいて、倍精度除算/逆数計算ベクトル計算を行うための方法及び方法について説明する。一実施形態において、入力独立変数は、指数部と小数部とで現される。小数部は、スケーリングされ、逆数にされ、そして、乗算されて、入力独立変数の逆数表現が生成される。一実施形態において、指数部を逆数にすることは、指数の符号を変更することにより実行されてもよい。その他の実施形態についても説明される。 (もっと読む)

ベクトル型計算機及びベクトル型計算機の命令制御方法

【課題】ベクトルギャザー命令やベクトルスキャッター命令に対して、動的な追い越し制御が行えるベクトル型計算機を提供する。

【解決手段】最小値最大値判定器21でベクトルギャザー命令又はベクトルスキャッター命令に対するアドレスの依存元命令を実行する固定小数点演算器12の演算結果を用いてベクトル要素の最小値及び最大値を判定する最小値最大値判定し、この最小値及び最大値を最小値/最大値レジスタ部31に保持しておく。ベクトルギャザー命令又は前記ベクトルスキャッター命令を実行する際に、保持されている最小値及び最大値から、前記ベクトルギャザー命令又は前記ベクトルスキャッター命令のアドレスのアクセス範囲を特定し、ベクトルギャザー命令又はベクトルスキャッター命令の追い越し制御を行う。

(もっと読む)

ベクトル処理装置及びベクトル演算処理方法

【課題】ベクトル処理装置内のベクトル演算パイプのデータ入出力を高速化すること

【解決手段】ベクトル演算処理装置内に、ベクトル演算処理を行う複数のベクトル演算パイプ210を設けた少なくとも1以上のベクトル処理ユニット200を備える。ベクトル処理ユニット200内であって、かつ、ベクトル演算パイプ210の外部に前記ベクトル演算パイプに対応する出力用のデータバッファ220、及び入力用のデータバッファ230を設ける。

(もっと読む)

最適化SIMDコードのための動作指示命令の挿入

【課題】 ベクトル化コードの実行時の例外を追跡し示すために指示された命令を挿入するためのメカニズムを提供する。

【解決手段】 コンパイルのために第1のコード(620)の一部分を受信する。第1のコード(620)の一部分を分析して、指定の非投機的動作を実行し、置換動作指示命令(1020)へのベクトル・レジスタ入力内に存在する特殊例外値(840)に対応する任意の例外条件を示すための指示動作をさらに実行する置換動作指示命令による置換の候補である第1のコード(620)内の指定の非投機的動作を実行している非投機的命令を識別する。置換を実行し(1080)、少なくとも1つの非投機的命令の置換に基づいて第2のコード(630)を生成する。コンパイル済みコード(630)を実行しているこのデータ処理システム(100)は、投機的命令が例外条件を生成したことに応答して、例外処理を開始せずに、特殊例外値(840)をベクトル出力レジスタ(1130)に保管するように構成される。

(もっと読む)

並列データ処理装置

【課題】 SIMDアーキテクチャは、システムが多数の相対的に小さいデータ項目グループを処理しなければならないときには非効率となる問題を克服する並列データ処理装置を提供することを目的とする。

【解決手段】 データ処理装置は、処理要素のSIMD(単一命令複数データ)アレイ10を備える。前記処理要素は、複数の処理ブロックに作動可能に分割され、前記処理ブロックは、データ項目のそれぞれのグループを処理するように作動可能である。

(もっと読む)

ベクトル演算装置およびベクトル演算方法

【課題】処理性能の向上したベクトル演算装置を提供すること

【解決手段】ベクトル演算装置1は、複数個のベクトルデータを格納する複数のベクトルレジスタ110、および、ベクトルレジスタ110から出力されるベクトルデータに対し演算を行うベクトル演算器111を有するベクトルパイプ11と、イテレーション演算のk(k:1以上の整数)番目の演算を行うベクトルパイプ11からk+1番目の演算を行うベクトルパイプ11に演算結果を順次並列して供給するパス116と、複数のイテレーション演算を複数のベクトルパイプ11で並列して実行するよう命令発行管理を行う命令発行部102とを備える。

(もっと読む)

並列データ処理装置

【課題】 SIMDアーキテクチャは、システムが多数の相対的に小さいデータ項目グループを処理しなければならないときには非効率となる問題を克服する並列データ処理装置を提供することを目的とする。

【解決手段】 データ処理装置は、処理要素のSIMD(単一命令複数データ)アレイ10を備える。前記処理要素は、複数の処理ブロックに作動可能に分割され、前記処理ブロックは、データ項目のそれぞれのグループを処理するように作動可能である。

(もっと読む)

1 - 20 / 74

[ Back to top ]