Fターム[5B014GD17]の内容

入出力制御 (4,953) | 入出力制御装置(IOC) (351) | CPUの役割分担 (32)

Fターム[5B014GD17]の下位に属するFターム

I/Oの状況管理 (11)

データ処理(データ変換、編集) (13)

Fターム[5B014GD17]に分類される特許

1 - 8 / 8

部分仮想化マシンに基づく統一格納装置

【課題】格納装置の数および種類が増加するにつれて、OS開発の負荷が大きくなることを抑制し、装置ドライバを介して格納装置にアクセスをセキュアなものとする。

【解決手段】物理I/O装置に対応する仮想I/Oコントローラを含む仮想I/O装置をインスタンス化する部分仮想マシンが設ける。部分仮想マシンは、オペレーティングシステムから仮想I/O装置に対するI/O要求を捕捉し、I/O要求がI/O制御要求を含む場合に処理するI/Oコントローラエミュレータと、I/O要求がI/Oアクセス要求を含む場合に処理するI/O装置エミュレータと、I/Oコントローラエミュレータ部およびI/O装置エミュレータ部に結合され物理I/O装置と通信する装置ドライバとを含む。部分仮想マシンは、セキュアエンクレーブセッションにおいて実行され、OSによる部分仮想マシンへのアクセスを抑制する。

(もっと読む)

ディスクリプタ転送装置、I/Oコントローラ、及びディスクリプタ転送方法

【課題】メインメモリとは別に設けられた、高速でアクセス可能なディスクリプタ記憶用の記憶部の容量を上げることなくディスクリプタ転送にかかるレイテンシを下げることを可能とする。

【解決手段】プロセッサ2が、メインメモリ5又はメインメモリ5とは別に設けられたディスクリプタ記憶用の記憶部であるディスクリプタ格納部12にディスクリプタを記憶するとともに、ディスクリプタ転送装置1に対して、ディスクリプタの読み出し元を指示する。そして、ディスクリプタ転送装置1が、プロセッサ2からの上記指示に従って、メインメモリ5又はディスクリプタ格納部12からディスクリプタを読み出し、読み出されたディスクリプタをI/Oコントローラ3に対して転送する。

(もっと読む)

複数のマイクロプロセッサを有するストレージシステム、及び、そのストレージシステムにおける処理分担方法

複数のマイクロプロセッサを備えるストレージシステムにおいて、非同期処理のスループットを確保しつつ、同期処理の非同期処理待ちによるI/Oレスポンスの遅れを防ぐ。

コントローラが有する複数のマイクロプロセッサに、同期プロセッサと、非同期プロセッサが混在する。同期プロセッサは、同期処理を担当し非同期処理を担当しないマイクロプロセッサである。非同期プロセッサは、非同期処理を担当し同期処理を担当しないマイクロプロセッサである。  (もっと読む)

(もっと読む)

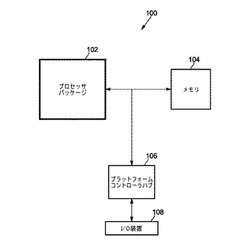

リモートデスクトッププロトコルのためのハードウェアアクセラレーション

オフロードされなければコンピュータシステムのプロセッサおよびメモリで実行されるリモートターミナルサービス処理タスクを周辺機器にオフロードするための方法。一実施形態では、開示される方法は、階層化ネットワークモデルにおいて利用され、一般にはネットワークアプリケーションにおいて実行されるコンピューティングタスクが、代わりにNIC(ネットワークインタフェースカード)などの周辺機器にオフロードされる。  (もっと読む)

(もっと読む)

インターフェース装置

【課題】ASICの再開発を行うことなく新規な通信プロトコルに対応することができるインターフェース装置を提供する。

【解決手段】FlashROM12は、通信プロトコルに従って外部装置と行う通信を制御するためのプログラムを記憶する。出力データバッファ制御回路6及び出力信号同期回路7は外部装置へ送信されるデータと制御信号との同期を制御する。CPU1は、プログラムに従って、外部装置へ送信される制御信号を生成する。

(もっと読む)

半導体デバイス及び半導体デバイスの自動制御方法

【課題】半導体デバイスのレジスタをリアルタイムに制御する。

【解決手段】複数のレジスタと、レジスタを制御する複数のコマンドを格納するコマンドバッファと、コマンドバッファに格納されたコマンドを順次実行するコマンド実行回路と、外部からの制御とコマンド実行回路からの制御を切り替える実行部選択回路と、を含み、アドレスのレジスタのデータからビット幅かつ有効ビットのデータを読み出すデータ読み出しコマンドと、アドレスのレジスタのデータの有効ビットを書き込みデータに書き換えるデータ書き込みコマンドと、外部からのクロック信号の数がクロック数に達するまで待機する単純ウェイトコマンドと、アドレスのレジスタのデータと比較データの有効ビットが等しくなるまで待機する状態ウェイトコマンドと、を含み、複数のコマンドを1つ以上組み合わせてレジスタを制御する。

(もっと読む)

ホストコントローラ、半導体集積回路、及び、ホスト制御方法

【課題】処理速度の向上等が可能なホストコントローラを提供する。

【解決手段】SDMMCホストコントローラ10は、第1のコマンド及び第1のコマンドに続いて発行されるべき第2のコマンドをカードC2に発行する旨の指示をメインCPU2から受けた場合に、第1のコマンドをカードC2に発行し、その後、第1のコマンドに対するレスポンスをカードC2から受けたときに、メインCPU2からの指示を待つことなく、第2のコマンドをカードC2に発行する。

(もっと読む)

入出力制御装置,情報制御装置,入出力制御方法及び情報制御方法

【課題】

プログラマブル電子装置には信頼性を得るために複数のプロセッサで同一処理を実行し、出力が一致することにより信頼性を向上させた。反面複数のプロセッサが常に同一の処理を実行するため、プロセッサ当りの処理性能は半分になる。一方、信頼性を要求しない処理は処理性能を要求し、高信頼と高処理性能の両立は困難であった。このため高信頼用プログラマブル電子装置と、高性能処理用プログラマブル電子装置を分ける必要があった。

【解決手段】

複数のプロセッサを備え、通常の制御やネットワーク処理などは異なるプロセッサで独立に動作させることにより処理性能の向上を図り、信頼性を要求する処理を実行する時のみ、他のプロセッサに割り込みを入れ、同一の高信頼を要求する処理を実行させ、複数のプロセッサ出力が一致することにより、信頼性の向上と処理性能の向上の両立を図り、単一のプログラマブル電子装置で高信頼処理と高性能処理を実現する。

(もっと読む)

1 - 8 / 8

[ Back to top ]