Fターム[5B015KA05]の内容

Fターム[5B015KA05]に分類される特許

1 - 3 / 3

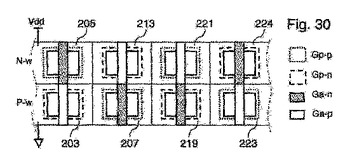

明白に異なる閾値電圧を有するトランジスタを持つSOIから製造する集積回路

本発明は、埋め込まれた絶縁材料面によって半導体基板層から隔てられた活性半導体層を含む集積回路に関する。この集積回路は、同じ型の第1および第2のトランジスタ(205、213)と、第1および第2のトランジスタの真下に配置された第1および第2の接地面とを有し、第1のトランジスタの接地面のドーピングは、第1のトランジスタのソースのドーピングと反対のドーピングであり、第1の閾値電圧を有する。第2のトランジスタの接地面のドーピングは、第2のトランジスタのソースのドーピングと同一のドーピングであり、第2の閾値電圧を有する。第1の閾値電圧は、第1のトランジスタのソースと接地面との間に印加される電位差に依存し、第2の閾値電圧は、第2のトランジスタのソースと接地面との間に印加される電位差に依存する。  (もっと読む)

(もっと読む)

SRAMセルおよび上記SRAMセルに流れ込む漏れ電流の補償方法

SRAMメモリセルが開示されている。このSRAMメモリセルは、少なくとも1つのメモリノード(K1、K2)と、メモリノード(K1、K2)、第1のビット線(BL)、および、第1ワード線(WL1)とに電気的に接続された、少なくとも1つの選択用トランジスタ(M5)を備えている。さらに、このSRAMメモリセルは、SRAMメモリセルに流れ込む漏れ電流を補償する手段(M7、M8)を備えている。この手段(M7、M8)は、漏れ電流に相当する電流が、SRAMメモリセルに流れ込むように構成されている。一実施形態では、本発明に係るこの手段は、第1のビット線(BL)と第2メモリノード(K2)とに電気的に接続されたトランジスタ(M7)として構成され、ここで、第1メモリノード(K1)は、選択用トランジスタ(M5)に接続されている。  (もっと読む)

(もっと読む)

放射線耐性のあるSRAMビット

1つの入力と1つの出力を有する第1インバータと、1つの入力と1つの出力を有する第2インバータとを備える集積回路における放射線耐性のあるSRAM装置。第1抵抗は、第1インバータの出力と第2インバータの入力との間に接続される。第2抵抗は、第2インバータの出力と第1インバータの入力との間に接続される。第1書き込みトランジスタは、第1インバータの出力と接続され、書き込み制御信号の第1セットのソースと接続されるゲートを有する。第2書き込みトランジスタは、第2インバータの出力と接続され、書き込み制御信号の第2セットのソースと接続されるゲートを有する。最後にパストランジスタは第1及び第2インバータのいずれか1つの出力と接続されるゲートを有する。  (もっと読む)

(もっと読む)

1 - 3 / 3

[ Back to top ]