Fターム[5B015PP00]の内容

S−RAM (6,838) | 構造/配置 (382)

Fターム[5B015PP00]の下位に属するFターム

メモリ分割 (119)

ICのレイアウト (130)

ICパッケージ内にSRAM以外のものを組み込むもの (129)

Fターム[5B015PP00]に分類される特許

1 - 4 / 4

メモリ装置

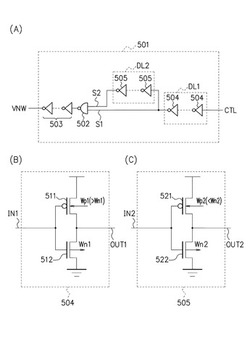

【課題】高速にデータを書き込むことができるメモリ装置を提供することを課題とする。

【解決手段】メモリ装置は、第1及び第2のpチャネルトランジスタと、第1のpチャネルトランジスタ及び第2のpチャネルトランジスタのバックゲートに第2のバックゲート信号を出力するバックゲート信号生成回路(501)とを有し、バックゲート信号生成回路は、第1の遅延回路(DL1)と第2の遅延回路(DL2)とを有し、第1の遅延回路は、第3のpチャネルトランジスタ及び第3のnチャネルトランジスタを含む第1のインバータ(504)を有し、第3のpチャネルトランジスタは、第3のnチャネルトランジスタよりゲート幅が広く、第2の遅延回路は、第4のpチャネルトランジスタ及び第4のnチャネルトランジスタを含む第2のインバータ(505)を有し、第4のpチャネルトランジスタは、第4のnチャネルトランジスタよりゲート幅が狭い。

(もっと読む)

スタティックランダムアクセスメモリ

【課題】第1の導電型の共通ウェルが形成された半導体基板と、前記半導体基板上の前記共通ウェルに行列状に配列されたメモリセルよりなり、列方向に整列して共通のビット線に接続される一群のメモリセルがメモリセルカラムを形成するメモリセルアレイからなるスタティックランダムアクセスメモリにおいて、隣接カラム群間のソフトエラーの伝搬を抑制する。

【解決手段】隣接する第1および第2のカラム群において、前記第1のカラム群CG1で選択される一のメモリセルカラムの第1導電型ウェルPW(01)と、第2カラム群CG2で同時に選択されるメモリセルカラムの第1導電型ウェルPW(05)は、いずれか一方が、共通ウェル11から、第2導電型の深いウェルDNW1により遮断されており、前記第2導電型の深いウェルDNW1は、行方向に測った場合の一つのカラム群の寸法を超えない寸法を有する。

(もっと読む)

半導体装置

【課題】ECC回路を用いつつ面積、消費電力、アクセス時間の増大を改善する。

【解決手段】書き込み動作時において、複数のメモリセルから第1バスに読み出された通常データとパリティービットとを用いて通常データのエラー訂正をエラー訂正回路により行い、該エラー訂正がされた通常データを第2バスに出力する第1動作と、第1動作により訂正された通常データのうち第2バスに転送された書き込みデータに対応したデータ部分を書き込みデータ生成回路により入れ替えて第1バスの通常データ部に出力する第2動作と、第2動作により入れ替えられた書き込みデータを含む通常データを用いてパリティービット生成回路によりパリティービットを生成して第1バスのパリティービット部に出力する第3動作と、第2動作と第3動作とにより第1バスに出力された通常データとパリティービットを複数のメモリセルに書き込む第4動作とを行う。

(もっと読む)

半導体記憶装置

【課題】 通過トランジスタと駆動トランジスタとでゲート長およびゲート幅が相異なると、製造時において管理すべきパラメータの数が多くなるため、半導体記憶装置の製造が煩雑になってしまう。

【解決手段】 SRAMセル1は、インバータ10,20、N型FET(電界効果トランジスタ)32,34,36,38、ワード線42,44、およびビット線46,48を備えている。FET32,34,36,38のゲート幅W2およびゲート長L2はそれぞれ、FET12,22のゲート幅W3およびゲート長L3に等しい。特に本実施形態においては、FET14,24のゲート幅W4およびゲート長L4も、それぞれW2(=W3)およびL2(=L3)に等しい。すなわち、SRAMセル1は、W2=W3=W4、且つL2=L3=L4となるように設計されている。

(もっと読む)

1 - 4 / 4

[ Back to top ]