Fターム[5B016AA02]の内容

位取り記数法を用いた四則演算 (704) | 目的、効果 (145) | ハードウェア削減 (29)

Fターム[5B016AA02]に分類される特許

1 - 20 / 29

内積演算装置および内積演算方法

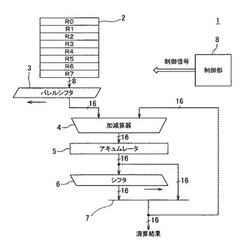

【課題】乗算器を使用しないハードウェア量の少ない演算器構成で、高並列に適したサイクルタイムの高速化が図れるとともに、ROMを用いなくても内積演算が効率よくかつ精度低下なく行うことができる内積演算装置および内積演算方法を提供する。

【解決手段】複数の入力ベクトル要素を格納する入力要素レジスタ2と、定数ベクトル要素の2のべき乗項と入力ベクトル要素との部分積を求めるバレルシフタ3と、部分積の累算を行う加減算器4と、加減算器の累算結果が格納されるアキュムレータ5と、アキュムレータ5に格納された累算途中の結果の切捨てを行うシフタ6と、定数ベクトル要素の最下位の2のべき乗項の同じ項にかかる全ての入力ベクトル要素の部分積の累算を行わせて順次高位の2のべき乗項にかかる部分積の累算を繰り返して最上位の2のべき乗項まで繰り返させる演算制御手段と、を備えている。

(もっと読む)

多倍長演算装置、暗号化装置、復号装置、演算方法、プログラムおよび記録媒体

【課題】 小さな回路規模で高速に多倍長演算を実現する多倍長演算装置を提供すること。

【解決手段】 本発明の多倍長演算装置110は、直列接続される複数の多ビット加算器120を含む。本多ビット加算器120は、各々が多倍長数の一部を構成する被加数および加数が入力される入力部A,Bと、被加数と加数との下位ビットを加算し、和の下位ビットを出力する下位ビット加算器122と、加数の上位ビットが被加数の上位ビットに対する減基数の補数であるという関係を満たすか否かを判定する判定回路124と、被加数および加数の上位ビットを加算する第1上位ビット加算器126と、被加数と加数との上位ビットを加算する第2上位ビット加算器128と、判定の結果に対応して第1上位ビット加算器126または下位ビット加算器122の桁上がりを当該多ビット加算器120の桁上がり出力として選択する選択回路130とを含む。

(もっと読む)

多量子ビット量子演算装置

【課題】装置の複雑化およびデコヒーレンスの増大が抑制できるようにする。

【解決手段】量子状態(量子情報)を保存する複数のメモリ量子ビット101と、メモリ量子ビット101と相互作用することでメモリ量子ビット101と量子状態の交換を行う量子バス102と、量子バス102に結合する量子ビットから構成されて少なくとも1組の量子演算を行う演算量子ビット103と、量子バス102に結合する読み出し量子ビット104と、読み出し量子ビット104の量子状態を読み出す測定器(量子状態測定手段)105と、メモリ量子ビット101の量子状態を制御する制御部106とを備える。

(もっと読む)

定数乗算装置

【課題】装置規模を小型化し、且つ演算速度を高速化することが可能な定数乗算装置を提供する。

【解決手段】2進6桁の被乗数Yの、各桁中に含まれる「1」の個数が4である場合に、12列、3段の複数の加算点を設定し、被乗数Yの最も下の位の「1」が第1桁に存在する場合に、第1段の、第1列から第6列までの加算点の各a入力にN桁の乗数Xの、第1桁から第N桁までの各数値を入力する。また、第2〜第3段の各加算点に、乗数Xを所定の桁だけシフトした数値を入力する。そして、各加算点の3つの入力のうち2以上が常時0となる場合は、この加算点に加算器を設置せず、1つの入力が常時0となる場合にはこの加算点に半加算器(HA)を設置し、それ以外の加算点に全加算器(FA)を設置する。このような構成により、装置規模を小型化し、更に演算速度を高速化することができる。

(もっと読む)

総和計算方法及び数値演算装置

【課題】汎用性を有するNビット幅のレジスタとNビット幅の加算器とでNビット幅の複数の数の総和計算が可能な総和計算方法を提供する。

【解決手段】総和計算方法は、N(2以上の自然数)ビット幅の2進数である複数の数を受け取り、複数の数の同一のビット位置にある1の個数を計数することにより、第n(=1〜N)ビット位置の1の個数を各nに対して求め、複数M(2以上の自然数)個のNビット幅のレジスタにより構成されるN列M行の行列の第n列に、第nビット位置の1の個数を表わす2進数を、第1行が最下位ビットで第M行が最上位ビットとなるように列方向に格納し、第m(=1〜M−1)行のNビット幅のレジスタの最下位ビット以外の格納内容を右(最下位方向)に1ビットシフトして第m+1行のNビット幅のレジスタの格納内容に加算する演算を第1行から順番に第M−1行まで実行することにより総和を求める各段階を含む。

(もっと読む)

演算回路

【課題】 0以上22n−2以下(nは自然数)の数値Xを2n −1で除算する演算回路の提供。

【解決手段】 図3の演算回路は、入力部に入力された0以上22n−2以下(nは自然数)の数値Xの上位nビット(すなわちX/2n )と上記数値Xと2進数の数値1とを加算回路にて加算し、その演算結果の上位nビット(すなわち上記加算結果を2n で割った値)を出力部が出力する。この出力部に出力された数値は、数値Xを2n −1で除算した商とすることができる。

(もっと読む)

半導体装置

【課題】演算の高速化を図り、また、小型化を図ることで並列度を高めることが可能な半導体装置を提供する。

【解決手段】半導体装置201は、乗数を示す3ビットの第1の乗数データを受けて、ブースのアルゴリズムに従い、シフトフラグ、反転フラグおよび演算フラグを出力するデコーダDEC1,DEC2と、被乗数を示す2ビットの第1の被乗数データと、シフトフラグ、反転フラグおよび演算フラグとを受けて、シフトフラグに基づいて第1の被乗数データの上位ビットおよび下位ビットのいずれかを選択し、選択したビットを反転フラグに基づいて反転または非反転し、反転または非反転されたデータおよび所定の論理レベルのデータのいずれかを演算フラグに基づいて選択し、第1の乗数データおよび第1の被乗数データの部分積を示す部分積データとして出力する第1の部分積算出部31〜38とを備える。

(もっと読む)

乗算方法、処理装置および演算器

【課題】効率的な乗算手法を提供する。

【解決手段】本発明の乗算方法は、p+q=k(p、qは自然数)を満たすp、qの2つ以上の組み合わせに対して、pビットの値とqビットの値の積の演算に使用可能なkビットの演算器を用いて、mビットの被乗数xとnビットの乗数yの積を乗算演算する乗算方法である。この乗算方法は、m、n、kの間に所定の条件が成立する場合に、nビットの乗数yを分割して、複数の分割乗数を生成するステップと、複数の分割乗数のそれぞれと、被乗数xの乗算演算を、kビット演算器を用いて実行するステップと、分割乗数のそれぞれと被乗数xとの乗算結果をもとに、被乗数xと乗数yの乗算結果を導出するステップとを含む。

(もっと読む)

許容誤差内の整数除算回路

【課題】ハードウェア経費を削減することができる除算回路の提供。

【解決手段】許容誤差内の整数除算回路である信号処理装置はポインタ、第一の左シフタ、第二の左シフタ、減数器、乗数器、及び右シフタが含まれる。ポインタは除数の最上位ノンゼロビットを求めて、最上位バイト値を出力する。第一の左シフタは、第一の指数計数を生ずる為に最上位バイト値に従ってシフト操作を行う。第二の左シフタは、第二の指数係数を生ずる為に最上位バイト値に従ってシフト操作を行う。減数器は除数、第一の指数係数、第二の指数係数に従って乗数を計算し、乗数を乗数器に出力する。乗数器は入力値を乗数と掛け合わせその結果を右シフタに出力する。右シフタは計算結果を出力する。

(もっと読む)

浮動小数点実行ユニットを用いる回路装置、集積回路装置、プログラム製品、および方法(動的値域調整浮動小数点実行ユニット)

【課題】浮動小数点実行ユニットを提供する。

【解決手段】浮動小数点実行ユニットは、浮動小数点計算のために拡張された値域を動的に提供するために浮動小数点値の仮数ビットの部分集合を付加的な指数ビットして選択的に再利用することができる。浮動小数点オペランドの仮数フィールドは第1および第2部分を含むと考えられることができ、その第1部分は、浮動小数点値の仮数を表すように第2部分と連結されることができ、あるいは、拡張された値域を提供するために、浮動小数点値の指数を表すように浮動小数点オペランドの指数フィールドと連結されることができる。

(もっと読む)

複合加算回路アレイ及びAND/OR面

【課題】全加算回路グループを変更し、所定の数の入力ビットの論理関数を計算する方法を提供する。

【解決手段】前記全加算回路のそれぞれは、第1及び第2データ入力、データ出力、桁上げ入力、及び桁上げ出力を有する。前記全加算回路は相互に接続されて桁上げチェーンを構成する。前記方法は、前記全加算回路のそれぞれの第1の入力を同じ固定値に設定する工程と、前記所定の数の入力ビットをそれぞれ前記全加算回路の第2の入力に接続する工程と、前記全加算回路のアレイからなる桁上げチェーンの出力を前記論理関数の結果として用いる工程とを備える。

(もっと読む)

デジタル信号処理装置

【課題】 DSPの大規模化、消費電力の増加を招くことなく、要求される演算精度での演算処理を実行することができ、かつ、演算サイクルを短縮化する。

【解決手段】 アキュムレータ131と加算器123との間に小数点位置合わせ処理部114を介挿した。これは、アキュムレータ131が出力する累算値データP3とは小数点の位置がずれたデータP2Lが乗算結果レジスタ121から加算器123に供給されるとき、乗算結果レジスタ121の出力データP2Lと小数点の位置を合わせるためのビットシフト処理および0方向丸め処理を累算値データP3に対して施し、加算器123に供給する。従って、加算器123およびアキュムレータ131のビット幅を不要に増加させることなく、倍精度演算を実行することができる。

(もっと読む)

浮動小数点演算装置

【課題】本発明は、従来の浮動小数点積和演算を可能としながら、2つの浮動小数点A、Bの加算(A+B)及び減算(A-B)を並列処理する事ができる浮動小数点演算装置を提供する。

【解決手段】本発明は、2つの浮動小数点A、Bに対する加算(A+B)及び減算(A-B)を並列実行するために、従来の浮動小数点積和演算器(FMA)に加え、浮動小数点加算器を一つ備え、加算(A+B)または減算(A-B)のうちで、いずれかが2ビット以上の左シフト正規化が必要であるかを判定する手段を有し、加算(A+B)または減算(A-B)のうちで、2ビット以上の左シフト正規化が必要でない方の正規化論理を省く事で、性能を2倍に向上し回路規模は2倍未満に抑える。

(もっと読む)

フィルタ演算器及び動き補償装置

【課題】ハードウェア量及び消費電力を削減することができるブースアルゴリズムを利用したフィルタ演算器及び動き補償装置を提供すること。

【解決手段】フィルタ演算器1は、入力データと複数のフィルタ係数からなるフィルタ係数群とをブースアルゴリズムを用いて積和演算する。このため、入力データと隣接するフィルタ係数の差分との乗算を行う2以上のフィルタ乗算ユニット10a〜10dと、隣接するフィルタ乗算ユニットの乗算結果を加算する加算器23とを備える。フィルタ乗算ユニット10b〜10dは、ブースのアルゴリズムに従って繰り返し部分積を生成する部分積生成ユニットと、部分積生成ユニットの出力を累積加算する加算器20とを有する。

(もっと読む)

演算回路及び演算方法並びに情報処理装置

【課題】より少ない回路量で数値的に大きな誤差をもつエラーを効率的に検出する浮動小数点演算回路を提供する。

【解決手段】上記課題を解決するために、浮動小数点演算回路に、第1の演算結果を出力する第1の演算器101と、第2の演算結果を出力する第2の演算器102と、第1の演算結果と第2の演算結果とについて所定ビット幅の比較を行う比較回路103と、を備える。

(もっと読む)

除算装置および除算方法

【課題】少ないハードウェア規模で高速で除算処理を行うこと。

【解決手段】入力制御部1は、除数の正負判定結果を出力制御部5へ出力する一方、除数をSB化して出力する。有効ビット数判定部2は、SB化除数を入力して、そのビット数を判定して、演算テーブル部3および演算処理部4へ出力する。演算テーブル部3は、SB化除数と有効ビット数とを入力し、有効ビット数が有効ビット内である場合、その演算テーブルを参照して、SB化除数の値に対応した商とテーブル使用フラグとを出力する。一方、演算処理部4は、SB化除数と有効ビット数とを入力して、有効ビット数が有効ビット数にないと判定した場合、除算処理を行う。出力制御部5は、演算テーブル部3からのテーブル使用フラグに基づき、演算テーブル部3からのテーブル読出し結果あるいは演算処理部4からの演算処理結果を商として出力する。

(もっと読む)

乗算器及びフィルタ処理装置

【課題】演算速度を維持しつつハードウェア量を削減すること。

【解決手段】フィルタ演算器10は、ブースのアルゴリズムにしがたって入力データと各フィルタ係数とから部分積を生成する部分積生成ユニット1〜4と、部分積を加算する加算器51とを有する。部分積生成ユニットは、部分積生成部1a、1b、1cと、部分積生成部1b、1cと加算器51との間に設けられ、部分積生成部の出力を選択して加算器51に入力するセレクタ14、15と、セレクタ14、15を制御する零検出部f1、g1とを有する。各フィルタ係数は、当該フィルタ係数から生成される符号データの1以上が常に0となるものであって、零検出器f1、g1は、それぞれ部分積生成部1b、1cが零を出力するとこれを検出し、部分積生成部1cの出力を選択さして加算器51に入力させる。

(もっと読む)

乗算装置

【課題】任意の係数を乗算したディジタルデータをサンプル周期で出力する乗算装置において、複数のディジタル信号同士の加算が必要となる場合にも、新たな記憶素子等の増加による回路規模の増大を回避する。

【解決手段】任意の係数を乗算したディジタルデータをサンプル周期で出力する乗算器を含む乗算装置であって、ディジタルデータと1サンプル前の乗算出力とを加算して乗算器に供給する加算器304と、乗算器の出力を加算器304へ帰還させるスイッチ302とを備える。

(もっと読む)

ブース乗算方法及びシステムのための電力効率の良い符号拡張

ディジタル信号プロセッサの設計及び使用のための技術であって、通信(例えば、CDMA)システムにおける伝送を処理することを含む。ブース乗算方法及びシステムのための電力効率の良い符号拡張は、ブース乗算ツリーに符号ビットを適用することを含む。符号ビットは、ブース乗算処理が符号拡張ステップを実行することを可能にする。これは、事前に決められた部分積行の正しい符号を保存するために符号ビットを使用してブース乗算ツリーの事前に決められた部分積行を1要素拡張することをさらに含む。この符号拡張ビットは、キャリー−アウト列中に置かれて、ブース乗算処理の積を拡張する。次に、方法及びシステムは、ブース乗算ツリーの事前に決められた列に置かれた符号ビットにキャリー−アウト値を加算することによってブース乗算ツリーから最終積を形成する。この結果は、符号を有する最終積のサム成分を効率的に拡張しそして最終積のキャリー成分をゼロ−拡張することである。  (もっと読む)

(もっと読む)

ダイナミック回路

【課題】ダイナミック回路において、評価制御トランジスタを省略してトランジスタのスタック段数を削減するとともに評価制御トランジスタの省略に伴う初期化動作時の貫通電流の発生を抑制する。

【解決手段】ダイナミック回路は、ダイナミックノード(10)、複数の入力信号についての論理評価結果に応じてダイナミックノード(10)の充電状態を変化させる評価回路(30)、評価回路(30)のレプリカ回路(403)による論理評価結果に応じて論理レベルが変化する制御信号を出力する制御回路(40)、制御回路(40)及び外部からそれぞれ制御信号を受け、これら制御信号に従ってダイナミックノード(10)の初期化の開始及び停止を制御する初期化回路(20)を備えている。

(もっと読む)

1 - 20 / 29

[ Back to top ]