Fターム[5B018MA40]の内容

記憶装置の信頼性向上技術 (13,264) | 対象 (1,668) | その他 (5)

Fターム[5B018MA40]に分類される特許

1 - 5 / 5

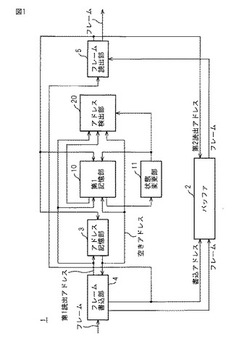

フレーム処理装置及びフレーム処理方法

【課題】バッファの空きアドレスを格納するアドレス記憶部から読み出す値に異常が生じたときに発生するバッファのリソースの低減を防止する。

【解決手段】フレーム処理装置1は、バッファ2の空きアドレスを記憶するアドレス記憶部3と、巡回アドレスによって読出アドレスを指定することによりアドレス記憶部3から読み出した空きアドレスへフレームを書き込むフレーム書込部4と、バッファ2の各アドレスの使用状態を記憶する第1記憶部10と、バッファ2にフレームを書き込むときフレームが書き込まれるアドレスについて第1記憶部10に記憶される使用状態を変更する状態変更部11と、巡回アドレスが一巡する期間に亘って書込処理が行われず、かつ未使用であると第1記憶部10に記憶されるアドレスを検出するアドレス検出部20を備える。

(もっと読む)

メディア処理装置に備えられた不揮発性メモリの書込み制御方法、メディア処理装置及び不揮発性メモリ書込みシステム

【課題】ホストコンピュータのアプリケーションが把握している不揮発性メモリに記憶されている装置固有の情報を更新する、更新固有情報を受信した場合でも、不揮発性メモリの書込み可能回数を超えない範囲の書込み処理を実行可能にする。

【解決手段】メディア処理装置10の稼動時間や、該装置10内の各可動部分の可動回数などをメンテナンスカウンタ情報として不揮発性記憶部65に書込む場合や、該装置10では管理できずホストコンピュータ100でのみ管理されて、それから送られてくるディスクの発行枚数などのメンテナンスカウンタ情報を受信してメンテナンスカウンタ情報記憶部65に書込む際に、”書込み可能回数”或いは”書込み済回数”を参照して、書込み寿命を超えて書込みを行わないようにした。これにより、不揮発性記憶部65が書込み不能であるにもかかわらず、メディア処理装置10がメンテナンスカウンタ情報の書込み処理を実行してしまうといった危険な動作を行うのを防止することが可能となる。

(もっと読む)

セルフテスト機能のあるメモリコントローラ及びそれをテストする方法

【課題】メモリコントローラのデータ及びデータタイミング信号をフィードバックして短時間内にメモリコントローラをテストする。

【解決手段】セルフテスト機能を追加したメモリコントローラはテストモードでテストデータを生成するテスト制御部、データ読み取りタイミング信号を生成し、データ読み取りタイミング信号に同期して生成されたテストデータとデータ読み取りタイミング信号を出力するデータ伝送部及び出力されたテストデータ及び出力されたデータ読み取りタイミング信号をデータ伝送部にフィードバックするデータ入出力部を含む。データ伝送部はフィードバックされたデータ読み取りタイミング信号に基づいてフィードバックされたテストデータを復元し、テスト制御部は復元されたテストデータと生成されたテストデータとを比較してテストを実施する。

(もっと読む)

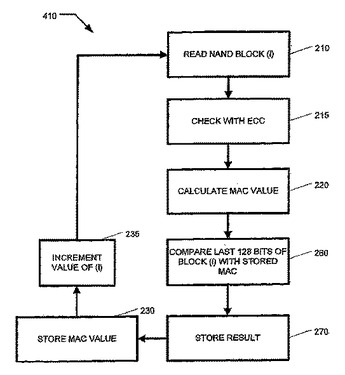

メモリカードコントローラファームウェアのハードウェアドライバ完全性チェック

メモリシステムは、コントローラのハードウェアにおいて実施される暗号化エンジンを備える。メモリシステムを起動する際に、ブートストラップ機構が実施され、ファームウェアの第1の部分が、実行時に実行すべきファームウェアの他の部分をプルインする。暗号エンジンのハードウェアは、ファームウェアの少なくとも第1の部分の完全性をベリファイするために使用される。したがって、システムを実行することになっているファームウェアのみが実行されることになる。  (もっと読む)

(もっと読む)

プログラマブル・デバイスの構成エラー検出の偽陽性の低減

【課題】プログラマブル・デバイスの不必要な再ロードと再構成を避けるために偽陽性ソフト・エラーを検出する装置と方法を提供すること。

【解決手段】デバイスが、マスキング・ユニットと感度マスク・データを使用して、メモリの未使用部分をエラー検出計算から除し、偽陽性メモリ・エラー検出を低減させる。デバイスは、メモリからデータを読み取り、データ保全性を検証するエラー検出ユニットを含む。感度マスク・データがメモリの未使用部分を示す。メモリの未使用部分はプログラマブル・デバイスの未使用部分に関する構成データに対応する。感度マスク・データの各ビットがメモリからのデータの1つまたは複数のビットの使用状態を示す。マスク・データに応答して、マスキング・ユニットが、メモリの未使用部分からのデータを、エラー検出計算の結果を変更しない値に設定する。これによって、メモリの未使用部分からのデータのすべてのエラーが、エラー信号を出さなくなる。

(もっと読む)

1 - 5 / 5

[ Back to top ]