Fターム[5B018RA13]の内容

記憶装置の信頼性向上技術 (13,264) | エラーの種類 (442) | アドレス (19)

Fターム[5B018RA13]に分類される特許

1 - 19 / 19

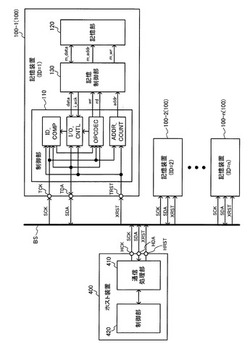

記憶装置、ホスト装置、回路基板、液体容器及びシステム

【課題】アクノリッジを送受信し、且つ、書き込み処理時間を短縮することができる記憶装置、ホスト装置、回路基板、液体容器及びシステム等を提供すること。

【解決手段】記憶装置100は、バスBSを介して接続されるホスト装置400との通信処理を行う制御部110と、ホスト装置400からのデータが書き込まれる記憶部120と、記憶部120のアクセス制御を行う記憶制御部130とを含む。制御部110は、バスBSに接続される複数の記憶装置100のうちのm(mは1以上の整数)個の記憶装置100に対するホスト装置400によるデータの書き込み期間の終了後に、ホスト装置400からのID情報を受信し、且つ、自身の記憶部120にホスト装置400からのデータが正常に書き込まれている場合に、ホスト装置400に対してアクノリッジを返信する。

(もっと読む)

メモリ書き込み確認装置、メモリ書き込み確認方法およびプログラム

【課題】データの正常性だけでなく、書き込みアドレスの正常性も確認する。

【解決手段】書き込み部11は、メモリ12にデータを書き込み、計算部13は、書き込み部11がメモリ12に書き込んだデータのデータ・チェックサム値とデータを書き込んだアドレスのアドレス・チェックサム値とを計算し、データ・チェックサム値とアドレス・チェックサム値を合計したチェックサム合計値を計算する。表示部14は、データ・チェックサム値とチェックサム合計値を表示する。

(もっと読む)

電子装置、及び、これを用いた電動パワーステアリング装置

【課題】アドレスバスおよびデータバスの故障を検出する電子装置において、故障検出に係る処理負荷を低減し処理速度を向上する。

【解決手段】電子装置は、CPUとROMとを接続しアドレスを伝送する4つ以上のバスラインからなるアドレスバス21を備える。電子装置は、アドレスバス検査用アドレスAdによって指定されるROM領域13aから値を読み出し、読み出した値から計算した判定値Vjと予め計算されたアドレスバス検査用正解値Vtとを比較し、一致しない場合、アドレスバス21が故障していると判定する。アドレスバス検査用アドレスAdは、4つ以上のバスラインに対応する4ビット以上の値であって、2ビット以上の0の値と2ビット以上の1の値とを有する値を含み、複数のバスライン間の短絡故障を同時に検出可能である。これにより、故障検出に必要な検査用アドレスAdの数を低減することができる。

(もっと読む)

フレーム処理装置及びフレーム処理方法

【課題】バッファの空きアドレスを格納するアドレス記憶部から読み出す値に異常が生じたときに発生するバッファのリソースの低減を防止する。

【解決手段】フレーム処理装置1は、バッファ2の空きアドレスを記憶するアドレス記憶部3と、巡回アドレスによって読出アドレスを指定することによりアドレス記憶部3から読み出した空きアドレスへフレームを書き込むフレーム書込部4と、バッファ2の各アドレスの使用状態を記憶する第1記憶部10と、バッファ2にフレームを書き込むときフレームが書き込まれるアドレスについて第1記憶部10に記憶される使用状態を変更する状態変更部11と、巡回アドレスが一巡する期間に亘って書込処理が行われず、かつ未使用であると第1記憶部10に記憶されるアドレスを検出するアドレス検出部20を備える。

(もっと読む)

メモリー制御装置およびプログラム並びにメモリー制御方法

【課題】論理物理変換テーブルに何らかの異常が生じてもデータアクセスを可能とする。

【解決手段】フラッシュメモリーの各物理ブロックの先頭に設けられた管理データ領域にインデックス情報(論理アドレス)を記録しておき、ホスト側から論理アドレスの指定を伴ってコマンドを受信した場合に論理アドレスを論理物理変換テーブルを参照して物理アドレスに変換し(S120)、物理アドレスが示す物理ブロックの管理データ領域からインデックス情報を読み出して論理物理変換テーブルが正常か否かを判定し(S130,S140)、正常でない場合には各物理ブロックの管理データ領域からインデックス情報を読み出して論理物理変換テーブルを修復すると共に(S150)、論理アドレスを修復した論理物理変換テーブルを参照して物理アドレスに変換し物理アドレスが示す物理ブロックにアクセスしてコマンドに応じた処理を実行する(S120〜S160)。

(もっと読む)

伝送装置及びリンク切れ修復方法

【課題】 複数のセグメント間を連結するポインタに生じたビットエラーを正しい値に復元し、チェーンメモリーのリンク切れを修復することができる伝送装置及びリンク切れ修復方法を提供する。

【解決手段】 伝送装置100は、エラーポインタのビットパターン及び反転パターンの排他的論理和を演算し、真のポインタを含むポインタ候補を算出するポインタ予測部50を備えている。また、ポインタ候補が示すポインタ格納領域11aに格納された前ポインタとエラーポインタが格納されたポインタ格納領域11aのアドレスとの一致の有無を判定するポインタ検証部70を備えている。また、ポインタ検証部70による判定結果に基づき、エラーポインタを、一致した前ポインタが格納されるポインタ格納領域11aのアドレスであるポインタ候補に変換するポインタ復元部80を備えているものである。

(もっと読む)

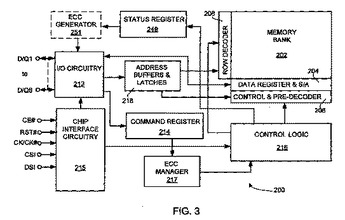

エラー検出方法および1つまたは複数のメモリデバイスを含むシステム

1つまたは複数のメモリデバイスを含むシステムと、エラーの検出および訂正の方法とが開示される。システムのメモリデバイスが、パケットを受信するための入力を含む。パケットの第1の部分は、少なくとも1つのコマンドバイトを含むことが可能であり、パケットの第2の部分は、コマンドエラー検出を容易にするパリティビットを含むことが可能である。メモリデバイスは、パリティビットに基づいて、エラーが少なくとも1つのコマンドバイト内に存在するかどうかを検出するように構成されているエラーマネージャと、パケットをエラーマネージャに供給するように構成されている回路とを含むことが可能である。  (もっと読む)

(もっと読む)

アドレスバスのテスト方法及びテスト装置

【課題】アドレスバスとデータバス夫々のバス幅の相対的な関係に依存せずにアドレスバスのテストをすること。

【解決手段】複数のメモリセルを有するメモリ装置20へ伝送される複数ビットのアドレスパタンの伝送路であるアドレスバス15aのテスト方法は、次のステップを含む。全ビットが第1論理値であるアドレスパタンにより特定されるメモリセルに対して第1論理値を書き込み、あるビットがその他の全てのビットとは異なり第2論理値である複数のアドレスパタン夫々により特定されるメモリセルに対して第1論理値を書き込み(S1)、第1のアドレスパタンにより特定されるメモリセルに対して第1論理値とは異なる値の第2論理値を書き込み(S5)、第2のアドレスパタンにより特定され、かつ第1論理値が読み出されるべきメモリセルからの第2論理値の読み出しに基づいてアドレスバスの不良を検出する(S4)。

(もっと読む)

セキュアメモリインターフェース

【課題】セキュアメモリインターフェースを提供すること。

【解決手段】セキュアメモリインターフェースは、セキュアモードが活性化された場合に、メモリ装置に対する欠陥注入を探知するように読出部、書込部、及びモード選択部を含む。モード選択部は、データプロセッシング部から生成されたメモリアクセス情報を使用してセキュアモードを活性化または非活性化する。従って、データプロセッシング部はメモリ装置に保存されたセキュアデータの量と位置を柔軟に指定することができる。

(もっと読む)

アドレスエラー検出装置、アドレスエラー検出方法

【課題】メモリ回路のアドレスデコード部で発生する障害を高確率で検出できる小面積のアドレスエラー検出装置およびアドレスエラー検出方法を提供する。

【解決手段】Xデコーダ103の出力から複数ビットの冗長符号を生成するX符号化器105と、Yデコーダ104の出力から前記冗長符号と同じビット数の冗長符号を出力するY符号化器106と、X符号化器105の出力10とY符号化器106の出力11を各ビット排他的論理和するXOR回路107と、XOR回路107の出力12とアドレス信号1を入力し、誤り検出を行う誤り検出器108と、を備える。X符号化器105とY符号化器106、およびXOR回路107によって、アドレス信号をハミング符号化した冗長部12を生成する。誤り検出器108では、元のアドレス信号と生成された冗長符号に対して検査行列の掛け算を行い、エラーが発生したか否かを検出し、エラー出力3を得る。

(もっと読む)

半導体記憶装置

【課題】論理アドレスの指定を間違えた場合でも、アドレス領域を超えてメモリがアクセスされることがない半導体記憶装置を提供する。

【解決手段】データを記憶するメモリ部と、外部から供給された論理アドレスをメモリ部の物理アドレスに変換する機能を有し、メモリ部の読み出し及び書き込みを制御するメモリコントローラと、を備え、 メモリコントローラは、外部から供給された論理アドレスがメモリ部のアドレス領域を超えたときにアドレス領域エラーを外部に通知するものである。

(もっと読む)

メモリ制御装置

【課題】アドレスに関して2ビット以上のエラーを検出することができるメモリ制御装置を提供する。

【解決手段】上位装置から指定されるアドレスをBankアドレス、Rowアドレス、Columnアドレスに分割し、時分割多重されて供給されるRowアドレスとColumnアドレスそれぞれについて別々にパリティビットを生成し、両パリティビットとデータとに基づいてチェックビットを生成する。これにより、RowアドレスとColumnアドレスのいずれか一方に1ビットエラーが発生した場合に加えて、さらに、RowアドレスとColumnアドレスの両方にビットエラーが発生した場合も、2ビットエラーとして検出することができる。

(もっと読む)

メモリコントローラおよびメモリ制御方法

【課題】メモリ2重化システムにおいて、障害情報に対してリアルタイムに対処するとともに、アドレス線のエラーを推定することでシステムダウンを防止することを課題とする。

【解決手段】LDX#1およびLDX#0は、それぞれが所持するECC情報(ECCチェックのための情報)を交換してECCチェックを行い、リクエストデータの一部についてそれぞれECC(Error Correcting Code)チェックを行って、アドレス線にエラーが発生しているか否か推定する。具体的には、例えば、LDX#0は、リクエストデータの一部に関するECCチェック結果であるシンドローム(診断情報)を作成し、このシンドロームから把握されるリクエストデータの一部に関するエラーの状況に応じて、例えば、リクエストデータの大部分がアンコレクタブルエラーを起こしている場合には、アドレス線にエラーが発生しているものと推定する。

(もっと読む)

半導体記憶装置及び半導体記憶装置機能検査方法並びに半導体記憶装置を有する電子機器

【課題】 半導体記憶装置及び半導体記憶装置を有する電子機器のアドレス、データバス、システムバスの検証に乱数で作成したアドレス、データを使用することで、クロストーク、ノイズの影響によるデータ化けを精度よく検出する。

【解決手段】 半導体記憶装置Aー1、Aー2、A―XXX,B−1、B−2、B―XXX,X−1、X−2、X−XXXに擬似乱数発生器2で書込まれた乱数アドレスのデータを書込むと共に半導体記憶装置Aー1、Aー2、A―XXX,B−1、B−2、B―XXX,X−1、X−2、X−XXXに書き込まれた乱数アドレスのデータを読出し、書込みデータと読出しデータは比較手段を介して比較することで特定のビット配列で生ずる機能障害を検出する半導体記憶装置及び半導体記憶装置機能検査方法並びに半導体記憶装置を有する電子機器を提供する。

(もっと読む)

記憶装置、メモリ管理装置、メモリ管理方法及びプログラム

【課題】 アドレス変換テーブルの変更動作中に異常が発生しても以後の読み書き動作が正常に行える記憶装置等を提供することである。

【解決手段】 フラッシュメモリ11は、ブロックの物理アドレスと論理アドレスとの対応関係を表すBPT(Block Pointer Table)を、現在のもの及び過去のものについて記憶する。コントローラ12はユーザデータを書き込む際、ユーザデータ書き込み後の新たな現在のBPTを空きブロックに書き込む場合は、当該空きブロックがBPTの格納に利用された順序、1個前のBPTの位置、前にBPTの格納に利用されていたブロックが不良ブロックであるか否か、を示す各情報を新たなBPTに含める形でBPTを更新する。次回の初期化時は、これらの情報に基づいて現在のBPTの訂正等を行い、また、これらの情報のいずれかが欠けていた場合は、残る情報に基づいて、現在のBPTの内容を特定する。

(もっと読む)

CAM装置およびCAM制御方法

アドレスに対応する複数のタグを複数のエントリに、パリティビットおよび該パリティビットを反転させた反転ビットを記憶するタグ部(12a)と、複数のエントリに対応させて複数のデータを複数のエントリに記憶するデータ部(12b)と、検索用アドレスとタグ部(12a)の各エントリとを比較する比較器(200〜2031)と、比較結果で複数一致であるマルチヒットが発生した場合、当該複数のエントリの記憶内容のオアをとり、オア後のパリティビットおよび反転ビットに基づいて、マルチヒットの発生原因を判定する判定部(112)とを備えている。  (もっと読む)

(もっと読む)

メモリアクセスエラーの検出及び/又は訂正方法、並びにこの方法を実行するための電子回路構成

メモリ(4)内に、保護対象のデータ(D)の他に、このデータ(D)を用いて生成したチェックデータ(P)を保存している、プロセッサシステムでのメモリアクセスエラーを検出及び/又は訂正するための方法は、誤り検出及び訂正時において特に高い信頼性を達成可能な形態に改善することが求められている。このために、この発明では、チェックデータ(P)の生成の際に、保護対象のデータ(D)の他に、そのアドレスをも考慮している。  (もっと読む)

(もっと読む)

マージバッファのシステムキルエラーのプロセスキルエラーへの変換技術

【課題】 本発明の課題は、上記問題点に鑑み、マージバッファのシステムキルエラーをプロセスキルエラーに変換する方法、装置及びシステムを提供することである。

【解決手段】 上記課題を解決するため、本発明は、データ及び該データが格納されるアドレスを有し、1以上のプロセスに係るストア命令を収集するバッファと、第1プロセスに係るストア命令を、前記バッファが第2プロセスに係るストア命令を収集する前に前記バッファから常にドレイン処理するバッファ制御とから構成されることを特徴とする装置を提供する。

(もっと読む)

電気機器

【課題】 バックアップメモリの信頼性を向上させることができる電気機器を提供する。

【解決手段】 データ書込部11は、バックアップメモリ40内におけるアドレスデータをバックアップデータに付加してバックアップメモリ40に書き込み、データ読出部12は、バックアップデータを読み出す前にアドレスデータを読み出し、バックアップメモリ40の読み出し先のアドレスと、読み出されたアドレスデータとを比較し、両アドレスが一致する場合、バックアップデータを読み出す。

(もっと読む)

1 - 19 / 19

[ Back to top ]