Fターム[5B022DA10]の内容

Fターム[5B022DA10]に分類される特許

1 - 8 / 8

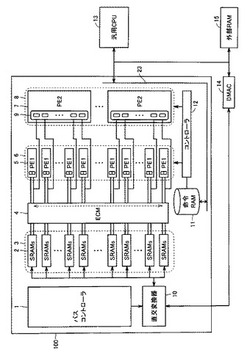

データ処理装置およびそのデータ処理方法

【課題】可変長データに対する演算処理と、固定長データに対する演算処理とを効率的に行なうことが可能なデータ処理装置を提供すること。

【解決手段】データ処理装置100は、SIMD方式の複数のPE1(5)と、複数のPE1(5)のそれぞれに対応して設けられる複数のSRAMs2と、複数のPE2(7)とを含む。複数のPE1(5)のそれぞれは、対応する1つのSRAMs2に格納されるデータに対して演算を行なう。また、複数のPE2(7)のそれぞれは、対応する複数個のSRAMs2に格納されるデータに対して演算を行なう。したがって、複数のSRAMs2を共有することができ、可変長データに対する演算処理と、固定長データに対する演算処理とを効率的に行なうことが可能となる。

(もっと読む)

単一のTAP(テストアクセスポート)を介して複数のTAPにアクセスするための方法、および集積回路

【課題】本発明は、単一のTAP(テストアクセスポート)を介して複数のTAPにアクセスする集積回路を提供する。本来は別々のICで使用されるように設計された、種々の再使用可能なICの一部やモジュールの制御およびテストを統合できるようにする。

【解決手段】第1複製状態マシン(26)と第2複製状態マシン(28)をそれぞれ用いることによって、第1状態マシン(20)と第2状態マシン(22)のいずれも修正することなく、第1状態マシン(20)と第2状態マシン(22)を個別にテストする。

(もっと読む)

半導体信号処理装置

【課題】低消費電力かつ小占有面積で高速に論理演算および算術演算処理を実行することのできる半導体信号処理装置を提供する。

【解決手段】ユニット演算子セル(UOE)を、複数のSOIトランジスタで構成し、この少なくとも2つのSOIトランジスタのボディ領域(SNA,SNB)に書込データを格納し、これらの記憶用のSOIトランジスタ(NQ1,NQ2)を直列にまたは単独に読出ポート(RPRTBまたはRPRTA)に結合する。これにより、ユニット演算子セルの記憶データのAND演算結果またはNOT演算結果を得ることができ、データの書込/読出だけで演算処理を行なうことができる。

(もっと読む)

動的再構成プロセッサ

【課題】実行するアプリケーションによって処理性能が大きく変わることなく、ゲート規模やゲート利用率の観点から効率のよい動的再構成プロセッサを得る。

【解決手段】再構成可能演算部3は、積和演算部と並べ替え部とパターンマッチ/換字部と論理演算部のうち少なくとも一つの演算部を有し、かつ、その演算部における入力から出力に至る論理経路が選択可能に構成されている。演算制御部1は、再構成可能演算部3の論理経路情報を演算制御メモリ4に書き込み、再構成可能演算部3は、演算制御メモリ4に記憶された論理経路情報に基づいて、使用する演算部とその論理経路が設定される。

(もっと読む)

論理比較動作を実行するための方法と装置

【課題】

【解決手段】

本発明は、パックド・データおよびアンパックド・データに基づいて、論理比較および分岐のための命令をプロセッサに実行させるための方法および装置に関する。実施例において、プロセッサは、メモリに接続される。メモリは、第1のデータおよび第2のデータを格納する。プロセッサは、第1および第2のデータの論理比較を実行する。論理比較は、第1および第2のデータの各ビットに実行されてもよく、または特定のビットだけに実行されてもよい。少なくとも1つの実施例において、少なくとも、第1のデータはパックド・データエレメントを含む。論理比較はパックド・データエレメントの最上位ビットに実行される。論理比較は、第1および第2のデータの同じそれぞれのビットの比較を含む。更に、第1のデータのビットと第2のデータの対応ビットの補数との論理比較を含む。これらの比較に基づいて、分岐サポートが実行される。かかる分岐サポートは1つ以上のフラグの設定を含む。そして、それは分岐ユニットによって次々に利用されてもよい。あるいは、分岐サポートは、示された目的コード位置への分岐を含んでもよい。  (もっと読む)

(もっと読む)

演算処理装置および演算処理プログラム

【課題】ベクトルプロセッサにおいて、回路規模の増大を抑制しつつ、飽和機能を持つ命令を高速に処理する。

【解決手段】 加減算/シフトユニットA25または加減算/シフトユニットB26で加算処理がそれぞれ行われる時に、飽和処理部25a、26aは、ステータスレジスタ22のSビットを参照し、Sビットが“1”の時、加減算/シフトユニットA25または加減算/シフトユニットB26にて得られた加算結果がオーバーフローまたはアンダーフローしているかどうかをそれぞれ判断し、加減算/シフトユニットA25または加減算/シフトユニットB26にて得られた加算結果がオーバーフローしている場合、その加算結果として“0x7FFFFFFF”を出力するとともに、加減算/シフトユニットA25または加減算/シフトユニットB26にて得られた加算結果がアンダーフローしている場合、その加算結果として“0x80000000”を出力する。

(もっと読む)

ディジタル情報複製管理装置

【課題】 簡易な構成でありながら、データ記憶装置に記憶されているデータの不正コピーを強固に抑制する。

【解決手段】 CPU10とHDDコントローラ14との間はバス18によって接続され、HDDコントローラ14とハードディスクドライブ19との間はバス22a、論理回路部110、およびバス22bによって接続されている。ここで、論理回路部110はHDDコントローラ14側が出力したビットデータを反転してハードディスクドライブ19に供給するものであり、これによりハードディスクドライブ19には本来のデータと異なるビットデータのデータとして記録される。

(もっと読む)

決定性有限オートマトン(DFA)処理

到着するパケットデータで決定性有限オートマトン(DFA)グラフをリアルタイムで走査するプロセッサ110を提供する。プロセッサは、少なくとも1つのプロセッサコア120と、この少なくとも1つのプロセッサコア120と非同期に動作するDFAモジュール134とを有し、キャッシュコヒーレントメモリ130,108に格納されたパケットデータでノンキャッシュメモリ118に格納された少なくとも1つのDFAグラフを走査する。 (もっと読む)

1 - 8 / 8

[ Back to top ]