Fターム[5B033AA04]の内容

Fターム[5B033AA04]に分類される特許

1 - 20 / 47

情報処理装置、情報処理方法、及びプログラム

プロセッサ、及びプロセッサの制御方法

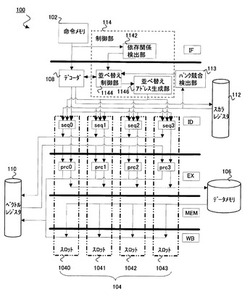

【課題】複数のパイプラインを有するプロセッサにおいて、処理効率を低下させることなくバンク競合を回避する。

【解決手段】メモリの複数のバンクに第1のバンクアクセス順序でアクセスする第1の処理部と、前記第1の処理部のアクセスの開始に続いて第2のバンクアクセス順序で前記複数のバンクにアクセスを開始する第2の処理部と、前記第1の処理部及び前記第2の処理部による前記複数のバンクへのアクセスが競合する場合に、前記第2のバンクアクセス順序を前記競合が生じない第3のバンクアクセス順序に並べ替えて前記第2の処理部を前記複数のバンクにアクセスさせる制御部とをプロセッサに備えることで、処理効率を低下させることなくバンク競合を回避できる。

(もっと読む)

ベクトル処理装置、ベクトル処理方法、及び、プログラム

【課題】命令パケットを制御することにより処理性能を向上させるのに好適なベクトル処理装置等を提供する。

【解決手段】命令パケットバッファ部11b2は、スカラプロセッシング部11により発行される第1の命令パケットを格納する。アドレス比較・バッファ制御部11b1は、第1の命令パケット及び第1の命令パケットの後に発行される第2の命令パケットの種類を判別し、第1の命令パケットが指定する第1のアドレスと第2の命令パケットが指定する第2のアドレスとを比較し、第1及び第2の命令パケットを結合する指示を出力する。アドレス比較・バッファ制御部11b1は、第1の命令パケットの命令がスカラストア命令であり、第2の命令パケットの命令がスカラストア命令であって、第1及び第2の命令パケットのアドレスが一致する場合、結合処理部11b3に結合する指示を出力し、結合処理部11b3は、第1及び第2の命令パケットを結合する。

(もっと読む)

演算処理装置

【課題】ストライド命令の後続命令に対してもチェイニングを行って性能を向上することができる演算処理装置の提供を図る。

【解決手段】同時アクセス可能な複数のメモリブロックbank0〜bank3を有するデータメモリ2との間でデータを遣り取りする複数のベクトルパイプライン121〜124を有する演算処理装置であって、前記データメモリに対するストライドアクセスを、基本パターンのデータサイズを決める第1パラメータと、該基本パターンにおける有効なデータ数を決める第2パラメータで規定する。

(もっと読む)

プロセッサ

【課題】逐次実行部(RISCプロセッサ100)の処理と並列実行部(VLIWコプロセッサ200)の処理とを効率良く融合させる。

【解決手段】RISCプロセッサ100において同時にフェッチされた4つの命令のうち第2番目と第4番目の命令の特定フィールドが命令プリデコーダ170によってプリデコードされる。この特定フィールドはオペコードフィールドと同時発行命令数フィールドを含む。オペコードフィールドがVLIWコプロセッサ命令を示す場合、プログラムカウンタ管理部110は同時発行命令数フィールドに応じてプログラムカウンタの増分値を制御する。VLIWコプロセッサ200では同時発行命令数フィールドに応じた並列度によりVLIWコプロセッサ命令が実行される。

(もっと読む)

独立ロード/ストア機構およびそのための命令を実行するための方法、システム、およびコンピュータ・プログラム

【課題】

【解決手段】独立ロード/ストア命令は、CPUによって実行された場合、2つの独立メモリ位置からのオペランドにアクセスし、2つのオペランドが、他のCPUからのオペランドへの介入ストアなしに、ブロック同時インターロック・フェッチを使用してアトミックにアクセスされたように見えるか否かを示すように、条件コード・インジケータを設定する。独立ペア・ロード形式の命令では、アクセスはロードであり、独立データは汎用レジスタに格納される。

(もっと読む)

非アラインドメモリアクセス予測

【課題】命令実行パイプラインにおけるメモリアクセス命令のミスアライメントを早期に予測する。

【解決手段】複数のメモリアクセス命令のミスアラインメントを予測し、追加のマイクロ操作を実効アドレス生成に先立って生成する。該追加のマイクロ操作は、所定のアドレス境界を横切る範囲に入るメモリにアクセスする。追加のマイクロ操作を生成して追跡するのに十分なパイプライン制御資源が利用可能であることが保証され、実効アドレス生成時にそれら資源が利用可能でない場合のパイプラインフラッシュを回避する。ミスアラインメント予測は、フラッグ、二重モードカウンタ、局所プレディクタ、広域プレディクタおよび統合プレディクタなど、既知の条件付分岐予測技術を使用することができる。ミスアラインメントプレディクタは、メモリアクセス命令フラッグまたはミスアラインド命令タイプによって使用可能にされてもよいし、あるいはバイアスされてもよい。

(もっと読む)

データをシャッフルするための方法及び装置

【課題】効果的にデータをシャッフルするための方法及び装置を提供すること。

【解決手段】一実施例の方法は、L個のデータ要素を有する第1オペランドとL個の制御要素を有する第2オペランドとを受け取ることからなる。各制御要素に対して、当該制御要素により指定された第1オペランドデータ要素からのデータは、それのゼロクリアフィールドが設定されていない場合に関連付けされた結果のデータ要素位置にシャッフルされ、それのゼロクリアフィールドが設定されていない場合、関連付けされた結果のデータ要素位置にゼロが配置される。

(もっと読む)

バウンダリ実行制御システム、バウンダリ実行制御方法、及びバウンダリ実行制御プログラム

【課題】 ベクトルストア命令実行時におけるバウンダリ生成と後続のスカラロード命令の発行制御を高速化し、かつハードウェア量を削減することを目的とする。

【解決手段】 本発明のバウンダリ実行制御システムは、キャッシュと、キャッシュに対してスヌープ処理を行うスヌープ処理回路と、バウンダリチェック回路とを備える。バウンダリチェック回路は、複数のデータを並行して格納する命令であるベクトルストア命令の実行時に、更新するアドレスの最小値および最大値の少なくともいずれか一方をバウンダリとして記憶するとともに、最小値と最大値との排他的論理和演算の結果からマスクを生成し、キャッシュに対するスカラロード命令の発行要求時に、バウンダリとマスクとに基づいて、スヌープ処理の完了を待たずにスカラロード命令の発行を許可するか否かを判定する。

(もっと読む)

制御装置

【課題】デバイス種別と該デバイス種別のデータ配列の先頭からの相対アドレスとを指定してデータを要求する外部装置に対して該当するデータを返すことができる制御装置を得ること。

【解決手段】夫々の分断されたデータ配列が配置されるデバイス記憶部の夫々記憶領域について、該データ配列のデバイス種別と、該データ配列の分断される前のデータ配列における先頭からのオフセットと、記憶領域の先頭の絶対アドレスと、記憶領域の領域サイズと、を記述するアドレス変換テーブルを備える。

(もっと読む)

データプロセッサ

【課題】広い範囲から容易にデータのプリフェッチを行うことができるデータプロセッサを提供する。

【解決手段】中央処理装置(2)は、命令実行によって所望の値が設定可能にされるレジスタ(BR)の値にオフセットを加えてデータの実効アドレスとする所定の命令を実行可能であり、メモリ(6)に格納された一部の命令列及びデータ列を保持するバッファ(5)は、前記命令列及びデータ列を格納するキャッシュメモリ(IC,DC)を有し、前記キャッシュメモリに前記所定の命令を格納したとき、当該命令で指定される実効アドレスのデータを含むデータ列を前記メモリから前記キャッシュメモリにプリフェッチする。フェッチした命令列の中から前記所定の命令を見つけ出してデータ列のプリフェッチを行うからデータプリフェッチの操作が容易であり、PC相対ロード命令に比べて広い範囲からデータプリフェッチを行うことができる。

(もっと読む)

プロセッサ

本出願は、全体の圧縮構造体を読み出し解凍する必要なく、メモリ内の圧縮構造体にランダムにアクセスする方法を提供する。  (もっと読む)

(もっと読む)

プロセッサ、レジスタアクセス方法およびレジスタアクセスプログラム

【課題】レジスタスピル処理が発生してもプログラムの実行速度の低下を防ぐことのできるプロセッサの提供。

【解決手段】本実施の形態にかかるプロセッサでは、物理レジスタ120のうち、レジスタリネーミングによって論理レジスタ110との対応付けがされていない物理レジスタに、論理レジスタ:Lレジスタ0に格納されている値を格納する。物理レジスタ120のうち、PレジスタXXは、論理レジスタとの対応付けがされておらず、“空いた”状態である。したがって、論理レジスタ:Lレジスタ0に格納されている値を物理レジスタ:PレジスタXXに格納し、待避命令の処理が完了する。また、このとき待避命令に記述されていたアドレスXと物理レジスタ:PレジスタXXとが対応付けられたことを対応表140に反映させる。

(もっと読む)

プログラマブルコントローラ

【課題】データメモリのスタック領域への高速アクセスができる。

【解決手段】インストラクションレジスタ12〜14とマイクロコード処理機能を有し、アプリケーションデータ格納用メモリ(DM)2にスタック領域を持たせ、メモリ(DM)に対するアドレス制御は、そのスタック領域をアクセスするためのスタックポインタ(SP)20とアドレスポインタ(DP)22をマルチプレクサ21で選択する。この選択には前記メモリ(DM)のアドレス選択コマンドと該メモリ(DM)へのリードコマンドを同時に出力する。

(もっと読む)

演算処理装置

【課題】本発明は、命令キャッシュメモリからフェッチした、リピートブロック(反復実行する命令コード群)を含む命令コードを実行するマイクロプロセッサにおいて、プログラム中のリピートブロックを実行する場合に余計な電力の消費を抑制できるようにする。

【解決手段】たとえば、プログラム中のリピートブロックの実行時、リピートブロックの最初の反復により、リピートブロックの先頭にプログラム実行が戻るタイミングから、リピートバッファ14上にリピートブロックの先頭からの命令コードの格納を開始する。リピートバッファ14への命令コードの格納を終了した後は、リピートブロックの反復により、リピートブロックの先頭にプログラム実行が戻るたびに、命令フェッチユニット18にリピートバッファ14から命令コードを供給する構成とされている。

(もっと読む)

テーブル内のエレメントのアドレスを決定するシステムおよび方法

特定の実施形態では、メモリに記憶されたテーブル内の位置を識別するために単一の命令を実行することを含む方法が開示される。この単一の命令は第1のレジスタからビットフィールドデータを抽出すること、およびこのビットフィールドデータを第2のレジスタのインデックス部に挿入することをプロセッサによって実行可能である。第2のレジスタはテーブルアドレス部およびインデックス部を含む。テーブルアドレス部はテーブルに関連するメモリ位置を識別するテーブルアドレスを含む。テーブルアドレスおよびビットフィールドデータは結合してテーブル内のエレメントへのインデックスされたアドレスを形成する。  (もっと読む)

(もっと読む)

データ処理装置およびデータ処理方法

【課題】アクセラレータでの実行速度を高速化したデータ処理装置およびデータ処理方法の提供を図る。

【解決手段】プロセッサと、メインメモリと、ローカルメモリを有するアクセラレータと、を具備するデータ処理装置であって、前記プロセッサで実行されているプログラムの分岐履歴およびメモリアクセス履歴を取るプロファイルユニット5を備え、前記プログラムの前記分岐履歴(ST2)および前記メモリアクセス履歴(ST3)に基づいて、前記アクセラレータが前記ローカルメモリを利用するように、該アクセラレータの合成(ST5)および前記プログラムの変更(ST6)を行うように構成する。

(もっと読む)

エイリアスアドレス指定を用いる可変長命令コード化の実装

デジタルプロセッサおよび動作の方法は、エイリアスアドレス空間を利用し、レガシープロセッサ上で可変長命令コード化を実装する。方法は、メモリにコードシーケンスの命令を格納することと、コードシーケンスの命令アドレスを生成することと、命令アドレスにおける、第1のアドレス空間と第2のアドレス空間との間の移行に応答して、第1の動作モードと第2の動作モードとを自動的に切り替えることであって、第1のアドレス空間および第2のアドレス空間におけるアドレスは、共通のメモリ空間にアクセスする、ことと、第1の動作モードにおいて、第1のアドレス空間において命令にアクセスすることと、第2の動作モードにおいて、第2のアドレス空間において命令にアクセスすることと、コードシーケンスのアクセスされた命令を実行する、こととを包含する。第1および第2の動作モードにおいて、異なる命令長の命令が利用され得る。  (もっと読む)

(もっと読む)

プロセッサ及びプリフェッチ制御方法

【課題】本来の処理命令の実行に対する影響を抑えつつ、複数のキャッシュブロックを転送する。

【解決手段】本プロセッサは、実行ユニットとキャッシュとキャッシュブロックを主記憶からキャッシュに転送する主記憶制御部とキャッシュブロックの転送指示を主記憶制御部に出力するマルチブロックプリフェッチ制御部とを有する。そして、実行ユニットは、プログラム内の所定の処理の前に挿入された第1prefetch開始命令を実行し、プリフェッチ対象領域情報を含む第2prefetch開始命令をマルチブロックプリフェッチ制御部に出力する。また、マルチブロックプリフェッチ制御部は、第2prefetch開始命令を受信した場合、当該命令に含まれるプリフェッチ対象領域情報とキャッシュブロックの大きさとに基づき、転送すべき複数のキャッシュブロックを特定し、複数のキャッシュブロックを所定の処理の実行時間内で転送するようにスケジューリングし、転送指示を出力する。

(もっと読む)

データ処理装置

【課題】メモリに格納されたリングバッファのデータ構造を持つ系列データであるリングバッファ系列データの転送を高速化することができるデータ処理装置を提供する。

【解決手段】リングバッファ系列データを格納するメモリ2と、1または複数のデータを対象として演算を行う演算器5と、前記演算器5の演算対象データまたは前記演算器5の演算結果データを格納するレジスタ8と、前記メモリ2と前記レジスタ8との間のデータ転送を制御するデータ転送制御部1とを有するデータ処理装置100であって、前記リングバッファ系列データのデータ転送に関する制御情報を格納するリングバッファ転送制御レジスタ3を有し、前記データ転送制御部1は、前記リングバッファ転送制御レジスタ3の内容に従い前記リングバッファ系列データのデータ転送を行う。

(もっと読む)

1 - 20 / 47

[ Back to top ]