Fターム[5B033BD00]の内容

機械語命令の実行 (2,093) | ビット操作、各種演算命令 (94)

Fターム[5B033BD00]の下位に属するFターム

単一ビットの判定、操作 (9)

比較 (8)

シフト、回転、変換、アラインメント (30)

ビット、バイド、ワード演算 (31)

定数処理、固定データ発生 (6)

Fターム[5B033BD00]に分類される特許

1 - 10 / 10

2次元マトリクス処理のためのレジスタ

【課題】SIMDマルチメディア処理を効率的に実装するために、複数の関連データ・アイテムを単一のMMXレジスタ内に配置する。

【解決手段】プロセッサがレジスタの二組のセットを有し、第1のセットはデータのマトリクスをストアし、第2のセットは、データのマトリクスの転置されたコピーをストアする。第1のセットのいずれかの行のいずれかの部分が変更されたとき、第2のセット内の転置されたコピーの対応する列の部分が自動的に変更される。データのマトリクスをレジスタの第1のセットにストアし、レジスタの第1のセットは第1の数のレジスタを有し、各レジスタは第1の数のストレージ・ユニットを含み、各ストレージ・ユニットはマトリクスの要素をストアし、レジスタの第2のセット内に転置するステップであって、レジスタの第2のセットは第2の数のレジスタを有し、各レジスタは第2の数のストレージ・ユニットを包含する。

(もっと読む)

信号処理プロセッサ及び半導体装置

【課題】複数のデータ語長に対応したビットリバース処理を効率良く行える信号処理プロセッサ及び半導体装置を提供すること。

【解決手段】本信号処理プロセッサ100は、アドレス・レジスタ122と、アドレスデータに基づくメモリアクセスの対象となるデータの属性情報をアドレス・レジスタに関連付けて記憶する属性情報保持部124と前記デコード信号と、前記アドレス・レジスタに記憶されるアドレスデータに基づいてアクセスアドレスを生成し、メモリにアクセスするメモリアクセス部170を含み、メモリアクセス部170は、アクセスアドレスの所与の範囲のビットを所定の規則に従って入れ替えるビットリバース処理を行うビットリバース処理部141、161を含み、前記アクセスアドレスに対応した前記アドレス・レジスタに関連付けて記憶されている前記属性情報に基づいて、ビット入れ替え対象となる前記所与の範囲を制御する。

(もっと読む)

プロセサおよび情報処理装置

【課題】コンディションコードの数による制限を受けずに条件付きストア命令を実行できるプロセサを提供すること。

【解決手段】条件データを浮動小数点レジスタそのものに格納し、該条件データに基づいて、ストアデータをキャッシュにストアするか否かを判定する条件付き浮動小数点ストア命令を演算部が実行する。

(もっと読む)

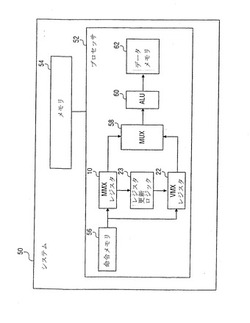

アライメントまたはブロードキャスト命令を含むマルチメディア・コプロセッサの制御メカニズム

【課題】マルチメディア・コプロセッサの制御メカニズムを提供する。

【解決手段】プロセッサに基づくシステム22はメイン・プロセッサ24およびコプロセッサ26を含む。コプロセッサ26はコプロセッサ26によって実行されるデータ処理動作を指定するオペコードおよびコプロセッサ命令のためのターゲット・コプロセッサを識別するためのコプロセッサ識別フィールドを含む命令を扱う。2つのビットがバイト(8ビット),ハーフ・ワード(16ビット),ワード(32ビット)およびダブル・ワード(64ビット)を含む4つのデータ・サイズのうちの1つを示す。他の2ビットは飽和タイプを示す。

(もっと読む)

2つの独立した差分絶対値和を生成するための命令

単一の命令を受信するとき、2つの独立した差分絶対値和(SAD)演算(505、705)を実行するための方法および装置が提供される。2つの演算は並列で実行され得る。演算は2個のソースレジスタ(405、410)内に記憶された値を処理して、結果はデスティネーションレジスタ(425)に記憶される。ソースレジスタおよびデスティネーションレジスタはそれぞれ2つの独立したアクセス可能な区分を有し、それにより、第1のSAD演算(401)は第1の区分にアクセスすることが可能であり、一方、第2の独立したSAD演算(402)はレジスタの第2の区分に同時にアクセスすることが可能である。第1のSAD演算は、ソースレジスタの第1の区分内の値に関して実行され、結果はデスティネーションレジスタの第1の区分に記憶されている。第2のSAD演算は、ソースレジスタの第2の区分内の値に関して実行され、結果はデスティネーションレジスタの第2の区分に記憶されている。値は画素値を含み得る。  (もっと読む)

(もっと読む)

付加情報処理装置、情報処理装置、及び、記憶装置

【課題】 柔軟に処理を変更可能であり、さらに、効率的な演算処理、特に累算処理を実現可能な付加情報処理装置等を提供する。

【解決手段】 ALU27とデータメモリDM31を有する基本処理部3に付加される付加処理部5であって、ALU27と並列して演算を実行可能な加算器29と、ALU27及び加算器29の演算結果に基づいてアクセスが行われるテンプレートメモリTM33及びサーチエリアメモリSM35を備え、ALU27の演算結果に基づくDM31へのアクセスとALU27及び加算器29の演算結果に基づくTM33及びSM35へのアクセスが切り替えられる。

(もっと読む)

SIMDデータ処理システムにおける結果区分化

単一命令複数データ(SIMD)を構築するプロセッサ(2)において、単一データ処理命令は、対応する入力値よりさらにデータ幅が大きい複数の独立した結果値を生成するために、複数の独立した入力値に対してSIMDタイプ処理を実行するような処理ロジック(4,6,8,10)を制御するように機能する。適切に制御された乗算器の形式において再区分器は、これらの結果データ値を、独立したレジスタ(38,40)に格納される上位ビット部分及び下位ビット部分に区分するように機能する。結果値を保持された必要とされるSIMD幅は、別の処理が必要とせずに、所望の上位結果レジスタ(38)又は下位結果レジスタ(40)から読み出される。さらに、全結果の保持は、そのような重複拡張累積演算など、正確な改良を促進する。  (もっと読む)

(もっと読む)

演算処理装置

【課題】算術演算におけるキャリーの伝播遅延を抑制し高速な算術演算処理を実行することができる演算処理装置を得ること。

【解決手段】ALU1はプロセッサから入力された通常の2進数のデータを格納している複数のレジスタ31−1〜31−mのデータを用いて論理演算処理および算術演算処理を実行して演算結果をレジスタ31−1〜31−mに格納し、ALU2はレジスタ31−1〜31−mに対応付けられて符号変換部5によって符号変換が施された剰余数系のデータを格納している複数の変換レジスタ41−1〜41−mのデータを用いて論理演算処理および算術演算処理を実行して演算結果を変換レジスタ41−1〜41−mに格納し、変換レジスタ41−1〜41−mに格納されているデータをプロセッサに出力する際には、剰余数系のデータに逆符号変換を施して通常の2進数に変換した後に出力する。

(もっと読む)

浮動小数点数演算回路

【課題】 浮動小数点数演算回路において効率的に演算対象データを供給する。

【解決手段】 Wビット幅の命令はメモリ200からロードストアユニット110を介して命令デコーダ120に供給される。命令中に即値として埋め込まれたNビット幅のデータは変換回路130によりFビット幅の浮動小数点数に変換され、浮動小数点数の演算器140による演算対象となる。変換回路130において変換されたデータまたは演算器による演算結果はセレクタ150を介してレジスタファイル170に格納される。変換回路130はNビット幅の整数をFビット幅の浮動小数点数に変換する整数変換器300とNビット幅の浮動小数点数をFビット幅の浮動小数点数に変換する浮動小数点数変換器400とを備えて、Nビット幅のデータをFビット幅の浮動小数点数に変換する。

(もっと読む)

SIMD命令をサポートするプログラマブルデータ処理回路

データ処理回路は、SIMD命令を有する命令セットを有する命令実行回路を有する。命令実行回路は、SIMD命令に応答して、N個の各自の同一の処理を実行するよう構成される複数の算術回路を有する。SIMD命令は、第1レジスタと第2レジスタとの選択を規定する。SIMD命令は、アドレス指定されたレジスタからのSIMD命令のN個の各自のSIMD命令オペランドの第1及び第2系列を規定する。各算術回路は、SIMD命令の実行時、第1及び第2系列からそれぞれ各自の第1オペランドと各自の第2オペランドとを受け付ける。命令実行回路は、部分的に重複するように、第1及び第2系列を選択するよう構成される。好ましくは、少なくとも1つの系列のオペランドのポジションは、好ましくは、オペランドデータの制御の下、プログラム制御下にある。好ましくは、プログラムコントロールは、第1レジスタのスタートに関して系列のスタートを選択し、当該系列は、第1レジスタのスタートにおいてスタートしない場合、第2レジスタにおいて実行される。

(もっと読む)

(もっと読む)

1 - 10 / 10

[ Back to top ]