Fターム[5B033BE01]の内容

Fターム[5B033BE01]に分類される特許

1 - 20 / 32

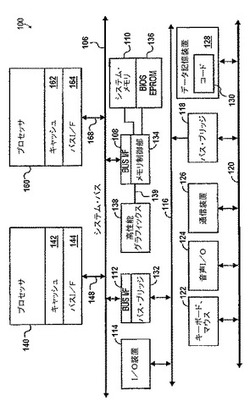

複数のデータ・エレメントの収集及び分散

【課題】複数のデータ・エレメントの収集及び分散におけるオーバーヘッドを低減するプロセッサを提供する。

【解決手段】効率的なデータ転送処理は、単一の命令が複数のデータ・エレメントに対する第1の記憶域と第2の記憶域との間の転送処理を指定し、プロセッサ装置140,160によりデコードする段階、前記プロセッサ内の演算実行部による実行のために単一の命令を発行する段階、単一の命令の実行中に例外の発生を検出する段階、及び該例外に応答して、該例外を分配する前に、未解決のトラップ又は割り込みを例外ハンドラに分配する段階、により達成されうる。

(もっと読む)

プロセッサ

【課題】ソフトウェアを用いることなく、割り込み処理によるオーバーヘッドのない、メモリコピーが可能なプロセッサを提供する。

【解決手段】データを記憶する第1のデータ記憶手段19と、第1のデータ記憶手段からデータがコピーされる第2のデータ記憶手段20と、前記第1のデータ記憶手段から前記第2のデータ記憶手段への前記データ全体のコピーを、不可分処理として実行させるコピー命令が記憶された第1の命令記憶手段18と、データに対し施す処理の処理命令が記憶された第2の命令記憶手段13と、データ全体のコピーを実行しながら、前記第2の命令記憶手段から読み出した前記処理命令を前記データに施し、第2のデータ記憶手段に記憶することで、データコピーとデータに対する処理を並行に実行する制御手段14とを有し、制御手段は、前記データ全体のコピーが完了すると、前記第1のデータ記憶手段の前記コピー命令の次の命令から実行を再開する。

(もっと読む)

文字列転送命令を用いて文字列連結関数の動作を行う方法及びプログラム

【課題】RXCコンパイラが用意する文字列操作をおこなう標準ライブラリ関数strncatに対して、直接に文字列操作命令であるSMOVUを当てはめて、strncat関数のオブジェクトサイズを増やすことなく、実行サイクル数を大幅に削減する。

【解決手段】演算処理装置が、連結先アドレスR1、連結元アドレスR2、及び、連結する文字サイズR3を入力データとし、連結先アドレスR1に文字サイズR3を加算することにより、転送後の末尾のアドレスR4を得るとともに、前記文字サイズR3に1を加算し、転送後の末尾のアドレスR4、連結元アドレスR2、及び、1を加算された文字サイズを入力データとして、文字列転送命令を実行し、実行後、1を加算された文字サイズ分全て転送できたか否かを判断し、全て転送できた場合に転送後の末尾の文字に'\0'を上書きする。

(もっと読む)

独立ロード/ストア機構およびそのための命令を実行するための方法、システム、およびコンピュータ・プログラム

【課題】

【解決手段】独立ロード/ストア命令は、CPUによって実行された場合、2つの独立メモリ位置からのオペランドにアクセスし、2つのオペランドが、他のCPUからのオペランドへの介入ストアなしに、ブロック同時インターロック・フェッチを使用してアトミックにアクセスされたように見えるか否かを示すように、条件コード・インジケータを設定する。独立ペア・ロード形式の命令では、アクセスはロードであり、独立データは汎用レジスタに格納される。

(もっと読む)

プロセッサに関するロード/移動及び複製命令

【課題】単一命令複数データ(SIMD)技術により高度のメディア、画像処理及びデータ圧縮アプリケーションの性能を向上する。

【解決手段】プロセッサに、フェッチ/復号化手段と、算術論理演算ユニット(ALU)及び汎用レジスタ群を含む実行コアに加え、マルチメディア拡張(MMX)レジスタ58およびSIMD拡張命令(SSE及びSSE2)レジスタ60を備える。マルチメディア拡張レジスタ58は64ビットのパック・バイト、ワード、及びダブルワードの整数に対する単一命令複数データ(SIMD)演算をサポートする。SIMD拡張命令レジスタは拡張マルチメディア(XMM)データ・レジスタ84及びMXCSRレジスタ86を含む。SIMD拡張命令レジスタは128ビットのパック単精度並びに倍精度浮動小数値及び128ビットのパック・バイト、ワード、ダブルワード及びクワドワード整数に対するSIMD演算をサポートする。

(もっと読む)

シーケンス検出又は命令に関連付けられた情報に基づいた命令の最適化性能

一実施形態において、本発明は、入力命令及び経路選択信号を受信可能であり、経路選択信号に応じて、入力命令を第1命令コード又は第2命令コードにデコードする命令デコーダを含む。同一の入力命令を表す2つの異なる命令コードを使用することにより、実行ユニットは、異なるデータ長に対して最適化されたオペレーションを実行してもよい。その他の実施形態についても記載、及び特許請求される。 (もっと読む)

情報処理装置

【課題】CPUと拡張演算器を備える情報処理装置において割込み命令が発生した時に、少ない専用命令数で必要なデータ全てを退避させる。

【解決手段】「GETACX Dm,Dn」という1つの専用命令で全てのレジスタからのデータの退避を実現する。Dmは、汎用レジスタ104から第1データ入力バス120に出力される値であり、拡張演算器110の各演算機はそれぞれ自己の値を認識している。Dmが自己を指定する値の場合に各演算機は自己内部のレジスタに格納されているデータをセレクタ116に出力する。拡張演算器情報出力回路117は、拡張演算器110に搭載されている演算器の個数の情報を記憶しており、第1データ入力バス120の値がその数値を上回るとフラグレジスタ102に「1」を出力し、CPU100はフラグレジスタ102の値が「1」になっていることを以ってレジスタからのデータの対比が終了したことを認識する。

(もっと読む)

ブロック転送命令実行装置およびブロック転送方法

【課題】 命令格納メモリの容量消費を抑え、処理時間の短い転送を実現すると共に、演算処理を行ったデータを転送することができるブロック転送命令実行装置を提供する。

【解決手段】 命令ゲート回路10と、カウンタ9と、ソースアドレス加算器6と、デスティネーションアドレス加算器7と、ブロック転送命令実行中は前記命令ゲート回路10にゲーティング指令を出力し、カウンタ9が0になるまで、1個ずつデータ転送の実行を演算器5に指令し、1個のデータ転送を行うごとにカウンタ9の値を−1すると共に次のデータを指示できる値の加算指令をソースアドレス加算器6およびデスティネーションアドレス加算器7に出力するブロック転送制御回路8を備える。

(もっと読む)

プロセッサ及びプリフェッチ制御方法

【課題】本来の処理命令の実行に対する影響を抑えつつ、複数のキャッシュブロックを転送する。

【解決手段】本プロセッサは、実行ユニットとキャッシュとキャッシュブロックを主記憶からキャッシュに転送する主記憶制御部とキャッシュブロックの転送指示を主記憶制御部に出力するマルチブロックプリフェッチ制御部とを有する。そして、実行ユニットは、プログラム内の所定の処理の前に挿入された第1prefetch開始命令を実行し、プリフェッチ対象領域情報を含む第2prefetch開始命令をマルチブロックプリフェッチ制御部に出力する。また、マルチブロックプリフェッチ制御部は、第2prefetch開始命令を受信した場合、当該命令に含まれるプリフェッチ対象領域情報とキャッシュブロックの大きさとに基づき、転送すべき複数のキャッシュブロックを特定し、複数のキャッシュブロックを所定の処理の実行時間内で転送するようにスケジューリングし、転送指示を出力する。

(もっと読む)

マイクロコンピュータ

【課題】転送すべきデータ長が予め決まっていないブロックデータのデータ転送処理効率を向上させたマイクロコンピュータを提供する。

【解決手段】マイクロコンピュータ10は、命令をデコードする実行制御部101と、実行制御部101の命令デコード結果に基づいて演算処理を実行するALU704と、汎用レジスタファイル703と、ALU704による汎用レジスタ703とデータメモリ72との間のデータ転送命令の実行に応じて汎用レジスタファイル703の格納データが所定の識別コード(NULL文字)であるか否かを検出する検出回路110とを備える。

(もっと読む)

半導体集積回路

【課題】CPUの演算器の入出力であるレジスタファイルへのメモリからの演算データの供給、もしくはCPUの演算器の演算結果をレジスタファイルからのメモリに格納するに際して、CPUの負荷を軽減すること。

【解決手段】MPU1のCPU2は、メインプロセッサ6と、SIMD型の演算器ALU0…ALU3を含むコプロセッサ3と、ALU0…ALU3の演算データを格納するレジスタファイル4と、ダイレクトメモリアクセスコントローラ(DMAC)15とで構成されている。CPU2の指示に応答してDMAC15は、4と外部メモリ18の間で演算データをDMA転送して、CPU2の負担を低減する。DMAC15によりDMA転送される演算データは、演算のためのソース・データと演算結果とである。特に、DMAC15は、4内部でALU演算データを格納する任意のレジスタを指定するレジスタファイルDMA転送レジスタ154を含む。

(もっと読む)

情報処理装置

【課題】 メモリとプロセッサ間のデータ転送とプロセッサ内の演算実行を分離して互いに独立に実行することによってデータ転送の最適化を図り、性能向上、消費電力の削減、および、処理部の特定用途または汎用のハードウェア化を容易にする。

【解決手段】 メモリと大容量レジスタファイル間のデータ転送においてプログラムによって必要な時期に必要なデータのみを転送するロードストア部と、大容量レジスタファイルのデータを使用して生成されたデータを大容量レジスタファイルへ書き戻す処理部と、同期フィールドの各種同期を実行する同期機構で構成する。これらが同期をとりながら独立に並列動作することによって、メモリと大容量レジスタファイル間のデータ転送が間断なく行われて、処理の効率化が可能となり、この目的を達成する。

(もっと読む)

演算プロセッサとモータ制御装置

【課題】回路の遅延を減らして高速動作ができるとともに、各種の命令を扱うことができる拡張性のある演算プロセッサとこれを用いたモータ制御装置を提供する。

【解決手段】命令格納メモリ(102)と、命令列制御部(103)と、演算器(106)と、レジスタ群(105)とを備えた演算プロセッサ(101)において、アクセス要求(107)とアドレス入力(108)とデータ入力(109)を入力し外部追加命令を命令セレクタ(119)へ出力する命令構成部(118)と、外部追加命令(122)と命令格納メモリ(102)からの信号を入力し命令列制御部(103)へ出力信号を出力する命令セレクタ(119)と、出力レジスタ(120)と、命令列制御部からの演算コード(113)と即値(114)とレジスタ群(105)からのソースデータ(110)とを入力しレジスタ群(105)へレジスタデータ(112)をレジスタ群(105)と出力レジスタ(120)へ出力する演算器(106)とを備えたものである。

(もっと読む)

データロード方法及びデータ処理装置

【課題】連続したデータを使用する命令を実行する際にメインメモリもしくはデータキャッシュに使用したいデータがない場合、使用したいデータを要求することによって生じる命令の処理速度の低下を防止する。

【解決手段】連続した複数個のデータを使用する命令を実行するときに、使用する可能性のある連続するデータを1回のキャッシュフィルによって持ってこられる量単位に分割してキャッシュフィルすると共にキャッシュフィルの境界にあるデータに対応する命令(境界命令)をまず実行する。次いで、連続するデータに対応する命令(要素命令)を実行中に次の境界命令によってデータのキャッシュフィルを行う。

(もっと読む)

データ処理装置

【課題】論理的・物理的規模の増大を最小限とし、データ処理速度を向上する。

【解決手段】命令中のディスプレースメント(基準アドレス)と、汎用レジスタ(ER0〜ER7)に割当てられるインデックスレジスタが保有する情報とから実効アドレスを計算するアドレッシングモードを設ける。メモリをアクセスするサイズに応じて、バイトであればインデックスレジスタの値を×1とし、ワードであれば×2というようにシフトする。実効アドレスの計算に、前記拡張およびシフトを含むことにより、命令数を削減し、実行ステート数も短縮できる。配列の大きさは、アドレス空間の大きさより小さいから、汎用レジスタの上位を、別のデータレジスタとして使用し、汎用レジスタに配置できるデータの量を増加でき、メモリとのリードライトの回数を削減することによって、命令数を更に削減し、プログラム容量を削減することができる。

(もっと読む)

半同期メモリ・コピー動作において用いられるアドレス範囲の妥当性

【課題】半同期的なメモリ・コピー命令の実行において、 メモリ・ページの内容を保護する。

【解決手段】 メモリ・ページの内容を保護するためのシステム、方法、及びプログラムが開示される。この方法は、半同期メモリ・コピー動作の開始を判断することを含む。半同期メモリ・コピー動作が実施されるアドレス範囲が判断される。ページ・テーブル・エントリの削除に関する発行された命令が検出される。この方法は、発行された命令が、アドレス範囲内の少なくとも1つのアドレスに関連付けられたページ・テーブル・エントリを削除するように予定されているか否かを判断することを更に含む。発行された命令がページ・テーブル・エントリを削除するように予定されていることに応答して、半同期メモリ・コピー動作が完了するまで、発行された命令の実行が停止される。

(もっと読む)

効率的かつ柔軟なメモリ・コピー動作

【課題】メモリ・コピー動作のあいだにプロセッサが後続の命令を実行し続けられるようなメモリ・コピー動作を提供し、不必要なプロセッサ・ダウンタイムを回避する。

【解決手段】半同期メモリ・コピー動作実行のためのメモリ・コピー命令を受信するステップを含む。半同期メモリ・コピー動作は、フラグ・ビットを設定することによりメモリ内のソース位置に対応する仮想ソース・アドレス及びメモリ内のターゲット位置に対応する仮想ターゲット・アドレスに関する妥当性の一時的な永続性を保つ。メモリ・コピー命令は、少なくとも仮想ソース・アドレス、仮想ターゲット・アドレス、及びコピーされるバイト数を識別する標識を含む。メモリ・コピー命令は、メモリ・コントローラによりメモリ・コピー動作を実行するために、メモリ・コントローラに結合されたキューに入れられる。後続の命令が命令パイプラインから利用可能になったときの実行が続行される。

(もっと読む)

情報処理装置

【課題】細切れの小さいサイズの連続したアドレス空間しかない場合でも多くのペリフェラルを使用することを可能にする。

【解決手段】周辺装置の処理を行う処理部130と、複数のブロックに分割されたメモリ140と、前記メモリへのアクセス信号に基づきアクセス対象となるメモリのブロックを特定して前記メモリに対するアクセス処理を行うメモリアクセス処理部とを含み、前記メモリアクセス処理部は、アクセス対象となるメモリのブロックアドレスを保持するブロックアドレス格納レジスタと170、172、アクセス対象となるブロックアドレスを特定してブロックアドレス格納レジスタに設定するブロックアドレス制御部120、150、160と、ブロックアドレス格納レジスタの値に基づきアクセス対象となるメモリのブロックを特定して前記メモリに対するアクセス処理を行うように制御するアクセス制御部120、150、160とを含む。

(もっと読む)

プロセッサ・コプロセッサシステム

【課題】 プロセッサとコプロセッサの処理におけるバスラインへの過負荷とコプロセッサの設計の複雑さを回避して、様々な機能を有するコプロセッサの設計や追加を容易にする。

【解決手段】 このプロセッサ・コプロセッサシステムは、第1のレジスタファイルを有し、プログラム命令列を実行するプロセッサ10と、第2のレジスタファイル及び演算器を有し、第2のレジスタファイルに格納されたデータに対して所定の演算を行うと共に、演算結果を第2のレジスタファイルに格納するコプロセッサ20とを含み、プロセッサ10が、当該プロセッサ単独で実行される命令の他に、コプロセッサと協調して、第2のレジスタファイルをデータのソース及びデスティネーションとして演算器において演算を行う演算命令と、データの転送を行うための第1〜第4の転送命令とを実行する。

(もっと読む)

データ処理装置及びレジスタ・ファイルとメモリとの間でデータ値を転送する方法

データ処理装置及びレジスタ・ファイルとメモリとの間でデータ値を転送する方法が提供される。データ処理装置は、データ値に対してデータ処理演算を実行するように働くデータ処理ユニットと、データ処理ユニットによってアクセスするデータ値をストアするように働く複数のレジスタを有するレジスタ・ファイルとを含む。データ処理ユニットは、単一転送命令に応答して、レジスタ・ファイルのレジスタの対応する複数のものとメモリ中の連続したデータ値アドレスとの間で複数のデータ値の転送を実行する。単一転送命令は、そこから連続したデータ値アドレスを取り出すアドレス識別子を提供し、データ値の転送の各々に対して、複数のレジスタのうちのそのデータ値の転送の対象であるレジスタを指定するレジスタ識別子を提供する。更に、データ値の転送の各々に関するレジスタ識別子は、データ値の転送の他のものに関して指定されるレジスタ識別子とは独立して指定可能であり、従って、この単一転送命令の使用に大幅な柔軟性を付与する。  (もっと読む)

(もっと読む)

1 - 20 / 32

[ Back to top ]