Fターム[5B033BF00]の内容

機械語命令の実行 (2,093) | マイクロコンピュータ (30)

Fターム[5B033BF00]の下位に属するFターム

チップ内レイアウト (1)

周辺装置インタフェース (7)

入出力端子 (3)

モード設定、切換 (11)

Fターム[5B033BF00]に分類される特許

1 - 8 / 8

縮小命令セット・コンピュータ・マイクロプロセッサーの構造

【課題】本発明は、改良された形態の、単純化された縮小命令セット・コンピューター(RISC)マイクロプロセッサーに関する。特に、スタック構造をとるマイクロプロセッサーに関する。

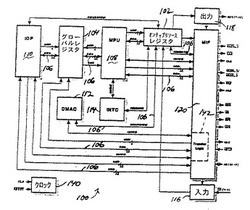

【解決手段】本発明のある態様では、マイクロプロセッサーシステムはマイクロプロセッシングユニットと入出力プロセッサー(IOP)とを含んでいる。大域メモリーユニットは中央処理装置及びIOPと連結されている。ある手段が、中央処理装置及びIOPの大域メモリーユニットへのアクセスを裁定する。ある形態では大域メモリーユニットは複数の大域レジスタを含んでいる。

(もっと読む)

プロセッサシステムおよび例外処理方法

【課題】エラー発生時の命令アドレス退避およびエラー処理終了後の実行命令復帰制御をおこなわないコプロセッサを付随するマイクロプロセッサを提供する。

【解決手段】プロセッサシステムにおいて、エラー検出部でエラーを検出した場合、エラー検出部120は割り込み制御部64にエラー信号を出力し、割り込み制御部64はエラーアドレスレジスタ61の値と制御信号をプログラムカウンタ制御部20に出力し、プログラムカウンタ21の値をエラーアドレスレジスタ61の値に書き換えることでエラー割り込みによる分岐処理を実現する。ここでエラーが検出されたときに、エラー発生時のプログラムカウンタ21の値を退避させる処理をおこなわず、特定の退避レジスタおよびエラー処理実行後にエラー発生時のアドレスに復帰する制御回路を設けない。

(もっと読む)

プロセッサおよびそれを用いたマイクロコンピュータシステム

【課題】汎用レジスタを用いないプロセッサを提供すること。

【解決手段】複数のCo−CPUが互いに接続され、複数のCo−CPUが別個の演算を並列に実行するプロセッサが提供される。複数のCo−CPUのそれぞれは、コマンドデコーダ22と、ALU21と、複数のセレクタ23〜36とを含む。コマンドデコーダ22は、コマンドコードをデコードする。セレクタ23〜28は、隣接する複数のCo−CPUからの出力およびMRAMからの出力を受け、少なくとも1つを選択的に出力する。ALU21は、セレクタ27および28からの出力に対してコマンドデコーダ22によるデコード結果に応じた演算を行なう。セレクタ31〜32は、ALU21による演算結果および隣接する複数のCo−CPUからの出力を受け、隣接する他の複数のCo−CPUに選択的に出力する。したがって、汎用レジスタを用いないプロセッサを提供することが可能になる。

(もっと読む)

CPU、集積回路装置、マイクロコンピュータ、電子機器、及びCPUの制御方法

【課題】リセット専用ロジックを持つことなしにリセット機能を実現できるCPUの提供。

【解決手段】本CPU10は、命令コード32を読み出してフェッチレジスタ30にフェッチするフェッチ回路20と、フェッチレジスタ30にフェッチされている命令コードを受け取り、デコードして実行する命令デコード実行回路40とを含み、フェッチレジスタ30は、リセット入力がリセット信号80に接続され、リセット時に所定のソフトウエア割り込み命令に初期化されるように構成され、命令デコード実行回路40は、所定のソフトウエア割り込み命令の命令コードをデコードして実行するソフトウエア割り込み処理部50を含む。

(もっと読む)

縮小命令セット・コンピュータ・マイクロプロセッサーの構造

【課題】本発明は、改良された形態の、単純化された縮小命令セット・コンピューター(RISC)マイクロプロセッサーに関する。特に、スタック構造をとるマイクロプロセッサーに関する。

【解決手段】本発明のある態様では、マイクロプロセッサーシステムはマイクロプロセッシングユニットと入出力プロセッサー(IOP)とを含んでいる。大域メモリーユニットは中央処理装置及びIOPと連結されている。ある手段が、中央処理装置及びIOPの大域メモリーユニットへのアクセスを裁定する。ある形態では大域メモリーユニットは複数の大域レジスタを含んでいる。

(もっと読む)

シグナルプロセッサ

【課題】それぞれのアプリケーション分野に最適に適合できるシグナルプロセッサを提供すること。

【解決手段】デコーダ(5)は、第1デコーダ部分(7)と、第2デコーダ部分(8)と、機能ユニット(9)と、マルチプレクサ(10)とを有し、

前記第1デコーダ部分(7)は固定配線されており、かつプログラム不能であり、論理演算を使用して、圧縮プログラムインストラクションをデコードし、

前記第2デコーダ部分(8)はプログラム可能であり、

前記機能ユニット(9)は、第1デコーダ部分(7)または第2デコーダ部分(8)のどちらがデコードを行なうかを決定し、

前記マルチプレクサ(10)は、第1デコーダ部分(7)または第2デコーダ部分(8)を選択的にシグナルプロセッサの出力端に、前記機能ユニット(9)によって発生されたビット信号のカテゴリーに応じて接続する。

(もっと読む)

アイドル要素予測回路およびアンチスラッシングロジック

制御ロジックはプログラム可能なプロセッサ中の特定の機能要素(例えば、除算器、または乗算器あるいはこれらに類似するもの)の使用を監視し、特定の機能要素が指定した期間の間使用されていないとき、ユニットの電源を切る。カウンタ(ローカルまたは中央)および時間しきい値は、設定期間が要素を使用することなく経過する時を決定する。制御ロジックはまた、機能ユニットがどのくらいの早さで再起動されるかを監視して電力制御がスラッシングを生じさせるかどうかを決定する。このようなスラッシングの決定の際にユニットがそのしきい期間を自動的に調整しスラッシングを最小化する。ロジックの例において非常に控えめであることをロジックが決定するとき、ロジックはしきい値を下げる。プログラマが電源切断ロジックを無効にして、ロジックを常に電源投入または常に電源切断のどちらかの状態にできるようにするために、モードビットが存在する。 (もっと読む)

予測的なプロセッサコンポーネントサスペンドのためのシステム及びその方法

命令サイクルが、キャッシュに記憶された命令から求められる(502)。ここで、命令サイクルは、キャッシュに常駐する、処理デバイスによって実行されると予測された命令シーケンスを表す。この命令サイクルの継続期間が見積もられ、命令サイクル中に使用されると予想されていない、処理デバイスの1つ又は2つ以上のコンポーネントを、その継続期間の一部又は全部の間サスペンドすることができる(506)。これらのコンポーネントは、たとえば、クロックゲーティングによるか、又は、1つ若しくは2つ以上の電源領域からコンポーネントを切り離すことにより、サスペンドすることができる(508)。  (もっと読む)

(もっと読む)

1 - 8 / 8

[ Back to top ]