Fターム[5B033DD03]の内容

Fターム[5B033DD03]に分類される特許

1 - 15 / 15

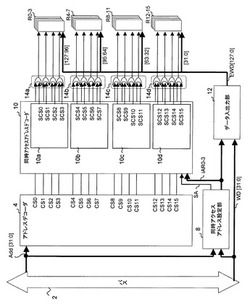

制御装置、及び制御方法

【課題】複数のレジスタへのアクセスを高速に行う。

【解決手段】制御装置は、複数のレジスタのアドレスをそれぞれ保持し、前記複数のレジスタのアドレスとは異なる第1のアドレスの指定に応答して前記複数のレジスタのアドレスを出力するアドレス設定部と、前記アドレス設定部から前記複数のレジスタのアドレスが入力され、当該複数のレジスタを選択する選択信号を同じタイミングで出力する第1のデコーダと、前記第1のアドレスに対する書込みデータを前記選択信号により選択される複数のレジスタに並行して書き込み、また、前記選択信号により選択される複数のレジスタから並行して読み出したデータを前記第1のアドレスからの読出しデータとして出力するデータ入出力部とを有する。複数のレジスタへ同時にアクセスでき、レジスタアクセスが高速化される。

(もっと読む)

ベクトル処理装置、システムおよびベクトル処理装置の動作方法

【課題】 ベクトル長が小さい場合にも、ベクトルレジスタファイルを効率よく使用し、ベクトル処理装置の性能を向上する。

【解決手段】 ベクトル処理装置は、ベクトルデータを各々格納する複数のデータレジスタが割り当てられるベクトルレジスタファイルと、ベクトルレジスタファイル内に割り当てられ、命令に含まれるオペランドにより指定可能な最大数のデータレジスタを各々有し、ベクトル長に応じてサイズが変化する複数のレジスタセットと、レジスタセットのうち、ベクトル演算に使用するベクトルデータを保持するレジスタセットである有効レジスタセットを示す情報が格納される制御レジスタと、ベクトル長に応じて変化する有効レジスタセットの開始位置を基準にしてオペランドにより指定されるデータレジスタを用いてベクトル演算を実行する実行部とを有している。

(もっと読む)

マイクロプロセッサ及びその制御方法

【課題】マイクロプロセッサの処理速度を向上させること。

【解決手段】マイクロプロセッサは、データを格納する第1のレジスタセットと、第1のレジスタセットから退避させたデータを格納するとともに、格納したデータを第1のレジスタセットに復帰させる第2のレジスタセットと、第1のレジスタセットから第2のレジスタセットにデータを退避させるとともに、第2のレジスタセットから前記第1のレジスタセットにデータを復帰させるレジスタI/Fと、スタックメモリに退避させるレジスタの情報を退避レジスタ情報として生成する退避レジスタ情報生成部と、第2のレジスタセットに格納されたデータ及び退避レジスタ情報をスタックメモリに退避させるとともに、退避レジスタ情報を読み出してスタックメモリに退避させたデータを第2のレジスタセットに復帰させるスタックI/Fと、を有する。

(もっと読む)

マイクロコンピュータ

【課題】汎用レジスタの使用効率を最適化することが可能なマイクロコンピュータを提供すること。

【解決手段】制御部13は、命令コードのデコード結果に応じて、命令の実行を制御する。GRAレジスタ32は、複数の汎用レジスタのそれぞれに対するアクセス属性を記憶する。モード記憶部31は、CPUの動作を制御するためのモードを記憶する。そして、レジスタアクセス許可判定回路33は、制御部13から汎用レジスタに対してアクセス要求がある場合に、GRAレジスタ32に記憶されるアクセス属性およびモード記憶部31に記憶されるモードに応じて、当該汎用レジスタに対するアクセスを許可するか否かを判定する。したがって、モードに対応して使用される汎用レジスタの本数を変更することができ、汎用レジスタの使用効率を最適化することが可能となる。

(もっと読む)

特殊機能を提供する高性能投機的実行プロセッサの構造及び方法

【課題】数多くの特殊なプロセッサ機能及び能力を提供するための構造及び方法を内含する、中央処理ユニット(CPU)といった高性能プロセッサを提供する。

【解決手段】これらの構造及び方法は、(1)精確な状態を維持しながらロード/ストア命令を含む長待ち時間命令を攻撃的にスケジュールし;(2)任意の命令境界において精確な状態を維持し回復し;(3)精確な状態を維持するべく命令状態をトラッキングし;(4)精確な状態を維持するべく命令をチェックポインティングし;(5)タイムアウトチェックポイントを新規作成し維持し使用し;(6)浮動小数点例外をトラッキングし;(7)リネーム可能なトラップスタックを新規作成し維持し使用し;(8)複数の同時未解決分岐評価のためのウォッチポイントを新規作成し維持し使用し;(9)精確な状態を維持するために命令状態をトラッキングし;(10)精確な状態を維持する一方でプロセッサのスループットを増大させる。

(もっと読む)

演算処理装置

【課題】レジスタウィンドウ方式のレジスタファイルを備え、ウィンドウ切り替え命令の後続命令のアウトオブオーダ実行が可能な演算処理装置の回路規模を削減し、その消費電力も低減する。

【解決手段】MRF10は、レジスタファイル、MRF_RA1及びMRF_RA2と5つの読み出しポートio0、io1、io2、l0、l1を備える。レジスタ制御部210によってMRF_RA1を制御し、それらの読み出しポートから、CWPレジスタ213の値(cwp)で指定されるレジスタウィンドウのインレジスタ/アウトレジスタ、ローカルレジスタのウィンドウを選択出力する。次に、レジスタ制御部210によってMRF_RA2を制御し、該選択出力されたウィンドウのデータと前記レジスタファイルから入力するグローバルレジスタのウィンドウのデータから、演算部30が必要とするレジスタのデータを選択し、該データを演算部30に出力する。

(もっと読む)

特殊機能を提供する高性能投機的実行プロセッサの構造及び方法

【課題】数多くの特殊なプロセッサ機能及び能力を提供するための構造及び方法を内含する、中央処理ユニット(CPU)といった高性能プロセッサを提供する。

【解決手段】これらの構造及び方法は、(1)精確な状態を維持しながらロード/ストア命令を含む長待ち時間命令を攻撃的にスケジュールし;(2)任意の命令境界において精確な状態を維持し回復し;(3)精確な状態を維持するべく命令状態をトラッキングし;(4)精確な状態を維持するべく命令をチェックポインティングし;(5)タイムアウトチェックポイントを新規作成し維持し使用し;(6)浮動小数点例外をトラッキングし;(7)リネーム可能なトラップスタックを新規作成し維持し使用し;(8)複数の同時未解決分岐評価のためのウォッチポイントを新規作成し維持し使用し;(9)精確な状態を維持するために命令状態をトラッキングし;(10)精確な状態を維持する一方でプロセッサのスループットを増大させる。

(もっと読む)

マップに基づくレジスタ・ファイルへの間接アクセスのためにレジスタ・マップをSIMD指向管理するための方法、システム、およびプログラム

【課題】プロセッサ内のマップに基づく間接レジスタ・ファイル・アクセスのために、レジスタ・マップを管理するための機構が提供される。

【解決手段】管理機構はマップ・セットを含むレジスタ・マッピングを含み、マップ・セットの各マップは複数のマップ・レジスタを有する。実レジスタ・セットには、マップ・セットのマップ・エントリを介してプロセッサによって間接的にアクセスされる。実レジスタ・セット内の実レジスタの数は、マップ・セット内のマップ・エントリの数より多く、マップ・セットのマップ・エントリは、任意の時点で実レジスタ・セットのサブセットのみを参照する。この機構は、単一の更新命令の実行に応答して、マップ・セットのうちの少なくとも1つのマップの複数のマップ・エントリを更新することにより、レジスタ・マッピングのマップ・セットの複数のエントリへの更新を管理するステップを含む。

(もっと読む)

マルチバンクレジスタを有するプロセッサおよびプロセッサの制御方法

【課題】命令長を長くせずに多くのレジスタを扱えて、パイプライン処理においてストールが発生しにくくすることを課題とする。

【解決手段】プロセッサ(100)が、命令デコーダと、演算器(12)と、外部メモリ(19)との間でデータ入出力を行なうメモリアクセス手段(13等)と、該演算器および該メモリアクセス手段からアクセス可能なレジスタをそれぞれ備えた複数のレジスタバンク(11)と、レジスタバンク指定命令に基づく該命令デコーダからのレジスタバンク指定制御信号により、該演算器が該レジスタバンクのいずれにアクセスするか、および、該メモリアクセス手段が該レジスタバンクのいずれにアクセスするかを制御するものであるバンクスイッチ手段とを備えている。またこのプロセッサ(100)を用いたマルチプロセッサシステムや、プロセッサ(100)の制御方法を提供する。

(もっと読む)

プロセッサおよび演算処理方法

【課題】 パイプライン処理を行うプロセッサにおいて、レジスタのゲート数を低減しつつ、複数のタスクあるいはスレッドを効率的に処理すること。

【解決手段】 パイプライン処理装置1は、レジスタファイルに代えて、メモリによって構成されたレジスタ用メモリ100を備えていると共に、PCを構成するレジスタに代えて、メモリによって構成されたプログラムカウンタ用メモリ30を備えている。したがって、これらをレジスタによって構成する場合に比べ、レジスタのゲート数が低減すると共に、コンテキストの入れ替えを行うことなく、アドレスの指定によってコンテキストスイッチを行うことができるため、複数のタスクあるいはスレッドを効率的に処理することが可能となる。

(もっと読む)

プロセッサ

【課題】 擬似並行的に複数のプログラムを効率的に実行可能なプロセッサを提供する。

【解決手段】 複数のレジスタ群と、複数のレジスタ群のうちいずれか1つを、プログラム実行の基礎とする実行対象レジスタ群として選択し、選択先を所定時間毎に切り替えるレジスタ切替部412と、切り替え毎に、実行対象レジスタ群にあるレジスタ値群によりプログラムを特定し、特定したプログラムを実行する処理実行部410と、プログラムの実行を中断する中断事由が発生していることを検出し、中断事由が解消したことを検出し、プログラムの実行をするハードウエアの消費電力を低減する処理制御部411とを備え、処理実行部410は、プログラムについての中断事由の発生が検出された場合、中断事由が解消するまでプログラムの実行のために割り当てられるべき実行期間を放棄し、処理制御部411が放棄している間、電力低減を実施するプロセッサ。

(もっと読む)

クラスタ化スーパスカラプロセッサ及びクラスタ化スーパスカラプロセッサにおけるクラスタ間の通信制御方法

【課題】クラスタ化スーパスカラプロセッサにおけるレジスタ・キャッシュのミス率を低下させることにより、ミス・ペナルティを被る確率が低下し、性能が向上するクラスタ化スーパスカラプロセッサ及びクラスタ化スーパスカラプロセッサにおけるクラスタ間の通信制御方法を提供する。

【解決手段】命令を命令ウィンドウに書き込む前に、該命令ウィンドウ中の先行命令に依存関係がないかをチェックし、依存関係がある場合には、その命令に対し、自身が割り当てられるクラスタにデータ通信するように要求を出す。要求された命令の実行結果は、命令の実行終了後に、指定されたクラスタのレジスタ・キャッシュに選択的に広域通信する。

(もっと読む)

マルチバンクレジスタを有するプロセッサおよびプロセッサの制御方法

命令長を長くせずに多くのレジスタを扱えて、パイプライン処理においてストールが発生しにくくすることを課題とする。プロセッサ(100)が、命令デコーダと、演算器(12)と、外部メモリ(19)との間でデータ入出力を行なうメモリアクセス手段(13等)と、該演算器および該メモリアクセス手段からアクセス可能なレジスタをそれぞれ備えた複数のレジスタバンク(11)と、レジスタバンク指定命令に基づく該命令デコーダからのレジスタバンク指定制御信号により、該演算器が該レジスタバンクのいずれにアクセスするか、および、該メモリアクセス手段が該レジスタバンクのいずれにアクセスするかを制御するものであるバンクスイッチ手段とを備えている。またこのプロセッサ(100)を用いたマルチプロセッサシステムや、プロセッサ(100)の制御方法を提供する。  (もっと読む)

(もっと読む)

仕切りのあるレジスタバンクのためのバンク付与

オペランドについての可能な候補レジスタバンクを特定することで、仕切られたレジスタバンク内の物理レジスタにオペランドを付与することができる。前記オペランドを候補レジスタバンクに割り当てる前に、候補レジスタバンク間に抵触がもしあれば、特定して解決する。 (もっと読む)

クロススレッドレジスタ共有化技術

マイクロプロセッサ内のレジスタリソース共有化技術。本発明の実施例は、大きなハードウェアオーバーヘッドを受けることなく、最適な個数の物理的レジスタが所望の個数の論理レジスタにマッピングされることを容易にする複数の命令スレッドに対するマイクロプロセッサ内のレジスタ共有化技術に関する。 (もっと読む)

1 - 15 / 15

[ Back to top ]