Fターム[5B042GA14]の内容

デバッグ、監視 (27,428) | 対象プログラム、装置 (3,643) | 対象システム、対象装置 (2,500) | パイプライン、命令プリフェッチ (30)

Fターム[5B042GA14]に分類される特許

1 - 20 / 30

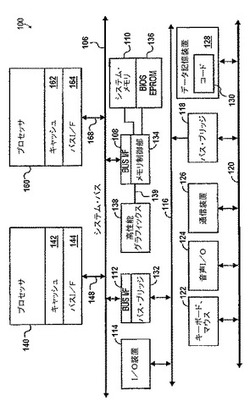

複数のデータ・エレメントの収集及び分散

【課題】複数のデータ・エレメントの収集及び分散におけるオーバーヘッドを低減するプロセッサを提供する。

【解決手段】効率的なデータ転送処理は、単一の命令が複数のデータ・エレメントに対する第1の記憶域と第2の記憶域との間の転送処理を指定し、プロセッサ装置140,160によりデコードする段階、前記プロセッサ内の演算実行部による実行のために単一の命令を発行する段階、単一の命令の実行中に例外の発生を検出する段階、及び該例外に応答して、該例外を分配する前に、未解決のトラップ又は割り込みを例外ハンドラに分配する段階、により達成されうる。

(もっと読む)

補正装置、補正方法、および補正プログラム

【課題】シミュレーションの精度の向上を図ること。

【解決手段】シミュレーション装置100は、先行するブロック102の末尾命令で指定される第1の資源群とブロック103の先頭命令で指定される第2の資源群とを検出し、第1および第2の資源群に共通して含まれる資源r1を特定する。次に、シミュレーション装置100は、ブロック103でr1を使用する時刻t+1と、先行するブロック102で資源の使用が終了し、後続のブロックで資源が使用可能となる時刻t+2とから求めた遅延時間1サイクルを算出する。続けて、シミュレーション装置100は、遅延時間を用いてADD命令の実行時刻を補正する。

(もっと読む)

プログラムデバッグ装置、方法、及びプログラム

【課題】プログラムの実行時間の測定中にブレークが発生した場合であっても、プログラムの実行時間を正確に測定できるようにする。

【解決手段】本発明に係るプログラムデバッグ装置1は、カウンタ2と、ブレークが発生する直前に実行された命令を特定する情報を保持するブレーク前情報保持部3と、ブレークの終了後に再実行される命令を特定する情報を保持する再実行開始情報保持部4と、通常時において直前に実行された命令と再実行される命令とが連続して実行される場合に要する実行時間を推定し、当該推定された実行時間に基づいて前記ブレークにより前記命令が無効にされたことに起因する誤差を補正するための補正値を生成する測定誤差演算部5とを有する。

(もっと読む)

クリティカルパスに基づく解析のための性能モニタリングアーキテクチャ強化

【課題】マイクロアーキテクチャの性能をモニタリングし、そのモニタリングされた性能に基づいてマイクロアーキテクチャをチューニングする方法及び装置を提供する。

【解決手段】シミュレーション、解析上の推論、リタイアメントプッシュアウト測定、全体実行時間、およびインスタンス当たりのイベントコストを決定する他の方法によって性能がモニタリングされる。インスタンス当たりのイベントコストに基づき、マイクロアーキテクチャおよび/または実行ソフトウェアは、性能を強化すべくチューニングされる。

(もっと読む)

非侵入型デジタル信号プロセッサデバッギング中における命令スタッフィング動作に関する方法及びシステム

【課題】マルチスレッド化デジタル信号プロセッサと関連してコアプロセスをデバッギングする。

【解決手段】スタッフ命令をデバッギングプロセスレジストリ内に書き込み、スタッフコマンドをデバッギングプロセスコマンドレジスタ内に書き込むことは、前記スタッフ命令を実行すべきマルチスレッド化デジタル信号プロセッサの予め決められたスレッドを識別する。命令スタッフィングプロセスは、前記予め決められたスレッド上における予め決められた実行ステージ中にデバッギングプロセス制御再開コマンドを発行し、前記デバッギングプロセス中に前記スタッフ命令を実行するようにコアプロセッサに指示する。これで、前記コアプロセッサは、前記スタッフィングされた命令を前記コアプロセッサプロセス及び前記デバッギングプロセスと関連して実行することができる。

(もっと読む)

処理装置

【課題】特殊信号が発生した際にプログラムカウンタ値を出力する処理装置を提供することを課題とする。

【解決手段】処理装置は、プログラムカウンタ値のアドレスの命令が命令メモリ(311)から読み出されると、読み出された命令に対応するプログラムカウンタ値を上位ビット部(331)及び下位ビット部(332)に分割し、上位ビット部をレジスタ部(500)に書き込み、読み出された命令とそれに対応する下位ビット部との組みを後段に伝播させる制御部(501)と、読み出された命令に対して複数ステージのパイプライン処理を行い、読み出された命令の情報とその命令に対応する下位ビット部との組みを各ステージに伝播させる演算パイプライン(301〜306)とを有し、制御部は、演算パイプラインで読み出された命令の処理による特殊信号が発生すると、その命令に対応する下位ビット部とレジスタ部内の上位ビット部とを結合させて出力する。

(もっと読む)

データ処理装置、トレースユニット、および診断装置

【課題】トレースデータストリーム内のアドレスのより大きな圧縮を提供する。

【解決手段】トレース回路8は、対応する参照アドレスを格納する複数の参照アドレスレジスタ30−1を有する。処理回路4が、関連付けられたメモリアドレスに関連付けられた処理動作を実行すると、トレース回路8は、選択された参照アドレスレジスタとして参照アドレスレジスタ30−1のうちの1つを選択し、(i)参照アドレスレジスタ30−1のうちのどれが選択された参照アドレスレジスタであるか、および、(ii)存在する場合、関連付けられたメモリアドレスと選択された参照アドレスレジスタの参照アドレスとの差を示すトレースデータ要素を生成する。トレースストリームを分析するための診断装置20は、参照アドレスレジスタ30−2を使用して、トレースデータ要素から関連付けられたメモリアドレスを再構成する。

(もっと読む)

推測的に実行される命令のトレーシング

【課題】推測的命令を実行するデータ処理装置のトレースにおいて、推測的に実行された命令が後ほどキャンセルされた場合のトレースデータ出力の理解の困難を解消する。

【解決手段】トレースユニットは、プロセッサの挙動を監視するトレース回路50と、トレース回路を制御するため現在のトレース制御データを蓄積する蓄積回路60と、トレース制御データの少なくとも一部を蓄積するデータストア65と、を備え、トレース回路は、命令グループの実行の検出に応じてトレース制御データをデータストアに蓄積するよう構成され、トレース回路は、推測的に実行された少なくとも1つの命令グループをキャンセルする少なくとも1つのプロセッサを検出することに反応し、キャンセルされる推測実行命令の前に実行された命令グループのデータストアに蓄積されたトレース制御データの少なくとも一部を取り出し、且つ取り出されたトレース制御データを蓄積回路に蓄積する。

(もっと読む)

情報処理装置

【課題】CPUの命令実行解析情報とメモリアクセスの情報を的確に取得する。

【解決手段】オペランドバス(105,205)に結合された実行部(103,203)と、制御部(101,201)とを含む中央処理装置(CPU#0,#1)と、デバッグ回路(35)とを設ける。上記制御部は、上記中央処理装置での命令実行解析情報を収集するデバッグ機能部を含む。上記デバッグ回路は、上記命令実行解析情報と上記オペランドバスから得られる情報とをそれぞれ専用の論理回路(112,114,212,214)を介して取り込むトレース取得回路(110,210)と、トレース出力回路(111,211)とを含む。上記トレース取得回路には、上記命令実行解析情報と上記オペランドバスから得られる情報とを並べ替える並べ替え論理部(115,215)を設け、的確なトレースを可能にする。

(もっと読む)

プロセッサ、及び並列命令実行対応デバッグ装置

【課題】VLIWアーキテクチャを採用したプロセッサでは、並列に実行するように変換されたプログラムの命令列の任意の命令だけをデバッグのためのデバッグ命令に置き換え、1命令だけをステップ実行することはできない課題があった。

【解決手段】VLIWアーキテクチャを採用したプロセッサに、並列実行が可能な命令数と同じ数のデバッグ命令検出手段を備える命令解析手段と、デバッグ命令が検出された際に、デバッグ命令と同一の実行単位に含まれ且つ前記デバッグ命令より高位のアドレスに配置されている命令の実行を取り消す命令取消手段を備えたことを特徴とする。

(もっと読む)

CPUでの命令実行と非同期的に発生するメモリアクセスエラーの原因究明のための情報処理装置、異常分析方法、および異常分析プログラム

【課題】エラー発生時のCPUレジスタ値を見ても、当該メモリアクセス命令を発行したプログラム(OS)位置が一意に特定できず、異常分析が困難なことがある。このような、CPUでの命令実行と非同期的に発生するメモリアクセスエラーに対して、異常分析を容易に行なう方法が提供されていない。

【解決手段】メモリアクセス命令に指定されるメモリのアドレスに、当該命令実行時のレジスタ値を付加してアドレスを拡張(拡張アドレス)し、この拡張アドレスを用いてメモリアクセスを実施する。メモリアクセスエラー発生時には、この拡張アドレスをユーザに提示する。この方法により、エラー発生時にCPUが別の命令を実行していたとしても、エラー発生の原因となった命令を実行した際のレジスタ値をユーザは取得することができるため、当該命令を発行したプログラム(OS)位置が一意に特定可能となる。

(もっと読む)

デバッグ方法、プログラム、及びシステム

【課題】パイプライン処理を命令実行構造として採用したプロセッサにて実行されるプログラムのデバッグをより的確に実行すること。

【解決手段】複数の命令を並列処理すると共に、少なくとも分岐命令、及び当該分岐命令に対して後続する命令をこの順に実行した後、分岐命令により指定される命令を実行するパイプライン処理型プロセッサによって処理されるプログラムのデバッグ方法であって、プログラムを構成する命令群に含まれ、かつ所望の停止位置にある命令を、自身の位置を分岐先として指定する分岐命令、及び当該分岐命令に続いて実行される停止命令に書き換え、当該書き換え後のプログラムを実行する。所望の停止位置にある命令を、遅延分岐命令及び停止命令に書き換えることによって、停止時にパイプライン上に残存する命令の影響を排除することができる。

(もっと読む)

情報処理システム及びその評価方法

【課題】モードを変更してもシステムを停止する必要がなく、システムの評価を効率的に行うことが可能な情報処理システムを提供する。

【解決手段】命令バッファ3のリタイヤカウンタ10を監視し、リタイヤカウンタ10が所定のしきい値11を超えたことを検知する手段、リタイヤカウンタ10が所定のしきい値11を超えた時には動作モードを通常モードから安定モードに変更する手段、安定モードに変更後に新規にコンテキストスイッチ7が発生した時に動作モードを通常モードに戻す手段を具備する。また、リタイヤカウンタ10が所定のしきい値11を超えた時にフェッチICをリタイヤIC15に更新してプログラムをリタイヤICから再開させる。

(もっと読む)

マイクロプロセッサ及びマイクロプロセッサのデバッグ方法

【課題】マイクロプロセッサの内部の論理不正動作の調査を容易化できるようにする。

【解決手段】論理動作不正が発生する命令列を、比較命令格納バッファ40に記憶し、プログラムを動作させ、命令比較部41で、実際に実行している命令と比較命令格納バッファ40に記憶されている命令とを比較し、コピー指示のある命令を検出すると、偶数個のコピー命令を生成する。後続のコピーされた偶数個の命令は、前方に存在する命令が完了するまで実行しない命令間隔に設定しており、タイミングや競合による論理動作不正を発生しない。命令列中の最後の命令から1命令ずつコピー指示を前の命令に移動させながらプログラムを実行し、多数決処理チェックの結果を確認することで、論理動作不正の発生する命令を特定する。

(もっと読む)

半導体装置及びソフトウェア開発支援装置

【課題】ユーザプログラムを実行しながら、CPU内部のレジスタ情報、特にステータスレジスタ値やプログラムカウンタ値を観測する。

【解決手段】半導体装置は、プログラムを実行可能なCPU(31)と、上記プログラムのデバッグを支援するためのデバッグ回路(33)とを備える。上記CPUは、ステータスレジスタと、プログラムカウンタとを含む。上記半導体装置は、ユーザプログラムの実行を停止させないで上記CPU内のレジスタ情報を取得するための専用パス(35)を含む。この専用パスは、上記ステータスレジスタが更新された場合の当該更新に対応する上記プログラムカウンタの値を、上記ステータスレジスタが次に更新される前に取得し、取得されたプログラムカウンタ値と、それに対応するステータスレジスタ値とをセットにして上記デバッグ回路に伝達するための論理回路(32)を含む。

(もっと読む)

シンボリックデバッガ、方法およびプログラム

【課題】パイプライン処理をユーザが直感的かつ容易にデバッグすることが可能なシンボリックデバッガを提供する。

【解決手段】シンボリックデバッガは、表示手段と、ハードウェア動作モデルを実行するモデル実行手段と、その実行状態に応じて表示手段によるソースプログラムの実行状態の表示を管理する対応関係管理手段と、を有する。対応関係管理手段は、現在実行中の基本ブロックに記述されたステージに対応するソースプログラム中の命令文の行を特定し、該特定した命令文に用いられた変数の値をモデル実行手段から取得する。表示手段は、特定された命令文の行、変数、該変数の値を関連付けて同一の強調表示形態により表示する。対応関係管理手段は、処理の流れを判別可能な複数の異なる強調表示のパターンに基づき、パイプライン動作の進行状況に応じて強調表示形態をステージ別に変化させる。

(もっと読む)

パイプライン型アーキテクチャを有するデータプロセッサ内のトレースデータを与えるシステム

本発明は、パイプライン型データプロセッサにおけるトレースデータを与える方法及びシステムである。本発明の態様は、実行パイプラインと並列のトレースパイプラインを設け、条件付き命令が完了したかどうかについてのトレース情報を与え、プロセッサの割り込みステータスについてのトレース情報を与え、プロセッサ内の命令を、やはりトレース情報を生成する機能的に等価な命令と置き換え、トレース出力バッファの占有率に基づいて、プロセッサ内の命令のスケジューリングを修正することを含む。 (もっと読む)

デバッグイベントを監視するためのシステム及び方法

複数の命令について、フェッチ、デコード、および実行と、各命令の実行に関連した結果の書込とを連続的に行うことによって、複数の命令を実行するためのパイプライン・プロセッサ(12)を有するシステム。デバッグ回路(40)は、パイプライン・プロセッサに結合されており、命令の実行を監視してデバッグイベントが発生する時を判定する。デバッグ回路は、デバッグ例外を発生させて命令処理フローを中断する。デバッグ回路は、デバッグイベントを引き起こした命令と命令実行において例外が発生するポイントとの間で命令実行を完了させる命令(存在する場合)の数を表す値を示すための制御回路(44)を有する。  (もっと読む)

(もっと読む)

半導体装置、及び半導体装置のデバッグ方法

【課題】プロセッサが実行していた異常終了直前の命令データを特定することができる。

【解決手段】LSI10は、バス13を介してプロセッサ12に入力された命令データを処理するパイプライン15、及びパイプラインに15よって処理された命令データが入力され、命令データに従って演算処理を行う演算実行回路16を有するプロセッサ12と、パイプライン15から演算実行回路16に入力される命令データを格納する記憶回路14と、を有するものである。

(もっと読む)

プロセッサ

【課題】プログラムの実行を停止する際の遷移期間においてデバッグ動作が実行されることにより生じるパイプライン・ハザードを解消できるプロセッサを提供する。

【解決手段】パイプライン方式にて命令を処理する命令処理部10において当該処理が停止される場合、新たな命令の処理が停止されるとともに、既に開始された処理が完了したか否かを示す状態信号S1が出力される。この状態信号S1が命令処理部10における処理の未完了状態を示す場合、デバッグ部20によるデバッグ動作の実行がデバッグ制限部30により制限される。すなわち、命令処理部10への命令の入力を停止してからその停止前に既に開始された処理が完了するまでの間、命令処理部10の動作の制御やその動作状態の記録などに関連するデバッグ動作が制限される。

(もっと読む)

1 - 20 / 30

[ Back to top ]