Fターム[5B048EE03]の内容

デジタル計算機の試験診断 (4,118) | 試験項目 (236) | 波形 (9)

Fターム[5B048EE03]に分類される特許

1 - 9 / 9

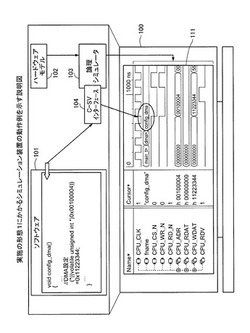

シミュレーション装置、シミュレーション方法、およびシミュレーションプログラム

【課題】ハードウェアとソフトウェアの協調動作のデバッグを効率的に行うこと。

【解決手段】シミュレーション装置100は、ソフトウェア101の実行中に、ハードウェアモデル102にアクセスする特定の関数が実行される場合、論理シミュレータ103側となるC−SVインターフェース104にて特定の関数の関数名を取得する。次に、C−SVインターフェース104は、関数名を記憶領域に格納する。また、論理シミュレータ103も、ハードウェアモデル102のシミュレーションの結果を記憶領域に格納する。波形ビューワ111は、記憶領域に格納されたシミュレーションの結果と関数名とを、時系列で対応付けて表示する。

(もっと読む)

信号処理ユニット及びこれを備える統合管理システム

【課題】コンフィギュレーションデータの更新情報を極めて簡素な信号で表現させ得る信号処理ユニットを提供する。

【解決手段】信号処理ユニット100は、コンフィギュレーションデータの更新情報が周波数信号によって表現され、当該周波数信号がFPGAから出力される。また、CPUでは、入力された周波数信号の周波数fに基づいて、コンフィギュレーションデータの更新情報を認識する処理を行うこととされる。このため、FPGAでは、一つのデータpinから更新情報に係る信号を出力させることが可能となり、当該FPGAに配備される他のデータpinを有効に利用できる。また、CPUでは、周波数信号の周波数fに基づいて更新情報を特定できるので、パルスエッジ等の間隔を検出することで直ちに更新情報を認識することが可能となる。

(もっと読む)

エミュレーション観測信号送信システム、エミュレーション観測信号送信方法、エミュレーション装置及びプログラム

【課題】エミュレーション装置11とホストコンピュータ12との通信回数を抑制することができるエミュレーション観測信号送信システムを提供する。

【解決手段】本発明のエミュレーション観測信号送信システムは、半導体集積回路の動作検証を行うエミュレーション装置と、ホストコンピュータとを備え、前記エミュレーション装置は、被検証回路の動作検証を行うFPGAと、少なくとも1つの観測用レジスタと、前記FPGAから前記観測信号を引き出し、前記観測用レジスタに記憶する記憶位置を決定するエミュレーション制御部と、前記エミュレーション制御部が決定した前記記憶位置に、前記観測信号の信号線を接続する観測信号送信回路を作成する観測用レジスタ記憶位置接続部とを備える。

(もっと読む)

集積回路、システム検証方法、及び携帯端末装置

【課題】 JTAG−ICEやロジックアナライザ等の測定器を用いることなく、ソフトウェアプログラムの介在を極力排除し、LSI内部のモードを極力変化させることなく、ソフトウェアプログラム及びハードウェアにおける問題発生条件の特定、及び問題解析を可能とする。

【解決手段】 バスコントローラから供給される各イニシエータとの間で送受信されたデータ、及び当該データに対応する上記イニシエータ識別番号を、バスイニシエータモニタの内蔵メモリに記憶する。そして、所定のアボート、或いはシステムリセットが発生した際に、上記内蔵メモリをライトプロテクト状態とし、このライトプロテクト状態とされた内蔵メモリに記憶されている上記データ及び上記イニシエータ識別番号を、シリアルデータラインを介して外部に出力して問題発生条件の特定及び問題解析を行う。

(もっと読む)

半導体試験システム

【課題】半導体デバイスの入出力波形やフェイル情報の収集に要する手間を低減することができる半導体試験システムを提供すること。

【解決手段】半導体試験システムは、半導体デバイス11aに対して所定の試験を行う半導体試験装置1と、試験条件を設定するとともにこの試験の実行を半導体試験装置1に対して指示する制御装置2とを有する。制御装置2は、試験条件を設定する試験条件設定手段と試験の実行指示を行う実行指示手段と試験によって得られた第1のデータを収集する試験データ収集手段としてのキャプチャ部20とを備える。キャプチャ部20は、第1のデータを収集する半導体デバイス11aのサイクル位置を可変に設定するとともに、サイクル位置の設定が異なるように設定された複数の試験条件のそれぞれに対応して実行指示を行う。

(もっと読む)

検証支援装置、検証支援方法、及びプログラム

【課題】検証対象マイコンの基準クロックの停止を識別でき、かつその基準クロックの停止期間を測定できるようにする。

【解決手段】検証対象のマイコン20から出力される出力データを取得し、出力データとともにマイコン20から出力される基準クロックを用いて、取得した出力データをデータバンク部12に保存するとともに、クロック動作判別部15が出力データのサンプリング間隔で基準クロックの停止を判別し、その判別結果をレジスタ制御部16によりクロック情報レジスタ部17に書き込み保存するようにして、クロック情報レジスタ部17に書き込まれた情報に基づいて、基準クロックの停止位置及び停止期間を測定できるようにする。

(もっと読む)

バストレース方式

【課題】制御LSIから高速メモリへのアクセスを外部で容易にモニターすることを可能にする手段を提供する。

【解決手段】高速メモリ(020)の特定のアドレスに対するアクセス波形を制御LSI(010)の外部で観測する場合は、波形観測対象のアドレスをアドレス比較部(014)で判断し、高速メモリ(020)のアドレスへのアクセスとして波形観測対象のアドレスが発生した場合、アドレス比較部(014)とANDゲート(019)によりバストレース信号切替部(015)を制御して、高速メモリバス(017)と低速メモリバス(018)を接続する。これによりCPU(011)から高速メモリ(020)へのアクセス信号が、高速メモリバス(017)→バストレース信号切替部(015)→低速メモリバス(018)経由で制御LSI(010)の外部へ出力され、高速メモリ(020)へのアクセス状態を低速メモリ側で観測することが可能となる。

(もっと読む)

システム状態判断装置および方法

【課題】 システムにおけるノイズによる多様な異常状態を発生させ、異常状態から正常状態に復帰したか否かを判断する装置および方法を提供する。

【解決手段】 システムの初期状態の出力電圧波形が検知され(S10)、記憶される(S12)。ノイズ周波数のパラメータ初期値として1GHzと設定されると(S14にてYES)、周波数が1GHzのノイズがノイズ発生部16から発生される(S16)。一定時間が経過すると(S18にてYES)、ノイズ発生後の出力信号の電圧波形が検知され(S20)、記憶される(S22)。初期状態の出力電圧波形と、ノイズ発生後の出力電圧波形とが一致しない場合(S24にてYES)には、ノイズの発生が停止され(S28)、一定時間の経過後(S30にてYES)、再び出力信号の電圧波形が検知され(S32)、記憶される(S34)。このとき記憶された電圧波形が、初期状態の出力電圧波形と一致しない場合(S36にてNO)、不合格と判定される(S42)。

(もっと読む)

システムLSIデバッグ方法およびデバッグ装置

【課題】 システムLSIを用いて製品開発を行う際のデバッグ方法およびデバッグ装置に関し、異常発生個所を時間軸で視覚的に特定することができる。

【解決手段】 発行された複数の制御コマンドを順次実行し、複数の制御コマンドがそれぞれもつIDを取得し、複数の制御コマンドのうちいずれかを実行している状態にあることを示すコマンド実行ステータスを取得し、制御コマンドの実行状態をコマンド実行パルスとして生成し、取得されたIDをパルスとして生成し、コマンド実行ステータスをパルスとして生成する。さらに、コマンド実行パルスと、IDパルスと、ステータスパルスとを、外部の信号測定部へ出力して表示する。

(もっと読む)

1 - 9 / 9

[ Back to top ]