Fターム[5B056FF00]の内容

複合演算 (1,407) | 構成回路 (181)

Fターム[5B056FF00]の下位に属するFターム

乗算器 (22)

加算器 (20)

ALU (3)

バタフライ演算回路 (21)

メモリ (28)

バッファ (13)

シフトレジスタ、バレルシフタ (5)

カウンタ (1)

ベクトルレジスタ (31)

マスクレジスタ (8)

ベクトル長レジスタ (3)

アライン回路 (5)

バス

パイプライン (15)

マイクロプログラム

入出力装置

Fターム[5B056FF00]に分類される特許

1 - 6 / 6

制御装置、制御プログラムおよび記録媒体

【課題】LUT30の参照値の数を減らした場合でも出力値の精度を劣化させず且つ計算コストを増加させない制御装置1等を提供する。

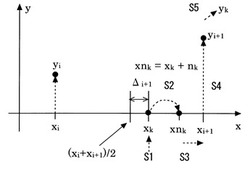

【解決手段】時刻kで入力された引数xk(参照値xiとxi+1との間に存在)に対して平均を0とする所定の確率分布に従うノイズnkを付加し新たな引数xnkとする。引数xnkに最も近い参照値(例えばxi+1)をLUT30から検索する。参照値xi+1に対応する出力値yi+1を引数xkに対応する出力値ykとして制御対象40側へ出力する。多次元LUTを用いた場合についても同様である。引数xkが(xi+xi+1)/2より参照値xi+1側へΔi+1だけ離れている場合、出力値ykがyi+1となる確率Pr(yk=yi+1)=Pr(nk<Δi+1)となる。ノイズnkが平均を0とする正規分布又は一様分布等の場合、出力値ykの平均E{yk}はガウス補間又は線形補間を行った場合と同様になる。

(もっと読む)

アレイプロセッサ

【課題】データ同士の入替作業用の専用回路の設置などを行うことなく、三次元離散直交変換および三次元逆離散直交変換を迅速に実行すること。

【解決手段】アレイプロセッサ1は、プロセッシングエレメントPEによる概念的な三次元配置状態により形成され、各プロセッシングエレメントPEの入力端子と出力端子とはそれぞれトーラス状に接続されている。各プロセッシングエレメントPEは、積和演算の演算結果を一の軸方向のプロセッシングエレメントPEに出力し、また、積和演算の演算データを他の軸方向のプロセッシングエレメントPEに出力する。演算結果等を取得したプロセッシングエレメントPEは積和演算を行い、演算結果と前記演算データとをそれぞれ隣接する他のプロセッシングエレメントPEに出力する。この処理をトーラス状に接続した全てのプロセッシングエレメントPEで行い、軸方向を変えて3回実行する。

(もっと読む)

ドット積演算を行うための命令および論理

【課題】ドット積演算に必要な命令数の大幅な削減を行う方法、装置、およびプログラム手段を提供する。

【解決手段】一実施形態では、装置は、1つのマイクロオペレーションに復号化された第1の命令を実行する実行リソースを含む。第1の命令に応答して、実行リソースは、少なくとも2つのソースオペランドのドット積を整数および浮動小数点を含む特定のデータタイプに対して演算し、結果値を前記ソースオペランドのうちの1つと同じレジスタまたはメモリロケーションに格納する。

(もっと読む)

シストリックアレイ

【課題】演算する行列サイズが可変とし負荷を均一化し、入出力データを蓄積するメモリを減らすMFA1次元シストリックアレイの提供。

【解決手段】MFA(修正Faddeevaアルゴリズム)を利用した行列演算用シストリックアレイであって、下方向正方MFAアレイ処理と、上方向正方MFAアレイ処理を1次元アレイに水平方向にマッピングし、1次元アレイの各PEでは、下方向と上方向の二つのスレッドのMFA行列演算が行われ、入出力を一次元アレイ両端のPEに対して備えている。

(もっと読む)

量子演算装置及び量子回路を用いた量子演算方法

【課題】 線形サイズ・線形深さで補助ビットを用いずに量子計算を行う。

【解決手段】

Q2n+1,Qk+2(k=1,…,2n-2)に対するCNOT演算操作を行い、Q1,Q2,Q2n+1に対するトフォリ演算操作を行い、その操作の後、Q2p+1,Q2p+2,Q2n+1に対するMAJ演算操作とQ2p+1,Q2p+2,Q1に対するトフォリ演算操作とをp=1からp=n-2までpを1ずつ増加させる順序で繰り返し、その繰り返しの後、Q2n-1,Q2n,Q2n+1に対するMAJ演算操作を行う。また、Q1,Q2q+4に対するCNOT演算操作とQ2q+1,Q2q+2,Q1に対するトフォリ演算操作とをq=n-2からq=1までqを1ずつ減少させる順序で繰り返す。そして、Q2に対するNOT演算操作を行い、Q1,Q2,Q2r+4(r=1,…,n-2)に対するトフォリ演算操作を行い、その操作の後、キュービットQ2に対するNOT演算操作を行い、さらにQ1,Q2,Q4に対するトフォリ演算操作を行い、その操作の後、Q2t,Q2t-1(t=1,…,n)に対するCNOT演算操作を行う。

(もっと読む)

FFT演算装置及びFFT演算方法

【課題】キャッシュメモリを用いて極めて多数のデータについてリアルタイムで実数FFT演算を行うFFT演算装置を提供する。

【解決手段】キャッシュメモリ13は、実数FFT演算の対象となるデータの一部を格納する。FFT演算部10は、キャッシュメモリ13の格納するデータについて、実数FFT演算を行う。FFT演算部10が、複数ステージのバタフライ演算のいずれかのステージの後に前記データ転送を少なくとも1回行うことにより、複数ステージのバタフライ演算におけるその後のバタフライ演算と変換結果を得るためのバタフライ演算とにおいて必要なデータをキャッシュメモリ13上に読み込み、その後のバタフライ演算を読み込まれたデータを用いて行い、その後にキャッシュメモリ13の格納するデータをそのまま使用して変換結果を得るためのバタフライ演算を行う。

(もっと読む)

1 - 6 / 6

[ Back to top ]