Fターム[5B060AA08]の内容

メモリシステム (7,345) | アロケーション、リロケーション (1,705) | 空間、領域管理手段 (388) | アドレス変換 (173)

Fターム[5B060AA08]に分類される特許

1 - 20 / 173

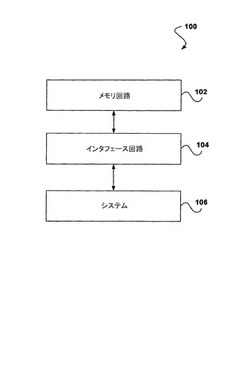

メモリ回路システム及び方法

【課題】メモリ回路システムを提供する。

【解決手段】インタフェース回路104が複数のメモリ回路102及びシステム106と通信できる。使用時、インタフェース回路は、メモリ回路の命令スケジューリングにおける制約を減少させるため、メモリ回路及びシステムをインターフェースするように動作する。別の実施形態では、インタフェース回路が、複数のメモリ回路、及びシステムと通信することができる。使用時、インタフェース回路は、システムとメモリ回路との間で伝達される命令に関連付けられているアドレスを変換するように動作する。更に別の実施形態では、少なくとも1つのメモリ積層体が、複数のDRAM集積回路を備えている。DRAM集積回路とホストシステムの間で1つ以上の物理パラメータを変換する目的で、ホストシステムに結合されたバッファ回路を使用して、ホストシステムにメモリ積層体をインターフェースする。

(もっと読む)

情報処理装置、送受信バッファ管理方法および送受信バッファ管理プログラム

【課題】ユーザ・カーネル間共有メモリを送受信バッファとして利用して通信する場合におけるページフォルトの発生を抑制する情報処理装置を提供する。

【解決手段】共有メモリ上の送受信バッファを利用して通信処理を行う情報処理装置であって、送受信バッファの位置する仮想ページから物理ページへのマッピングがページテーブルに存在する確度を示す確度指標を保持する確度指標保持手段1と、確度指標保持手段1が保持する確度指標に基づいて、確度が大きい送受信バッファから割当を行うバッファ管理手段2とを備えている。

(もっと読む)

メモリシステム

【課題】書き換え回数制限下での実効的な書き換え容量を増大したメモリシステムを提供する。

【解決手段】実施形態のメモリシステム1は、2ビット以上の所定ビット数の記憶容量のメモリセルを複数個有する不揮発性メモリ2と、前記メモリセルの書き換え回数を管理する書き換え回数管理テーブル40を備える。実施形態のメモリシステムは、ホスト7からの書き込み要求に応じたビット数で前記メモリセルに書き込みを行い、前記書き換え回数管理テーブル40が管理する前記メモリセルの書き換え回数が所定の回数を超えた後は、前記メモリセルを前記記憶容量に依存したグループに分割し、ホストからの書き込み要求に応じたビット数の前記記憶容量に対応する前記グループの前記メモリセルに書き込みを行うコントローラ3を備える。

(もっと読む)

メモリシステム、不揮発性記憶装置及びその制御方法

【課題】読み出し動作を高速化し、かつ書き込みに利用可能なフリーブロックを増加させる。

【解決手段】メモリシステム1は、不揮発性記憶装置3と情報処理装置2とを有する。情報処理装置2は、不揮発性記憶装置3の第1の論理アドレス領域からデータを読み出し、第1の論理アドレス領域に対応する読み出しデータが関数で表されるデータと同じである場合に、不揮発性記憶装置3に、第1の論理アドレス領域のデータを無効にするための削除通知を行う第1の制御回路を含む。不揮発性記憶装置3は、有効なデータに対応する論理アドレスと物理アドレスとを関連付ける管理テーブルと、削除通知により指定された論理アドレスを無効にするように管理テーブルを書き換え、情報処理装置2から受信した読み出し命令に含まれる論理アドレスが無効である場合に、関数で表されるデータを情報処理装置2に送信する第2の制御回路とを含む。

(もっと読む)

管理装置、および管理方法

【課題】不揮発性メモリの長寿命化を図りつつ不揮発性メモリを管理することが可能な管理装置、および管理方法を提供する。

【解決手段】電気的にデータの書き込み、読み出し、消去が可能であり、書き込みおよび読み出しはページ単位で行われ、消去は複数のページを含むブロック単位で行われる不揮発性メモリを管理する管理部を備え、管理部は、不揮発性メモリを構成する複数の物理ブロックを、仮想ブロックを有する仮想領域と、仮想領域の不良が発生している物理ブロックを代替する代替ブロックを有する代替領域とに分け、物理ブロックの管理、仮想ブロックの管理、およびユーザデータを一時的に保持する拡張ブロックの管理の3段階の管理単位で不揮発性メモリを管理し、物理ブロックの管理に用いる第1管理情報と、仮想ブロックの管理に用いる第2管理情報と、拡張ブロックの管理に用いる第3管理情報とを、不揮発性メモリに書き込む、管理装置が提供される。

(もっと読む)

トランザクションメモリ

【課題】トランザクション処理におけるソフトウェアオーバヘッド及び複雑さを低減する。

【解決手段】トランザクションリクエスト又は複数のトランザクション演算子を含むトランザクションコマンドを受信することに応答して、メモリアレイのオリジナルコンテンツを他の部分にコピーすることと、トランザクション演算子を受信することに応答して、コピーしたオリジナルコンテンツを修正する。トランザクションコミットを受信することに応答して、トランザクションが成功した場合のみ、オリジナルコンテンツを修正したコンテンツで置換する。

(もっと読む)

メモリコントローラ、及びデータ記録装置

【課題】管理テーブルを不揮発性メモリに保存する時の応答遅延時間を縮減し、データ記録装置の電源遮断後に、不揮発性メモリに保存した情報から管理テーブルを復元する機能を備えるメモリコントローラを提供する。

【解決手段】不揮発性メモリ1011は、管理テーブル格納ブロックと、データ書き込みのために割り当てたスクラッチブロックと、データを保持するデータブロックと、データを消去した消去済みブロックを持つ。メモリ1012は、データの格納場所を管理する論理・物理アドレス変換テーブル10120と、ブロック履歴管理テーブル10125を持つ。管理テーブル格納ブロックは、論理・物理アドレス変換テーブル10120とブロック履歴管理テーブル10125を保存する管理テーブルページを持つ。メモリコントローラ1010は、論理・物理アドレス変換テーブル10120の一部を不揮発性メモリ1011の管理テーブル格納ブロックに保存する。

(もっと読む)

データ格納装置、使用者装置及びそれの住所マッピング方法

【課題】マージ動作の効率を高くして高速のデータ書込み動作を可能とし、長い寿命を有するデータ格納装置、使用者装置及びその住所マッピング方法が提供される。

【解決手段】本発明による混合マッピング方式を使用する格納装置の住所マッピング方法は、バッファーメモリーに格納された書込みデータが少なくとも1つのスーパー連続ブロックを構成するか否かを判断する段階、及び前記判断結果にしたがって前記書込みデータに対する住所マッピングモードを決定する段階を含み、前記書込みデータの中で前記スーパー連続ブロックを構成する部分はブロックマッピングモードにしたがって論理住所を物理住所にマッピングする。

(もっと読む)

電力制御方法、計算機システム、及びプログラム

【課題】サーバに搭載されているメモリの消費電力を制御し、消費電力を削減する。

【解決手段】一つ以上の業務サーバ、業務サーバを管理する管理サーバ、及び、業務サーバと管理サーバとを接続するネットワーク、を備える計算機システムで実行されるメモリの消費電力を制御する方法であって、業務サーバは、メモリの消費電力を制御できる単位である一つ以上のメモリチップと、メモリチップの消費電力を省電力状態と通常状態とに切り替える制御を実施する電力制御機構と、一つ以上の仮想サーバを稼動させる仮想化機構と、を備え、管理サーバが、メモリチップのうち通常状態のメモリチップを特定し、管理サーバが、特定された通常状態のメモリチップのうち、仮想サーバに対して未割り当てのメモリチップを特定し、管理サーバが、特定された未割り当てのメモリチップの消費電力を省電力状態に変更するように業務サーバに指示する。

(もっと読む)

メモリコントローラ及びメモリコントローラを備える不揮発性メモリシステム、並びに不揮発性メモリの制御方法

【課題】ホストシステムから与えられるデータを格納するための領域を減少させることなく、論理ページと物理ページの対応関係を効率良く管理する。

【解決手段】それぞれの物理ブロックにおいて、物理ブロック内の物理ページをn個(nは2以上の整数)のグループに分割し、物理ブロック内のそれぞれの物理ページに、ホストシステムから与えられるユーザデータを書き込む際に、当該ユーザデータを書き込む物理ページに、当該ユーザデータに対応する論理ページを示す番号と共に、当該物理ページと同じグループに属する他の物理ページに格納されているユーザデータに対応する論理ページを示す番号を書き込む。

(もっと読む)

メモリコントローラ及びメモリコントローラを備えるフラッシュメモリシステム、並びにフラッシュメモリの制御方法

【課題】データの書き換えにおいて、書き換え後のデータを、書き換え前のデータと同じ物理ブロックに格納できる確率を高くする。

【解決手段】所定の期間毎に、論理ゾーンに含まれるそれぞれの論理ブロックに対する書き込み比率を算出し、この書き込み比率に基づいて、それぞれの論理ブロックに分配する予備論理ページの分配数の比率を決定する。この予備論理ページの分配数の比率に基づいて、それぞれの論理ブロックに分配するマッピング論理ページを決定する。

(もっと読む)

メモリコントローラ及びメモリコントローラを備える不揮発性メモリシステム、並びに不揮発性メモリの制御方法

【課題】物理ページ(PP)を複数個含む物理ブロック(PB)からなる不揮発性メモリにおける論理ページ(LP)とPPの対応関係を、それぞれのPPに簡易な情報を書き込むことにより管理する。

【解決手段】PB内の先頭のPBから末尾のPPに向かう書き込み順序で、データが書き込まれると共に、当該データが書き込まれたPPに、先頭のPPから当該PPまでのそれぞれのPPに対応するLPを示す情報を含むページ管理情報が書き込まれる。それぞれのLPに対応する最新のデータが書き込まれているPPを特定するときに、PBに書き込まれているページ管理情報のうち、書き込み順序が後のPPに書き込まれているページ管理情報が優先的に参照される。ページ管理情報に含まれる情報は所定の配列順序で配列されており、同じLPを示す情報が複数個あるときは、配列順序が後の情報が優先される。

(もっと読む)

データ供給装置、データ供給方法およびそれを搭載した電子機器

【課題】複数のシステムに必要とされるデータを格納するメモリの容量を削減する。

【解決手段】不揮発性メモリ10は、複数のシステムに共通のデータであって、その一部にダミーデータを含む共通データと、ダミーデータのアドレスを示す置換アドレスデータと、ダミーデータと置換すべき複数のシステムそれぞれに固有の固有データと、を格納する。一時メモリは、不揮発性メモリからロードされた共通データおよび複数のシステムそれぞれの固有データを格納する。制御回路は、あるシステムからのリクエストを受けたとき、一時メモリから、共通データを先頭アドレスからダミーデータの直前のアドレスまで順に読み出し、続いてリクエストを発したシステムの固有データを読み出し、続いて共通データをダミーデータの直後のアドレスから最後のアドレスまで読み出す。インタフェース回路は、一時メモリから読み出されたデータを、リクエストを発したシステムに供給する。

(もっと読む)

半導体記憶装置、その制御方法および情報処理装置

【課題】コマンド応答速度および書き込み効率が改善される半導体記憶装置を提供すること。

【解決手段】キャッシュメモリとしての第1の記憶部と、ページ単位で読み出し及び書き込みが行われ、ページ単位より大きなブロック単位で消去が行われる不揮発性半導体メモリに含まれる第2及び第3の記憶部と、不揮発性半導体メモリの記憶領域を、1以上の前記ブロックに対応付けられた論理ブロック単位で、第2及び第3の記憶部に割り当てるコントローラとを備え、コントローラは、不揮発性半導体メモリのリソース使用量が所定の閾値を越えている場合に、不揮発性半導体メモリのデータを整理してリソースを増加させる整理部と、ホストから整理状態通知要求が入力されると、整理部による整理状態を判別し、その判別結果を整理状態通知としてホストへ出力する整理状態通知部とを備える。

(もっと読む)

メモリコントローラ、メモリコントローラを備えるフラッシュメモリシステム、並びにフラッシュメモリの制御方法

【課題】アクセス要求により頻繁に指定される論理ブロックに対応する物理ブロックへのアクセスを効率的に行う。

【解決手段】アクセス要求により、そのときまでに指定された論理ブロックについて、その論理ブロックに対応する物理ブロックにアクセスするための論理ブロック情報が所定個数保持される。この論理ブロック情報の保持では、優先順位の高い論理ブロック情報が優先順位の低い論理ブロック情報より優先される。この優先順位の管理では、アクセス要求により頻繁に指定される論理ブロックに対応する論理ブロック情報の優先順位が高くなる。アクセス要求を受けたときに、そのアクセス要求により指定された論理ブロックに対応する論理ブロック情報が保持されていれば、その保持されている論理ブロック情報に基づいて指定された論理ブロックに対応する物理ブロックへのアクセスが行われる。

(もっと読む)

メモリ管理装置

【課題】不揮発性半導体メモリの寿命を延ばす。

【解決手段】本発明の一態様に係るメモリ管理装置1は、第1の半導体メモリと、第1の半導体メモリよりもアクセス可能上限回数の小さい不揮発性の第2の半導体メモリとのうちの少なくとも一方に記憶される各データの特性に基づいて生成され、当該各データの配置領域を決定するヒントとなる配置ヒント情報14を管理する。メモリ管理装置1は、配置ヒント情報14とメモリ使用情報11とメモリ固有情報12とに基づいて、書き込み対象データに対して第1の半導体メモリと第2の半導体メモリとのメモリ領域の中から、書き込み領域を決定する管理部15を具備する。配置ヒント情報14の生成は、オペレーティングシステムによって行われる。

(もっと読む)

フラッシュメモリモジュール

論物変換情報を、第1の変換情報と第2の変換情報とで構成する。フラッシュメモリモジュールのコントローラは、起動の際に第1の変換情報を復元し、第1の変換情報を復元した後にホストからアクセスコマンドの受信が可能となり、アクセスコマンド受信可能となった後に、第2の変換情報を復元する。 (もっと読む)

メモリ管理装置を含む情報処理装置及びメモリ管理方法

【課題】書き換え回数又は読み出し回数に制限のある不揮発性メモリを効果的に利用可能とする。

【解決手段】本発明の一例のメモリ管理装置1を含む情報処理装置は、第1のメモリ8と、不揮発性の第2のメモリ9とを含む混成メモリ2に対する書き込み位置を指定する書き込み先論理アドレスと、書き込み対象データとを、プロセッサ6bから受け付ける受付手段18と、第2のメモリ9へのアクセス回数が第1のメモリ8へのアクセス回数より少なくなるように、書き込み先論理アドレスに対応する書き込み先物理アドレスを決定するアドレス決定手段19と、書き込み先論理アドレスと書き込み先物理アドレスとを関連付けたアドレス変換データ13を、記憶手段17に記憶するアドレス管理手段20と、混成メモリ2における書き込み先物理アドレスの示す位置に、書き込み対象データを書き込む書き込み手段21とを具備する。

(もっと読む)

ノンユニフォームアクセスメモリにおけるスケーラブルなインデックス付け

多数のレコードにスケールし、高トランザクションレートを提供するインデックスを構築するための方法及び装置である。ノンユニフォームアクセスメモリデバイスが、そのメモリデバイスにとって効率的であるIO(入力/出力)トラフィックに遭遇しながら、インデックス付けアルゴリズムがそのアルゴリズムにとって自然(効率的)である方法で行うことを保証するために、新しいデータ構造及び方法が提供される。インデックス付けアルゴリズムによって見なされた論理バケットを、メモリデバイス上の物理バケットにマップする、あるデータ構造である変換テーブルが作成される。このマッピングは、ノンユニフォームアクセスSSD及びフラッシュデバイスへの書込み性能が強化されるようにするものである。バケットを集め、大きい順次書き出しとして、メモリデバイスへ順次書き出すために、もう1つのデータ構造である連想キャッシュが使用される。インデックス付けアルゴリズムによって必要とされる(レコードの)バケットでキャッシュをポピュレートするために、方法が使用される。フリー消去ブロックの生成を容易にするために、追加のバケットが、デマンド読出し中に、或いはスキャベンジング処理によって、メモリデバイスからキャッシュへ読み出されてもよい。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】不揮発性半導体記憶素子内のブロックの消去回数を減少させるとともに、書き込み効率の向上を実現する。

【解決手段】コントローラ10は、複数のデータを第一の単位で第一の記憶領域11に記憶する第一の処理と、第一の記憶領域11から出力されるデータを、第一の単位の二以上の自然数倍かつ第三の単位よりも小さい第一の管理単位で第四の記憶領域14に記憶する第二の処理と、第一の記憶領域11から出力されるデータを、第一の管理単位の二以上の自然数倍である第二の管理単位で第三の記憶領域13に記憶する第三の処理と、第四の記憶領域14内で最も古い割り当て順序を持つ第三の単位の領域を、第二の記憶領域12に移動する第四の処理と、第二の記憶領域12内の有効データを選択し、第二の単位の空き領域を持つ第三の単位の領域にコピーする第五の処理とを実行する。

(もっと読む)

1 - 20 / 173

[ Back to top ]