Fターム[5B060AA17]の内容

メモリシステム (7,345) | アロケーション、リロケーション (1,705) | オーバレイ構造、制御 (10)

Fターム[5B060AA17]に分類される特許

1 - 10 / 10

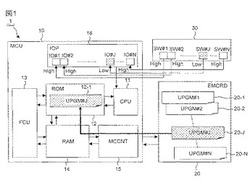

データ処理システム

【課題】オンチップする事ができる不揮発性メモリの記憶容量以上に大きな規模のプログラムやパラメータを用いたデータ処理の高速化と円滑化を実現することができるデータ処理システムを提供する。

【解決手段】オンチップする事ができる不揮発性メモリの記憶容量以上に大きな規模のプログラムやパラメータを半導体データ処理装置の外部に接続された不揮発性半導体メモリデバイスに格納し、半導体データ処理装置は外部から与えたれた情報の判別結果に応答して、内部で必要なプログラムやパラメータを不揮発性半導体メモリデバイスからダウンロードしてオンチップの不揮発性メモリを書き換える。プログラムを書き換えたときは、そのプログラムを先頭番地から実行させるソフトウェアリセット処理を行う。

(もっと読む)

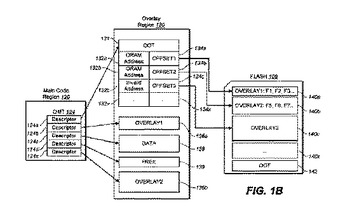

フラッシュメモリ記憶装置における動的メモリ割当てに起因する自己エビクションの回避

携帯用のフラッシュメモリ記憶装置のオペレーティングファームウェアは、実行可能ではない割合に大きなファイル記憶メモリに格納される。それは、実行可能なメモリに収まるオーバーレイに論理的に分解される。デッドスペース、あるいは頻繁にアクセスされるオーバーレイの1つまたはグループの中にあるべき関数を不必要に分離することを最小にすると同時に関数呼び出しを効率的に編成するために、オーバーレイのサイズは様々であってよい。データ割当てを必要とする関数を有するオーバーレイについて、データ割当てはオーバーレイのエビクションを引き起こすことがある。この自己エビクションは完全にあるいは初期実行時後に回避され、エビクションされたオーバーレイはデータのために確保された領域の外側の領域に再ロードされる。  (もっと読む)

(もっと読む)

情報処理システムのデータスワップ方法及び情報処理システム並びにその制御プログラム

【課題】スワップの効率化を図る。

【解決手段】複数のプログラム32のうちの1つのプログラムが先行して実行されているときに、或るイベントが発生して上記1つのプログラムがアイドリング状態に移行されて他のプログラムが新たに起動され、メモリ4の主記憶領域41aの記憶領域を使用しようとしたときに、その記憶容量が不足しているときに、スワップ対象のデータそのもの、又はスワップ対象のデータとプログラム記憶媒体3からメモリ4の主記憶領域41Aにデータを展開した元のデータとの差分のどちらをスワップさせるかを,予め記憶しておいた判定情報に基づいて行う。

(もっと読む)

メモリコントローラ、不揮発性記憶装置、不揮発性記憶システム及びメモリ制御方法

【課題】フラッシュメモリに対するインターフェイス部の処理をプログラマブルにすることで、複数種のフラッシュメモリに対応可能にする際、プログラム格納用RAMの容量を削減し、更に高速アクセスおよび省電力を実現する。

【解決手段】プログラムダウンロード部107がプログラム選択部105の選択指示に応じてメモリインターフェイス部103が実行するプログラムを選択的に不揮発性メモリ140からダウンロードするので、RAM104の容量を削減することができる。また、コントロール部102での処理に並行してプログラムダウンロード部107がプログラムをダウンロードするので、ダウンロードに要する時間的オーバーヘッドが不要となる。更に、ホスト160からのコマンドに応じた必要なプログラムを選択するようにしたので、不要なプログラムを毎回ダウンロードする必要がなく、結果的に省電力を実現できる。

(もっと読む)

情報再生装置および情報再生方法

【課題】ハードウエア機能への依存を抑制した情報再生処理装置および情報再生処理方法を提供する。

【解決手段】データが一時保存される第1メモリ14と、第1メモリ14から供給されたデータを復号化する復号化手段16と、復号化手段16による復号後のデータを一時保存する第2メモリ18と、復号化手段16から供給されたデータをデコードする第1および第2デコーダ20、22と、第1デコーダ20あるいは第2デコーダ22によるデコード後のデータを一時保存する第3メモリ24と、第2メモリ28あるいは第3メモリ24のメモリ領域が再生処理に十分であるか否かを判断する判断手段Dと、判断手段Dによって第2メモリ16あるいは第3メモリのメモリ領域24が十分であると判断された際に情報再生処理を並列処理とし、第2メモリ18あるいは第3メモリ24のメモリ領域が十分ではないと判断された際に情報再生処理を直列処理とする切替手段SWを有する。

(もっと読む)

動的メモリ管理方式

【課題】RAMの容量が小さな組み込み機器において、動的メモリを使用したシステムではメモリが枯渇してシステムが不安定になる、または動作しなくなる可能性があるという課題を有する。

【解決手段】メモリブロックを動的に獲得、返却する動的メモリ管理方式において、獲得したメモリブロックにデータ書き込みが完了した後にデータを書き換えないことを示すデータを付加するステップと、メモリブロックが参照されている数を計測しデータに付加するステップと、書き込み完了時のデータの内容を他のメモリブロックのデータ内容と比較するステップと、前記比較するステップによる比較結果が同一の場合に一方のメモリブロックのみを保持し他方のメモリブロックを返却するステップとを含むことによって、使用するメモリ量を削減し、メモリの枯渇を防ぐことでシステム全体の安定性を向上させる。

(もっと読む)

データ多重化記憶装置及び処理装置

【課題】限られた記憶容量を有効に或いは効率的に利用可能な記憶装置を提供する。

【解決手段】FPGAにおいて、リコンフィギュラブル回路12から出力される複素データIとQとが、一定の多重化条件に合致する場合には、多重化回路241は、対応するデータIとQを多重化してメモリ20に格納する。メモリ20からデータを読み出す際には、分離回路242が、多重化されているデータをIとQに分離して元のデータを再生して出力する。再生されたデータは、必要に応じて、リコンフィギュラブル回路12に再度入力される。

(もっと読む)

情報処理装置およびメモリアドレス空間割り当て方法

【課題】物理メモリに割り当て可能なメモリアドレス空間のサイズを変更することが可能な情報処理装置およびメモリアドレス空間割り当て方法を実現する。

【解決手段】CPU111のメモリアドレス空間に主メモリ116をI/Oデバイスよりも優先して割り当てるメモリサイズ優先モードが指定された場合、CPU111によって実行されるシステムBIOSは、標準メモリアドレス空間201および少なくともメモリ/MMIOアドレス空間202内の一部に主メモリ116を割り当てる。一方、CPU111のメモリアドレス空間にI/Oデバイスを主メモリ116よりも優先して割り当てる拡張デバイス優先モードが指定された場合、システムBIOSは、使用可能なメモリサイズが標準メモリアドレス空間201のメモリサイズに制限されるように標準メモリアドレス空間201に主メモリ116を割り当てる。

(もっと読む)

リアルモードにて1M以上のメインメモリを利用するx86系計算機

【課題】通常、OSが起動する前はBIOSがリアルモードで動作するようになっている。また、BIOSがOS起動ドライブとして認識可能なドライブはFDD、IDE接続のHDD等であり、他のドライブを起動ドライブとする場合には、ドライバをメインメモリにロードして実行する必要がある。しかしながら、ドライバが1Mバイト以上のメモリ領域を必要とする等の理由により、ドライバを1Mバイト以下のメモリ領域に直接ロードすることができない場合がある。

【解決手段】CPUの動作モードをリアルモードとプロテクトモードとに切り換えて、プロテクトモード又は、リアルモードにて利用可能なメモリ領域にロードされている情報と、プロテクトモードにて利用可能なメモリ領域にロードされている情報とを交換しながら実行する。

(もっと読む)

仮想マシンに配置された再配置可能な実行ファイルをロードするための方法および装置

【課題】 インプレース実行可能なファイルの仮想マシンへのロードを促進するシステムを提供する。

【解決手段】 本発明のシステム(100)は、インプレース実行可能なファイル(104)を仮想マシン(102)にロードすることにより作動する。仮想マシンにおいて、ファイル(104)は、ファイル104内でメモリ位置を示す内部ポインタおよびインプレース実行可能なファイルがロードされるように構成されるメモリにおいてターゲット位置を特定するターゲットメモリアドレスを含む。本システムはファイル(104)が実際にロードされる実際のメモリアドレスを決定する。実際のメモリアドレスおよびターゲットメモリアドレスが異なる場合、本システムはオフセット値を生成し、オフセット値によってファイル(104)内のそれぞれの内部ポインタを調整し、内部ポインタがファイル(104)内の意図する位置を示すことを可能にする。

(もっと読む)

1 - 10 / 10

[ Back to top ]