Fターム[5B060CC04]の内容

メモリシステム (7,345) | アクセスタイミング制御 (460) | アクセス同期/非同期制御 (24)

Fターム[5B060CC04]の下位に属するFターム

装置間の同期/非同期制御 (6)

ウェイト信号に関するもの (8)

Fターム[5B060CC04]に分類される特許

1 - 10 / 10

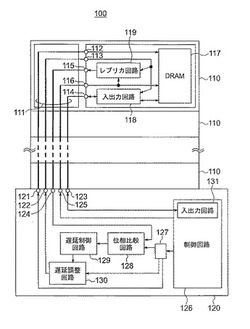

半導体装置

【課題】被制御チップの出力回路から制御チップの入力回路へ伝送されるデータ信号の位相を、入力回路に供給される同期信号の位相に一致させる。

【解決手段】半導体装置は、第1の被制御チップ110とそれと積層する制御チップ120を備える。第1の被制御チップは、同期信号に応じてデータ信号を出力する第1の回路117と、そのデータ信号を遅延同期信号に同期してデータ端子へ出力する入出力回路118と、出力回路を模した回路であって、遅延同期信号に同期してレプリカ信号を第1のレプリカ端子へ出力するレプリカ回路119とを含む。制御チップは、同期信号を出力し、データ信号を受ける第1の制御回路126と、同期信号を遅延させて遅延同期信号として出力する遅延調整回路130と、レプリカ信号の位相と同期信号の位相とを比較する位相比較回路128と、位相比較回路の比較結果に基づいて遅延調整回路の遅延量を制御する遅延制御回路129とを含む。

(もっと読む)

半導体メモリシステム

【課題】プログラムを並列化したときに消費電流のピーク期間の重なりを防止する。

【解決手段】実施形態に係わる半導体メモリシステムにおいて、複数の半導体メモリ1の各々は、連続する複数の動作を含む内部シーケンスを実行すると共に各動作の終了後に待機期間を有し、待機期間中に次の動作の開始を予告する2ビット以上の予告信号STAをメモリコントローラ28へ通知すると共に、メモリコントローラ28から内部シーケンスの再開命令を受けたときに次の動作を開始する。メモリコントローラ28は、複数の動作の各々について、動作期間及び消費電流のピーク期間に関する管理テーブルを備え、複数の半導体メモリ1のうち所定の半導体メモリから予告信号STAを受けたとき、管理テーブルに基づいて、所定の半導体メモリに対して再開命令を通知する。

(もっと読む)

フラッシュメモリ処理装置及びフラッシュメモリのポーリング方法

【課題】無駄なポーリングや無駄な待ち時間がないフラッシュメモリ処理装置及びフラッシュメモリのポーリング方法を実現することを目的にする。

【解決手段】本発明は、フラッシュメモリにデータの書き込み、消去を行うフラッシュメモリ処理装置に改良を加えたものである。本装置は、フラッシュメモリのデータの書き込みまたは消去の開始から終了時間を測定する時間測定手段と、この時間測定手段の測定結果により、フラッシュメモリにデータの書き込みまたは消去の開始から測定時間後、割込み信号を出力する割込み手段と、この割込み手段の割込み信号により、フラッシュメモリの終了確認を行う処理手段とを備えたことを特徴とする装置である。

(もっと読む)

メモリシステム、メモリ装置、およびメモリ装置の制御方法

【課題】 データの伝播遅延や消費電力も軽減されたメモリシステム、メモリ装置およびメモリ装置の制御方法を提供する。

【解決手段】 メモリシステム1は、コマンド信号およびアドレス信号ADを出力し、データ信号DQを入出力するメモリコントローラ2と、メモリコントローラ2からのコマンド信号およびアドレス信号ADを入力し、データ信号DQを入出力するNVメモリ4と、メモリコントローラ2からのコマンド信号およびアドレス信号ADを入力し、データ信号DQを入出力する第2メモリ装置と、を備え、コマンド信号、アドレス信号ADおよびデータ信号DQは直接に接続され、NVメモリ4のライト動作と、SDRAM3のライト動作とは共に同じデータレイテンシで且つ同時に行なわれることを特徴とするメモリシステムである。

(もっと読む)

データ信号処理装置、画像処理装置、画像出力装置、および、データ信号処理方法

【課題】バスのプロトコルに応じてデータ信号を変換する場合にメモリ資源の浪費を抑制する。

【解決手段】データ信号処理装置は、第1のプロトコルに従ってデータ信号を伝送する第1のバスと、第2のプロトコルに従ってデータ信号を伝送する第2のバスと、第1のバス上に伝送される第1のデータ信号を第2のバス上に伝送される第2のデータ信号に変換する変換部と、を備える。変換部は、第1のバスを介して第1のデータ信号の供給を受け、第1のデータ信号の供給に同期して、第2のバスに前記第2のデータ信号を出力する。

(もっと読む)

データ転送制御方法及びその装置とシステム

【課題】 データ転送及びデータ処理をスムースに行なうための予備動作を実現可能なデータ転送制御方法及びその装置とシステムを提供する。

【解決手段】 CPUを内蔵し、主メモリとデータ処理用の処理手段との間のデータ転送を制御するデータ転送制御装置で、主CPUからの処理手段でのデータ処理の指示を受けて、データ転送とデータ処理を制御するプログラムを主メモリからロードし、プログラムに従ってデータ転送記処理手段に指示し、データ処理を処理手段に指示し、処理手段からのデータ転送又はデータ処理の完了を通知する信号を受けて、次のデータ転送の準備を行なう。

(もっと読む)

インターフェイス回路

【課題】

従来のインターフェイス回路は、消費電力の増大を防ぎ、かつ、回路の観測性を高めながら、基準クロックに対する遅延時間が大きく異なる信号に対応することができない問題があった。

【解決手段】

本発明にかかるインターフェイス回路は、基準クロックに対して所定時間以上の遅延を有する信号を基準クロックに同期させる第1の同期化回路44−1、3と、所定時間未満の遅延を有する信号を基準クロックに同期させる第2の同期化回路44−2、4と、基準クロックに対する信号の遅延時間に基づいて判定信号を出力する遅延判定回路45と、予め設定された値に基づいて第1、第2の同期化回路のいずれか一方の出力を指定するパス設定信号を出力する遅延判定設定回路46と、判定信号とパス設定信号とのいずれか一方の信号に基づいて、第1、第2の同期化回路のいずれか一方の出力を選択して出力する遅延選択回路48とを有するものである。

(もっと読む)

OneNANDフラッシュメモリ及びそれを含んだデータ処理システム

【課題】OneNANDフラッシュメモリ及びそれを含んだデータ処理システムを提供する。

【解決手段】制御ロジックは、同期バーストブロック読み出し動作のための不揮発性メモリコアのアドレス及び命令情報を貯蔵するように構成されたレジスタを具備し、選択されたメモリブロックのページに対するデータ読み出し動作が前記レジスタの再設定なしに前記貯蔵されたアドレス及び命令情報に応じて連続して実行されるように不揮発性メモリコアを制御し、各データ読み出し区間の間ページバッファ内のデータが第1及び第2バッファメモリに交互に伝送されるように不揮発性メモリコア及び前記第1及び第2バッファメモリを制御し、ページバッファ内のデータが第1及び第2バッファメモリに全部伝送される際インタラプト信号を非活性化させ、第1及び第2バッファメモリ内のデータが全部クロック信号に同期して外部に伝送される際、前記インタラプト信号を活性化させる。

(もっと読む)

データ記録方法

【課題】 データの書き込みを高速化できるデータ記録方法を提供すること。

【解決手段】 ページ単位では、書込み所要時間および消去所要時間の速いフラッシュメモリへデータが次々と書き込まれていくが、ブロック単位では、書込み所要時間および消去所要時間の最も遅いフラッシュメモリへの書き込みが終了するのを待って、すなわちブロック単位では、書込み所要時間および消去所要時間の最も遅いフラッシュメモリへの書き込みが終了するのに同期して、各フラッシュメモリに対しブロック単位で消去が行われ、次のブロックのページ単位の書き込みに進む。

(もっと読む)

データ記録方法

【課題】 データの書き込みを高速化できるデータ記録方法を提供すること。

【解決手段】 並列数mの全フラッシュメモリへ並列的にページを割り振り、ページ単位では、1つのバスを共有する組にされたn個の各フラッシュメモリへ、予め規定された順で、前記割り振られたページに対するレジスタ転送と書き込みを行い、ブロック単位では、前記並列数mの全フラッシュメモリのうちで前記割り振られたページに対する書込み所要時間が最も遅いフラッシュメモリで書き込みが終了するのを待って、すなわちブロック単位では、前記書込み所要時間の最も遅いフラッシュメモリへの書き込みが終了するのに同期して、前記全フラッシュメモリに対し消去を行い、次のブロックのページ単位の書き込みに進む。

(もっと読む)

1 - 10 / 10

[ Back to top ]