Fターム[5B060DA00]の内容

メモリシステム (7,345) | 可変長語、部分アクセス制御 (157)

Fターム[5B060DA00]の下位に属するFターム

アドレス境界渡り処理 (26)

部分書込、部分読出 (49)

データ圧縮、データ伸長 (55)

レコードフォーマット変更 (17)

データビット長拡大、ビット付加 (6)

Fターム[5B060DA00]に分類される特許

1 - 4 / 4

半導体記憶装置

【課題】予め設定されたデータ長と異なるデータ長を送信してくる外部システムとの間でも支障のないデータの授受を行うことができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、データを記憶するメモリ部21と、ホストデバイスから供給された論理アドレスをメモリ部21の物理アドレスに変換する機能を有し、メモリ部21の読み出し及び書き込みを制御するメモリコントローラ22とを備える。メモリコントローラ22は、外部装置からアクセスされるデータの長さが予め規定された所定のデータ長よりも短い場合、内部でデータ長を整合させてメモリ部21と外部装置との間のデータの授受を行う。

(もっと読む)

直列および並列モードを有するメモリシステムおよび方法

1つまたは複数のメモリバンクへアクセスする方法を、直列アクセスを使用して、または並列アクセスを使用して実行することができる方法およびシステムが提供される。直列モードでは、各リンクは独立型の直列リンクとして動作する。対照的に、並列モード中は、これらのリンクは、1つの並列リンクとして共通で動作する。直列モードでは、入出力制御はリンクごとに独立して受け取られるが、並列モード中は、1組の入出力制御がすべてのリンクによって共通で使用される。  (もっと読む)

(もっと読む)

高速用途においてパラレルデータをシリアルデータに変換する方法および装置

パラレルデータをシリアルデータに変換する方法および装置。より具体的には、パラレルデータ(d0、d4、d2、d6、d1、d5、d3、d7)を受信するように構成されたデータパイプライン(62)と、データパイプライン(62)からのパラレルデータ(d0、d4、d2、d6、d1、d5、d3、d7)を受信するように配置され、パラレルデータ(d0、d4、d2、d6、d1、d5、d3、d7)をシリアルに出力するように構成された複数のスイッチ(70)を備えるバイナリソートロジック(64)とを備えたパラレルシリアル変換器(52)を提供する。 (もっと読む)

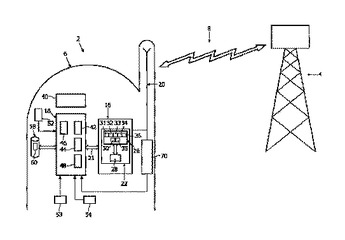

様々な外部メモリサイズとエンディアンネスに対して適応できるデータ処理装置

データ処理装置(D)は、エンディアン方式でプログラムの少なくとも一部を画定するデータを記憶する外部メモリ(EM)と、Nビット幅を有するメモリバス(MB)を介して外部メモリ(EM)に接続され、i)プログラムで起動するように適応された組込プロセッサ(EP)、ii)プログラムの少なくともブートストラップコードを記憶する内部メモリ(IM)、iii)メモリバス(MB)に接続された外部メモリインタフェース(EMI)、並びに iv)内部メモリ(IM)及び外部メモリインタフェース(EMI)を組込プロセッサ(EP)に接続するプロセッサバス(PB)を含む集積回路(IC)とを含む。外部メモリ(EM)は、また、それのサイズ(N/8ビットに等しい)及び記憶されたプログラムデータのエンディアン方式を表現する値を有するNビットデータワードを選択されたアドレスで記憶もする。データ処理装置(D)は、また、組込プロセッサ(EP)及び外部メモリインタフェース(EMI)と結合され、外部メモリの選択されたアドレスで外部メモリインタフェース(EMI)によって読み込まれたNビットデータワードの8ビットの少なくとも一部から外部メモリ(EM)のストレージのサイズ及びエンディアン方式を推定し、推定された外部メモリサイズに従って外部メモリインタフェース(EMI)の幅を設定し、ストレージの推定されたエンディアン方式に従って組込プロセッサ(EP)のデータ処理モードを設定するように構成された設定手段(CM)も含む。  (もっと読む)

(もっと読む)

1 - 4 / 4

[ Back to top ]