Fターム[5B062DD03]の内容

マイクロコンピュータ (2,258) | チップ内蔵回路 (296) | 命令先取りバッファ (6)

Fターム[5B062DD03]に分類される特許

1 - 6 / 6

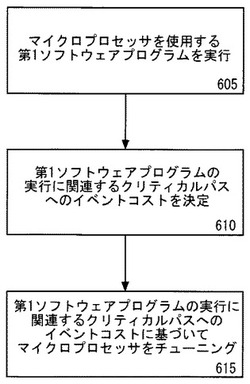

クリティカルパスに基づく解析のための性能モニタリングアーキテクチャ強化

【課題】マイクロアーキテクチャの性能をモニタリングし、そのモニタリングされた性能に基づいてマイクロアーキテクチャをチューニングする方法及び装置を提供する。

【解決手段】シミュレーション、解析上の推論、リタイアメントプッシュアウト測定、全体実行時間、およびインスタンス当たりのイベントコストを決定する他の方法によって性能がモニタリングされる。インスタンス当たりのイベントコストに基づき、マイクロアーキテクチャおよび/または実行ソフトウェアは、性能を強化すべくチューニングされる。

(もっと読む)

マイクロコンピュータ

【課題】スキップ処理が実行可能に構成されている場合、CPUに対してマスク不能割込み要求が発生すると、その発生時点で適切に処理できるマイクロコンピュータを提供する。

【解決手段】エバチップ1のCPU10は、スキップ命令の実行を開始する場合にはスキップ状態フラグを格納領域22aにセットし、その間はデータの書き込みが禁止され、スキップ命令の実行中にNMIが発生すると、スキップ状態フラグを退避回路55に退避させると共に、格納領域22aのスキップ状態フラグをリセットしてからNMI処理を開始し、当該割込み処理が終了すると、退避回路55より読み出したスキップ状態フラグを格納領域22aにセットしてスキップ命令の実行を継続する。

(もっと読む)

マイクロコンピュータ

【課題】 マイクロコンピュータにおいてプログラムメモリとして使用される強誘電体メモリの寿命延長を使用効率の低下を伴うことなく実現する。

【解決手段】 分岐命令検出部は、CPUによりメモリから取得される命令コードと所定の分岐命令の命令コードとの一致を検出する。命令情報格納部は、分岐命令検出部により命令コードの一致が検出された場合、所定の分岐命令とそれに続いて実行される命令とに関して、CPUにより指定されるアドレスとCPUによりメモリから取得される命令コードとを格納する。アドレス比較部は、CPUにより指定されるアドレスと命令情報格納部に格納されているアドレスとの一致を検出する。メモリアクセス制御部は、アドレス比較部によりアドレスの一致が検出された場合、CPUによるメモリからの命令コードの取得を禁止し、CPUに命令情報格納部から命令コードを取得させる。

(もっと読む)

半導体集積回路装置

【課題】クリティカルパス上でのデータ信号の遅延による誤動作を防ぐことができる半導体集積回路を得ることが目的である。

【解決手段】命令先読み回路120は、マスタ104から命令が実行されていることを示すop_fetch信号、マスタ104が発行した命令のデータ受信を示し、次の命令を実行できることを示すready信号、クロックマスク回路130から供給されるクロックclk1信号及びメモリ108からのリードデータrdata1が入力され、クリティカルパス420を通る命令が予め予測されており、将来実行されることを示すcri_flag信号が出力される。なお、前提条件は、クリティカルパス420を通る際、第2のAND回路522に接続されるrdata1の値は、命令コードが乗算命令”011”のときである。

(もっと読む)

データプロセッサ

【課題】共有リソースである演算回路を簡単な手続によって優先的に利用可能にする。

【解決手段】中央処理装置(CPU0,CPU1)と複数の演算回路(FPU0,FPU1)を備え、中央処理装置はフェッチした一の命令に基づいて一の演算回路にコマンドを与え、フェッチした他の命令に基づいて他の演算回路にコマンドを与えることが可能なデータプロセッサ(DPRCS1)に、どの演算回路がコマンドを実行中であるかを示す第1情報と、演算回路にどの中央処理装置から次のコマンドの実行が予約されているかを示す第2情報の格納に利用される記憶回路(BREG,RREG)を設ける。既にコマンド実行中であるときは記憶回路の第2情報を用いて次の演算コマンドの実行を予約することにより、実行終了後、速やかに当該演算回路に演算コマンドを振り当てて実行させることができる。

(もっと読む)

ハードウェアマルチスレッドシステムおよび方法

【課題】マイクロコントローラのマルチスレッド性能の特性を向上させ、マイクロコントローラ用ソフトウェアコードの開発に有用な情報を提供するシステムを提供する。

【解決手段】マルチスレッド式マイクロコントローラは、本質的にリアルタイムで、例えば1つまたは2、3のクロックサイクルで、いくつかのマルチスレッドシステムコールを実行するように構成されたスレッド制御ハードウェア(論理)を有するスレッド制御ユニットを含む。システムコールは、ミューテックスロック、待機条件、および信号命令とを含むことができる。スレッドコントローラは、マルチスレッドシステムコールの実行に用いられるいくつかのスレッド状態、ミューテックス、および条件変数レジスタを含む。スレッドは、空き、実行、作動可能および待機を含むいくつかの状態間を移行することができる。

(もっと読む)

1 - 6 / 6

[ Back to top ]