Fターム[5B062FF02]の内容

マイクロコンピュータ (2,258) | システムの拡張 (70) | シングルチップにおける拡張 (60) | メモリの拡張 (25)

Fターム[5B062FF02]の下位に属するFターム

内部/外部メモリの選択、切換 (10)

Fターム[5B062FF02]に分類される特許

1 - 15 / 15

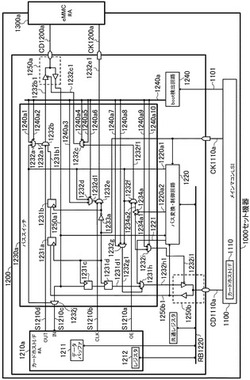

セット機器及びセット機器の制御方法

【課題】メモリカードに保存したマイコンのアプリケーション命令コードを読み出しを高速化する。

【解決手段】メインマイコンLSI1100とカードホストLSI1200とメモリカード1300aとがそれぞれ所定のカードバス仕様に準拠したカードバスの信号線CD1110a,CD1200a及びクロック信号線CK1110a,CK1200aにより接続されている。boot検出回路1240のバススイッチ制御信号1240aによりI/O回路1250a、1250bの制御方向をアプリケーション命令コードを読み出す方向に設定する。

(もっと読む)

マイクロコンピュータ及びデータ処理システム

【課題】マイクロコンピュータにおいてメモリアクセスコマンドの生成などの点でシリアルアクセスメモリに対するアクセスのオーバーヘッドを減らす。

【解決手段】 CPUが出力するアクセス要求に含まれるアドレス及びコマンドに基づいて、シリアルフラッシュメモリに、チップ選択信号及びクロック信号を供給し、前記クロック信号に同期してメモリアドレス及びメモリコマンドを出力してシリアルアクセスメモリのアクセス制御を行うシリアルメモリインタフェースコントローラ(60)をマイクロコンピュータに搭載し、このシリアルメモリインタフェースコントローラには、前記アクセス要求に応答するメモリアドレス及びメモリコマンドに基づくデータリードを完了したとき、そのリードデータの最後のメモリアドレスに続くアドレスへのリードアクセス要求以外のアクセス要求を検出するまで前記チップ選択信号の活性状態を維持する動作モードを採用する。

(もっと読む)

シングル・チップ半導体集積回路装置の製造方法、プログラムデバッグ方法、マイクロコントローラの製造方法

【課題】短時間で、マスクROMを備えたシングル・チップの半導体集積回路装置を製造すること。

【解決手段】第1の集積回路(12)および第1のマスクROM(11)を有する第1の半導体集積回路基板(10)とプログラマブルROM(15)とが搭載された第1の半導体集積回路装置(20)の状態において、第1のマスクROM(11)が第1の内部バス(13)から電気的に切り離された状態で、その第1の集積回路(12)とプログラマブルROM(15)とを使用して決定された最終的なプログラムを、第1の半導体集積回路基板(10)と実質的に同一構成の第2の半導体集積回路基板(100)の第2のマスクROM(110)に記憶することにより、最終製品としての第2の半導体集積回路装置(200)を製造する。

(もっと読む)

複数メモリ特定用途向けデジタル信号プロセッサ

回路基板(210)と、この回路基板上に実装された1又はそれ以上のデジタル信号プロセッサ(100)とを含む集積回路装置(200)を提供する。デジタル信号プロセッサ(100)は、データユニット(120)及び制御ユニット(110)を含み、データユニットは、特定のアプリケーションの少なくとも一部を実行するために特定の数式を実行するように構成された関数コア(124)と、特定のアプリケーションを実行するためのコマンドを制御ユニット及びデータユニットに送信するように構成された1又はそれ以上の命令を記憶する命令メモリ(122)とを含み、制御ユニットは、複数のメモリバンク(130、140)と関数コアの間の、特定のアプリケーションを実行するためのデータの流れを制御するように構成され、複数のメモリバンクは、1又はそれ以上のデジタル信号プロセッサの各々に結合されるとともに、回路基板上に統合された少なくとも2又はそれ以上のローカルメモリバンク(130)を含む。 (もっと読む)

マイクロコンピュータ

【課題】新たなインタフェース仕様に対応することが可能なマイクロコンピュータを提供する。

【解決手段】バスコントローラ30は、固定バス制御部34と、可変バス制御部35とを含む。CPU10は、固定バス制御部34を介して内部ROM50にアクセスし、可変バス制御論理情報を読み出して、プログラム可能な可変バス制御論理部35にマッピングする。そして、CPU10は、可変バス制御論理部35を介して外部バス62と接続された外部メモリに対してアクセスする。

(もっと読む)

シングルチップデータプロセッサ及び半導体集積回路

【課題】接続している別のデータプロセッサから、当該データプロセッサの内部機能若しくは当該データプロセッサの外付け回路を効率良く利用する方法を提供する。

【解決手段】一のデータプロセッサ101に他のデータプロセッサ100との接続を可能にするためのインタフェース手段119を設け、このインタフェース手段に、一のデータプロセッサ内の内部バス108に他のデータプロセッサをバスマスタとして接続可能にする機能を設け、内部バスにメモリマップされた周辺機能を前記インタフェース手段を介して外部より当該他のデータプロセッサが直接操作できるようにする。これにより、データプロセッサは、実行中のプログラムを中断することなく、別のデータプロセッサの周辺機能等を使うことが可能となる。要するに、一のデータプロセッサは別のデータプロセッサの周辺リソースを共有することが可能になる。

(もっと読む)

マイクロコンピュータ、データ書込み装置およびその書込み方法

【課題】近年、不揮発性メモリ内蔵マイコンに搭載される不揮発性メモリの容量が格段に増加してきたことにより、不揮発性メモリに対する書込み処理の簡便化および高速化が望まれてきている。

【解決手段】本発明のデータ書込み装置の書込み方法は、フラッシュライタからフラッシュマイコンへ書込みデータ等を送信する場合には、MDATA信号の立ち下がりエッジ信号をハンドシェーク用の信号として使用し、一方、フラッシュマイコンからフラッシュライタへ応答データを送信する場合には、MDATA信号の立ち上がりエッジ信号をハンドシェーク用の信号として使用することを特徴とする。

(もっと読む)

シングルチップマイクロコンピュータ

【課題】多数の割込によるデータ転送および使用者毎の固有の処理を可能とし、かつ処理効率が向上できる半導体集積回路装置、さらにこの半導体集積回路装置のデバック効率の向上が可能なエミュレータを提供する。

【解決手段】シングルチップマイクロコンピュータであって、CPU1/2、ROM1/2、RAM1/2、RAMP、タイマ、パルス出力回路、SCI、A/D変換器、IOP0〜IOP11、割込コントローラ、バスコントローラ、クロック発振器の機能ブロックから構成され、これらの機能ブロックは、CPU1,ROM1およびRAM1がIAB1,IDB1、CPU2,ROM2およびRAM2がIAB2,IDB2、RAMPがPAB,PDBに接続され、このIAB1,IAB2およびPABと、IDB1,IDB2およびPDBとの独立したインタフェースによってCPU1とCPU2が並列に動作可能となっている。

(もっと読む)

ソフトウェア熱プロファイルの分析生成のコンピュータによって実施する方法、データ処理システム、およびコンピュータ・プログラム

【課題】 ソフトウェア熱プロファイルの分析生成のためにコンピュータによって実施する方法、データ処理システム、およびコンピュータ使用可能コードを提供する。

【解決手段】 熱プロファイルを生成するために、1セットのプロセッサによってプログラムを実行するために1セットの命令ストリームを分析して、分析情報を作成する。分析情報に基づいて温熱指数を生成する。

(もっと読む)

マイクロコンピュータ

【課題】 プログラムサイズの増加を極力抑制した上で、多様な周辺機能をソフトウエアによって実現することができるマイクロコンピュータを提供する。

【解決手段】 マイクロコンピュータ10のCPU11を、Lタスクに記述されている周辺機能命令を1命令として実行処理可能に構成する。そして、CPU11は、オペランドで指定されている汎用レジスタ30より周辺機能命令の実行に要する情報を取得する共に、当該命令の実行結果に関する情報を汎用レジスタ30に格納する。

(もっと読む)

半導体集積回路装置

【課題】CPUおよびフラッシュメモリとDRAMとの2種類のチップを1パッケージ化したパッケージ構造において、回路的にも、外部接続端子数の低減、1パッケージ化による実装面積の縮小を図り、コストダウンが可能な半導体集積回路装置を提供する。

【解決手段】CPU、メモリおよび周辺回路などを含むマイクロコンピュータとフラッシュメモリとが搭載されたチップ(MF)と、DRAMとASICなどのロジック回路とが搭載されたチップ(AD)とからなり、このチップ(MF)とチップ(AD)との接続において、アドレス端子(A0〜A10)、データ入出力端子(D0〜D31)、電源端子(Vcc)、接地端子(Vss)、ロウアドレスストローブ端子(バーRAS、カラムアドレスストローブ端子バーCASL,バーCASH,バーCASHL,バーCASHH)などの制御端子は、1パッケージ化された半導体集積回路装置の同じ外部接続端子に接続されている。

(もっと読む)

半導体集積回路

【課題】 セキュリティ情報の取得など、悪意あるプログラムの外部空間での利用を排除する。

【解決手段】 ブートジャンプコードの実行によって、第2外部端子(T4)を介して取り込まれたキーコードが、予め設定されたコードと一致するか否かを判別する第1機能と、この第1機能によって、上記第2外部端子を介して取り込まれたキーコードが、予め設定されたコードと一致すると判断された場合に、外部のメモリ(20)に記憶されているプログラムをフェッチして実行する第2機能とを、中央処理装置(12)によって形成する。上記第2外部端子を介して取り込まれたキーコードが、予め設定されたコードと一致しない限り、上記半導体集積回路の外部に配置されたメモリに記憶されているプログラムをフェッチして実行することはないので、悪意あるプログラムの外部空間での利用を排除することができる。

(もっと読む)

CPU電力配送システム

中央処理装置(CPU)が開示される。このCPUは、CPUダイおよび該CPUダイに接合された電圧調整器ダイを三次元実装レイアウトにおいて含む。 (もっと読む)

半導体装置

【課題】 動的に回路構成を再構成可能な半導体装置にて、使用するメモリのサイズを任意に変更できるようにする。

【解決手段】 複数のメモリ33−1〜33−5と、コンフィグレーション情報を出力するシーケンサー11と、シーケンサーから供給されるコンフィグレーション情報に応じて、メモリ領域を再構成するメモリ再構成回路32とを備え、メモリ再構成回路によりメモリの割り当てを動的に変更するようにして、使用目的に応じてメモリ構成を再構成しメモリのサイズを任意に変更することができるようにする。

(もっと読む)

シングル・チップ・データ処理装置及びデータ処理装置

【課題】 簡単な構成によりシンクロナスダイナミック型RAMの動作マージンを拡大させてアクセスできるシングル・チップ・データ処理装置を提供する。

【解決手段】 複数の端子を含み、かつ、複数のモードの中の1つが上記複数の端子を介して供給された信号によって決定される外部メモリとともに用いられる。その一部に上記外部メモリが割り付けられるアドレス空間をアクセス可能とするアドレス信号を供給する中央処理装置と、上記外部メモリの上記複数の端子に電気的に連結される複数の外部端子と、上記中央処理装置と上記複数の外部端子に電気的に連結されたメモリ制御信号発生回路を含む。上記メモリ制御信号発生回路は、上記中央処理装置から発生されたアドレス信号の1部にしたがって、上記外部メモリのモードをセットする。

(もっと読む)

1 - 15 / 15

[ Back to top ]