Fターム[5B079CC03]の内容

計算機・クロック (4,131) | 位相/タイミングの調整 (657) | 調整手段 (364) | 静電容量の調整 (10)

Fターム[5B079CC03]に分類される特許

1 - 10 / 10

クロック供給装置およびクロック供給方法

【課題】インピーダンス整合のためのコストを増大させずに高周波クロック信号の伝送効率を高める。

【解決手段】一実施形態に係るクロック供給装置は、クロック信号を生成するクロックジェネレータ21に接続される第1伝送線路T1と、このクロックジェネレータ21の出力インピーダンスとは異なる入力インピーダンスを持つクロック供給先12Aに接続される第2伝送線路T2と、第1および第2伝送線路T1,T2を容量結合するキャパシタCP1と、第1伝送線路T1上でクロック信号の反射を抑制するプルアップ抵抗RP1と、分圧で得られる電位をクロック信号の基準電位として第2伝送線路T2に印加する一対の分圧抵抗RP3,RP2とを備える。一対の分圧抵抗RP3,RP2は第2伝送線路T2上のインピーダンスをクロック供給先12Aの入力インピーダンスに整合させる抵抗比に設定される。

(もっと読む)

クロック分配回路及びクロックスキュー調整方法

【課題】消費電力とクロックスキューを最小限に抑える。

【解決手段】クロック分配回路は、クロック分配領域に格子状に配置され、クロックメッシュを駆動する複数のクロックドライバと、各クロックドライバに対して格子状に割り当てた分割領域毎に、クロックドライバが駆動するクロックメッシュの配線容量及びクロックメッシュに接続した回路素子のクロック端子容量を抽出し、分割領域毎に抽出した総容量から必要なクロックドライバの駆動力を割り出して、ディジタルデータとして保持するクロックドライバ駆動力保持回路と、各分割領域内で必要なクロックドライバの駆動力保持データと、上下方向及び左右方向の分割領域内で必要なクロックドライバの駆動力保持データとをそれぞれ分割領域毎の抵抗比率により平均化して、クロックドライバの駆動力を調整するクロックドライバ駆動力制御回路とを有する。

(もっと読む)

遅延パルス発生回路

【課題】クロックパルスを用いずに入力パルスを遅延させた出力パルスを生成する。

【解決手段】外部からの入力パルス信号に応じて動作を開始し、その動作の開始から第1の遅延時間T1後に出力信号を変化させる第1の遅延回路102と、その出力信号に応じて、動作の開始から第1の遅延時間T1後に動作を開始し、その動作の開始から第2の遅延時間T2後に出力信号を変化させる第2の遅延回路104と、を備え、その出力信号の変化に応じて入力パルス信号を遅延させた出力パルス信号を生成する。

(もっと読む)

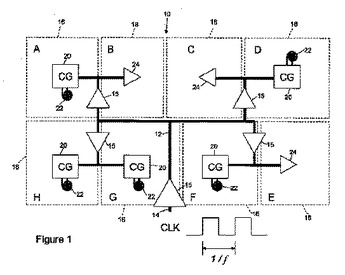

共鳴クロックされたシステムのためのクロック分配ネットワークアーキテクチャ

本明細書に開示されているのは、基準クロックを運ぶための分配ネットワークと、基準クロックによる同期作動のために基準クロックを受信するように分配ネットワークと結合された複数のサーキットドメインと、を含んでいるデジタルシステムである。複数のサーキットドメインの各サーキットドメインは、共鳴クロック信号を発生させるように基準クロックによって駆動されるそれぞれのクロックジェネレータと、共鳴クロック信号に従って作動するためにクロックジェネレータと結合されたそれぞれの回路であって、回路は、共鳴クロック信号のための容量性負荷を含む、回路と、回路の容量性負荷に共鳴するために回路およびクロックジェネレータに結合されたそれぞれのインダクタンスと、を含む。  (もっと読む)

(もっと読む)

信号伝送回路、CMOS半導体デバイス、及び回路基板

【課題】大規模集積回路内に形成される長い信号線路或いは接続される被駆動回路の数が多数存在する等により形成される静電容量の容量値が大きい信号線路の信号伝送特性を改善する。

【解決手段】駆動回路及び被駆動回路の電源電圧の中点電圧を出力し、出力インピーダンスが低い付加回路を信号線路に接続し、信号線路の電位を電源電圧の中点電圧に維持すると共に、駆動回路から出力される駆動信号を中点電圧(被駆動回路の閾値電圧)を中心に小振幅で励振させ、この小振幅に制限された駆動信号により被駆動回路を駆動させる。

(もっと読む)

メモリモジュール

【課題】クロック信号に同期して動作するメモリ素子群を搭載するメモリモジュールにおいて、その使用条件に応じてクロックの位相を微調整することができるようにする。

【解決手段】クロック信号CLKに同期して動作するメモリ素子群12を搭載するメモリモジュールが、入力クロック信号の位相と、出力クロック信号をフィードバックループに通すことにより得られるフィードバック信号の位相と、が一致するように調整された出力クロック信号を作成する位相同期ループ回路20と、外部からの信号に応じて、前記フィードバックループの負荷を選択的に切り替える切替え手段80と、を具備するように構成される。

(もっと読む)

DLL回路及びこれらを備えた半導体装置

【課題】 従来のDLL回路では、DQバッファ系の経路とDQレプリカ系の経路とを備え、DQレプリカ系の遅延時間をモニタすることでDQレプリカ系の遅延時間としている。しかし、温度、電圧、製造ばらつき等により、DQバッファ系の遅延時間とDQレプリカ系の遅延時間との誤差が発生するという問題がある。

【解決手段】 ZQキャリブレーション結果により遅延量を可変させる遅延量可変回路を、DQレプリカ系の経路に挿入する回路構成とする。DQレプリカ系の経路の遅延量を可変とし、DQバッファ系とDQレプリカ系とのタイミングスキュー差を一定になるように調整する。ZQキャリブレーション結果は温度、電圧、製造ばらつきに対応して変動することから、これらの変動に対応した遅延量を得ることでスキュー差を一定にできる高精度のDLL回路及びこのDLL回路を備えた半導体装置が得られる。

(もっと読む)

半導体集積回路の設計装置と方法並びにプログラム

【課題】

ばらつきによるクロックスキューの増大を抑止する装置、方法の提供。

【解決手段】

クロックツリーの分岐がツリー末端側に近く位置するように、クロックツリーの構成を変更する。

(もっと読む)

デジタル回路のコントローラ基板

【課題】同期型メモリ回路で、DIMMを含めたメモリ搭載容量に依存せずコストアップすることなく単純回路構成でメモリ動作周波数を向上させるデジタル回路のコントローラ基板を提供する。

【解決手段】中央処理演算装置(以下CPU)と、CLK同期型DRAM(以下メモリ)と、CPU/メモリコントローラと、周辺回路制御機能を有するASICで構成されるデジタル回路のコントローラ基板において、CLK同期でデータアクセスを行うメモリ回路で、1つのメモリバスに複数のメモリデバイスがコントローラ基板上またはDIMM(メモリモジュール)により接続される構成において、前記基板上に実装されるメモリデバイス数(メモリ容量)および実装されるDIMMの枚数(容量)とは無関係にメモリ−ASIC間の信号の配線伝播遅延時間を一定にしてCLK周波数を向上するようにした。

(もっと読む)

ASIC及び画像形成装置

【課題】 クロックによる過渡電流の集中を防ぐことで、不要輻射を抑える。

【解決手段】 1チップのASICを構成する回路で少なくとも同一クロックで駆動されるブロックは、複数ブロックに分割され、当該ASICのクロック入力端子からのクロックの伝播遅延が各ブロック毎に互いに異なるように、当該クロック入力端子から、各ブロックのクロック入力端子までのクロックのデレーを、その間に挿入されるクロックバッファのゲートのデメンジョン(ゲート幅、ゲート長)を変更してタイミング調整設計を行い、その結果を用いてブロックのレイアウト及び配線が行われる様にASICを提供する。

(もっと読む)

1 - 10 / 10

[ Back to top ]