Fターム[5B125CA22]の内容

リードオンリーメモリ (43,397) | 目的、効果 (6,321) | 機密保持、セキュリティ、コピー防止 (76)

Fターム[5B125CA22]に分類される特許

1 - 20 / 76

メモリカード、ストレージメディア、及びコントローラ

ホスト装置、装置、システム

OTPメモリ

【課題】より秘匿性の高いOTPメモリを提供する。

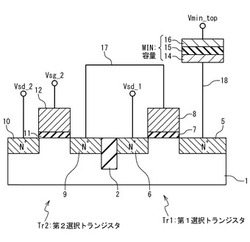

【解決手段】メモリセルは、第1ノードと第2ノードとの間に電流経路を形成するメモリトランジスタと、第3ノードと第4ノードとの間に電流経路を形成し、第3ノードがメモリトランジスタのゲートと配線により接続された選択トランジスタと、第1ノードに接続されたキャパシタとを備える。メモリトランジスタに対して、ゲート酸化膜が破壊されず劣化してゲートリーク電流が増大する程度の高電圧を印加することによりデータが書き込まれる。キャパシタの蓄積電荷のリークの有無によりデータを読み出すことが可能となる。ゲート酸化膜の劣化箇所は物理解析で識別できないため、秘匿性が高い。

(もっと読む)

半導体記憶装置、及び半導体記憶装置の動作方法

【課題】光学的に書き込み状態が解析されることがなく、安価に実現することのできる、半導体記憶装置及びその動作方法を提供すること。

【解決手段】半導体記憶装置は、書込み処理が行われていない第1半導体記憶素子と、書込み処理が行われた第2半導体記憶素子とを具備する。前記第1半導体記憶素子及び前記第2半導体記憶素子は、それぞれ、不純物が注入された半導体層を備える抵抗部と、前記抵抗部に接続される、第1コンタクトと、前記抵抗部に接続される、第2コンタクトとを具備する。前記第1半導体記憶素子における前記半導体層の不純物の活性化率は、前記第2半導体記憶素子のそれとは異なっている。

(もっと読む)

半導体装置

【課題】抵抗変化型記憶素子を用いた半導体装置の耐タンパ性を向上させること。

【解決手段】半導体装置は、1ビットのセルデータを記憶するユニットセル(10)と、制御回路(100)とを備える。ユニットセル(10)は、n個(nは2以上の整数)の抵抗変化型記憶素子(31)を備える。それらn個の抵抗変化型記憶素子(31)のうち少なくとも1つが、セルデータが記録される有効素子(40)である。セルデータの読み出し時、制御回路(100)は、少なくとも有効素子(40)を選択し、有効素子(40)に記録されているデータをセルデータとして読み出す。

(もっと読む)

不揮発性半導体記憶装置

【課題】電源電圧の供給停止を検出せずに、かつメモリセルからデータを読み出すことなく、書き換え動作中の電源遮断が容易に検出できる不揮発性半導体記憶装置を提供する。

【解決手段】行列上にフラッシュメモリセルが配置されたメモリアレイ99は、メモリブロック8_0〜8_3に分割される。メモリブロック8_0〜8_3は、データを記憶するノーマルメモリセルNCと、消去動作の完了の有無表わすためのフラグメモリセルFCを含む。制御回路6は、メモリブロックの消去動作が終了後に、フラグメモリセルFCを書込状態に設定する。

(もっと読む)

データ書き込み装置およびデータ書き込み方法

【課題】全てのROMに共通するデータと個々のROMごとに異なるデータとを1つの工程で書き込むことができ、また、書き込みデータの秘匿性を保つことができるデータ書き込み装置およびデータ書き込み方法を提供する。

【解決手段】データ書き込み装置10は、経路切り替え手段11とデータ書き込み手段12とデータ格納手段13とを備え、経路切り替え手段11は、制御装置から受信した共通データをデータ格納手段13に記憶させ、制御装置から共通データの書き込み開始の要求があった場合は、データ格納手段13から読み出した共通データをデータ書き込み手段12に出力し、制御装置から個別データの書き込み開始の要求があった場合は、制御装置から受信した個別データをデータ書き込み手段12に出力し、データ書き込み手段12は、経路切り替え手段11から入力されたデータをデータ書き換え可能な記憶素子の所定領域に書き込む。

(もっと読む)

フラッシュメモリの優先順位付き消去のためのデバイスおよび方法

【課題】優先順位付き消去機能を持つ記憶デバイスおよび方法を得る。

【解決手段】記憶メモリは、少なくとも一つのフラッシュ・ユニットを持ち、各フラッシュ・ユニットは、複数のブロックを持つ。コントローラは、複数のブロック内へデータを書き込むよう、各ブロックへ、データの消去優先度と相互に関連する消去優先度を指定するよう、そして緊急消去コマンドを受信すると即座に、各ブロックの消去優先度に従って各ブロック内のデータを消去するよう構成される。コントローラは、第一のフラッシュ・ユニット内で任意の順序で複数のブロック内へ、データの書き込みを実行するよう構成されることが好ましい。そして以降のフラッシュ・ユニットへの書き込みは、第一のフラッシュ・ユニット内の順序に相関性を持って実行される。消去は、複数のブロックの少なくともいくつかに対して、消去を完了する前に消去をアボートすることを含むことが好ましい。

(もっと読む)

集積化埋込型フラッシュ及びSRAMメモリを有する移動通信装置

【課題】フラッシュ及びSRAMのアクセス時間を改善し、ASICを使用する移動電話機のパワー消費を低減する。

【解決手段】改善されたアクセス時間を備えるフラッシュ及びSRAMメモリを特定用途集積回路(ASIC)の中に埋込む。フラッシュメモリシステムは、個々のフラッシュマクロの組及びフラッシュマクロにアクセスするためのフラッシュメモリコントローラ132を備えるように構成されたフラッシュメモリ列130を含む。フラッシュメモリコントローラは、フラッシュマクロの一つへ、同時にフラッシュマクロの他の一つから読出している間に、書込むための読出し間書込みユニット144,146を含む。フラッシュメモリコントローラは、また、プログラム可能な待機状態レジスタ138及びフラッシュメモリ列の異なる部分のための別々のパスワードを提供するパスワードレジスタ140を含む。

(もっと読む)

初期シード生成方法とそれを利用するフラッシュメモリ装置及びメモリシステム

【課題】信頼性を向上させることができるフラッシュメモリ装置及びそれを含むメモリシステムが提供される。

【解決手段】ここに提供されるフラッシュメモリ装置は行と列に配列されたメモリセルのアレイと、前記アレイに格納されるデータをランダム化するように構成されたランダム化及びデランダム化回路と、を含み、前記ランダム化及びデランダム化回路は前記アレイに格納されるデータがランダムデータであるか否かにしたがって前記ランダムデータに対応する初期シードを生成し、前記初期シードに基づいてランダムシークェンスを発生し、前記ランダムシークェンスに基づいて前記ランダムデータをランダム化させる。

(もっと読む)

半導体装置

【課題】ゲート電極へのチャージアップの有無を解析する手法を用いても、書き込まれた情報を解析することができないようにするアンチヒューズをメモリ素子として有する半導体装置を提供する。

【解決手段】基板10は第1導電型、例えばp型の半導体基板(例えばシリコン基板)である。アンチヒューズは、ゲート電極120及び第2導電型拡散層130を有している。第2導電型拡散層130は基板10に形成されており、例えばn型である。第1コンタクト122はゲート電極120に接続している。第2コンタクト142は第1コンタクト122と同一層に形成されており、基板10のうち第2導電型拡散層130が形成されていない領域に接続している。第2コンタクト142は第1コンタクト122に隣接している。

(もっと読む)

半導体装置、メモリ装置への書込方法、メモリ装置からの読出方法、及び半導体装置の製造方法

【課題】電極へのチャージアップの有無を解析する手法を用いても、書き込まれた情報を解析することができない半導体装置を提供する。

【解決手段】第1半導体素子100は基板上に形成されており、第1絶縁膜、第1電極、及び第1拡散層を備えている。第2半導体素子200は基板に形成されており、第2絶縁膜、第2電極、及び第2拡散層を備えている。第2電極は第1電極に接続している。制御トランジスタ300は、ソース及びドレインの一方が第1電極及び第2電極に接続しており、ソース及びドレインの他方がビットラインBL1に接続しており、ゲート電極がワードラインWL1に接続している。第1電位制御ラインSL1−1は第1拡散層に接続しており、第1拡散層の電位を制御する。第2電位制御ラインSL1−2は第2拡散層に接続しており、第2拡散層の電位を制御する。

(もっと読む)

不揮発性半導体記憶装置

【課題】チップ面積の増大を抑制しつつ、データの機密性を高めることが可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、セット状態及びリセット状態の遷移が可能なメモリセルMCと、パーマネント状態に固定されたメモリセルMCとを含むメモリセルアレイ1と、制御回路とを備える。メモリセルアレイ1に書き込まれるデータは、セット状態及びリセット状態の遷移が可能なメモリセルMC及びパーマネント状態のメモリセルMCをそれぞれ少なくとも1つずつ用いてメモリセルアレイ1内に記憶される。制御回路は、データ保持時に少なくとも1つのセット状態及びリセット状態の遷移が可能なメモリセルMCをリセット状態からセット状態に書き換え、データ読み出し時にセット状態のメモリセルMCを、リセット状態に書き換えた後、読み出し動作を実行する。

(もっと読む)

不揮発性半導体記憶装置及びそのデータ消去方法

【課題】 不揮発性半導体記憶装置の高速化を実現すること。

【解決手段】 本発明の不揮発性半導体記憶装置は、電気的に書き換え可能なメモリセルが配列された複数のメモリブロックでなるメモリセルアレイを有する不揮発性半導体記憶装置であって、複数のメモリブロックは、それぞれ、第1の領域及び第2の領域からなり、複数のメモリブロックのうちの選択したメモリブロックの第2の領域にあるメモリセルのうちの特定のメモリセルのデータが第1の値であれば、選択したメモリブロックへのデータの書込又は消去が許容され、特定のメモリセルのデータが第2の値であれば、選択したメモリブロックへのデータの書込又は消去が禁止され、メモリブロックへのデータの書込又は消去が許容される場合、選択したメモリブロックにおける全てのメモリセルのデータを消去する前に、選択したメモリブロックにおける第1の領域の全てのメモリセルのしきい値を正とする。

(もっと読む)

半導体装置

【課題】格納される命令コード自体の機密保護を実現すると同時に、命令コードに基づく処理を実行できる半導体装置を提供する。

【解決手段】半導体装置102は、複数のブロックに分割されたデータ領域と、ブロック毎にアクセスを禁止するための保護情報が格納される保護情報領域とを含む不揮発性メモリ2と、保護情報領域に格納された保護情報を読出部22と、いずれかのブロックに対するアクセスの禁止を解除する前に、当該ブロックに格納されているデータを消去する制御部20と、データ領域に格納された命令コードを読出して処理を実行する演算部92とを含む。そして、制御部20は、読出部から受けた保護情報に基づいて、保護情報によりアクセスを禁止され得るブロックへのアクセスを許可するか否かを決定し、かつ、演算部から命令コードの読出しを行なうためのアクセス要求を受けると、保護情報にかかわらず当該アクセスを許可する。

(もっと読む)

暗号鍵保護方法及び半導体記憶装置

【課題】ファイルデータを不正アクセスから保護する。

【解決手段】管理情報によってパスワード参照が有効とされる第1状態では、パスワード照合結果に応じてファイルデータを鍵で復号することを許可し、管理情報によってパスワード参照が無効とされる第2状態では、パスワード入力がなくとも上記ファイルデータを上記鍵で復号することを許可する。上記第1状態にあることを意味する管理情報は、第1スレッショルド電圧(9112)及びそれよりも低い第2スレッショルド電圧(9111)を用いて記録する。上記第2状態にあることを意味する管理情報は、第3スレッショルド電圧(9111)及び上記第3スレッショルド電圧(9111)よりも低い第4スレッショルド電圧(9110)を用いて記録する。パスワード有効状態では、パスワード管理ブロック内のメモリページ上にパスワード無効状態を意味するエントリ履歴が残留しないようにする。

(もっと読む)

偽造に耐えられる固定記憶のオプションをもつ不揮発性記憶装置

【課題】永続的な、偽造に耐えられる記憶の利点と消去可能な記憶の利点とを結合して、不揮発性記憶装置の使用を更にフレキシブルなものとする。

【解決手段】本発明は、記憶ユニットFM、アクセス変更の指示を受信する手段CON、及びアクセス変更の指示に応答して記憶ユニットへのアクセスを変更する手段WPを有する不揮発性記憶装置を提案する。アクセス変更の指示の受信前のアクセスは、データが記憶ユニットに記憶することができ、且つ既に記憶されているデータを変更することができるように行われ、アクセス変更の後のアクセスは、既に記憶されているデータの少なくとも幾つかが変更不可能であるが、なお読取ることができるように行われる。既に記憶されているデータの少なくとも幾つかへのアクセスは、アクセス変更の指示の受信に応答してアクセス変更の後に逆にできない。

(もっと読む)

NAND型フラッシュメモリデバイス及びNAND型フラッシュメモリのデータ消去方法

【課題】情報機器等においてファイルシステムでデータ管理されるNAND型フラッシュメモリの記憶データを高速に、かつ、完全に消去し、データの漏洩を防止することができるNAND型フラッシュメモリデバイス、並びにNANDフラッシュメモリのデータ消去方法の提供。

【解決手段】NAND型フラッシュメモリに情報機器のユーザデータを記録するパーティションを設けておくとともに、NAND型フラッシュメモリデバイスのプロセッサが、ホストから発行された、コマンドコードと前記パーティションの消去対象領域の先頭セクタアドレスとセクタ数からなる消去コマンドを解釈して、前記パーティションに記憶されている全データを消去する。

(もっと読む)

半導体記憶装置

【課題】読み出しデータだけでなく、書き込みデータについても十分にセキュリティ機能を強化した半導体記憶装置を提供する。

【解決手段】データを格納するデータ格納部と、逐次更新されるキーコードを格納するキーコード格納部とを備えたメモリと、データ格納部に格納されたデータを読出し、データスクランブル用キーコードに従って暗号化して出力するデータスクランブル回路と、暗号化されて入力されるデータをデータデスクランブル用キーコードに従って暗号を解除し、データ格納部に書込むデータデスクランブル回路と、キーコード格納部から取出した第1のキーコードに応じた擬似乱数を発生させて第2のキーコードとし、データスクランブル回路に供給すると共に、データデスクランブル回路に供給する擬似乱数発生回路と、第1のキーコードと第2のキーコードとを演算して第3のキーコードを作製し、キーコード格納部に書き込むことにより第1のキーコードを第3のキーコードに更新する演算回路とを設ける。

(もっと読む)

携帯型データキャリアのメモリにデータを安全に格納する方法

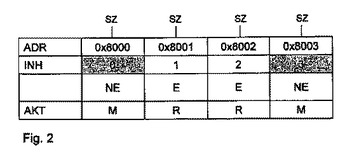

発明は携帯型データキャリアの多値メモリにデータを安全に格納する方法に関する。多値メモリは、少なくとも3つの値(E,NE)をそれぞれがとり得る、1つまたはいくつかの多値メモリセル(SZ)を有する。少なくとも3つの値は、それぞれについて、メモリセル(SZ)のそれぞれの値(E,NE)が有効または無効と定義されている、相異なるデータ内容を表す。それぞれのメモリセル(SZ)の値(E,NE)は所要保全レベルに応じて選択的に有効または無効と定義される。  (もっと読む)

(もっと読む)

1 - 20 / 76

[ Back to top ]