Fターム[5B125EK02]の内容

リードオンリーメモリ (43,397) | 外部接続構成、外部出力情報 (1,198) | RAM、ROM (333)

Fターム[5B125EK02]の下位に属するFターム

EEPROM、フラッシュ (16)

Fターム[5B125EK02]に分類される特許

1 - 20 / 317

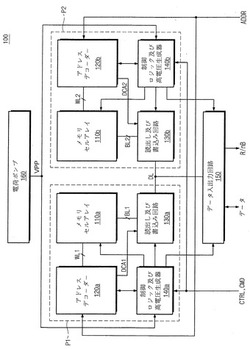

不揮発性メモリ装置及び不揮発性メモリ装置を制御するコントローラの動作方法

【課題】向上された動作速度を有する不揮発性メモリ装置及び不揮発性メモリ装置を制御するコントローラの動作方法を提供する。

【解決手段】本発明の不揮発性メモリ装置は、データのプログラム、読出し又は消去を遂行する第1プレーン、データのプログラム、読出し又は消去を遂行する第2プレーン、及び第1プレーン又は第2プレーンから共通バスを通じて伝送されるデータを外部へ出力し、外部から受信されるデータを、共通バスを通じて第1プレーン又は第2プレーンへ伝送するデータ入出力回路を含む。第1プレーンでプログラム、読出し又は消去が遂行される時、データ入出力回路は共通バスを通じて第2プレーンとデータを交換する。

(もっと読む)

半導体記憶装置

【課題】読出速度が速い半導体記憶装置を提供する。

【解決手段】フラッシュメモリ3は、選択ビット線BLをプリチャージするプリチャージ回路45と、定電流源50と、電流検知型のセンスアンプ23と、選択ビット線BLがメモリアレイMA2に属する場合は、選択ビット線BLおよび定電流源50をそれぞれセンスアンプ23の入力ノードLBT,LBBに接続し、選択ビット線BLがメモリアレイMA3に属する場合は、選択ビット線BLおよび定電流源50を入力ノードLBB,LBTに接続する切換回路SWT2,SWB2,SWとを含む。したがって、ビット線BLのプリチャージとデータ読出を並列に実行できる。

(もっと読む)

不揮発性メモリ装置のデータリード方法、及びそれを行う装置

【課題】新たなリードパラメータで不揮発性メモリ装置をリードするリードリトライを行う方法、該方法を行う装置を提供する。

【解決手段】リードリトライ動作及び/またはその部属的なリードリトライ動作は、リードリトライ動作が保証(warranted)されるか否かを判断する前に初期化されるか、完了することができる。例えば、NANDフラッシュメモリ装置のページは、新たなリード電圧レベルをページのワードラインに印加して、リードリトライ動作でリードされうる。例えば、リードリトライ動作は、エラー訂正動作でターゲットページのデータの以前リードページのエラーを訂正不能と判断される前に、ターゲットページで行われる。

(もっと読む)

不揮発性メモリ装置、不揮発性メモリ装置の消去方法、不揮発性メモリ装置の動作方法、不揮発性メモリ装置を含むメモリシステム、メモリシステムの動作方法、不揮発性メモリ装置を含むメモリカード、及びソリッドステートドライブ

【課題】向上された信頼性を有する不揮発性メモリ装置、不揮発性メモリ装置の消去方法、不揮発性メモリ装置の動作方法、不揮発性メモリ装置を含むメモリシステム、及びメモリシステムの動作方法が提供される。

【解決手段】本発明の消去方法は複数のメモリセルに消去電圧を供給する段階、複数のメモリセルのワードラインに読出し電圧に読出し動作を遂行する段階、及び複数のメモリセルのワードラインの少なくとも1つのワードラインに消去検証電圧を利用して消去検証動作を遂行する段階を含む。消去検証電圧は読出し電圧より低い。

(もっと読む)

プログラム書込システム

【課題】バッテリ電圧が異なる車両の制御対象機器を制御するための、同じハードウエア構成を備えた電子制御装置に対して、正しい制御プログラム以外の書き込みを防止すること。

【解決手段】ECU104が、書込装置101から制御プログラムの提供を受けたときに、検出されたバッテリ電圧VVと、制御プログラム内の使用電圧情報110から取得した使用電圧VSとに基づき、制御プログラムの正誤を判定する。そして、正しい制御プログラムではないと判定した場合、制御プログラムのフラッシュROMへの書込処理を中止する。

(もっと読む)

画像処理装置、リフレッシュ方法およびプログラム

【課題】画像処理装置に設けられた不揮発性メモリに対して、比較的に簡素な構成で適切にリフレッシュを行うことができるようにする。

【解決手段】画像処理装置は、自装置で用いられるデータを保存する不揮発性メモリと、自装置の動作状況を認識する認識手段101と、認識手段101が認識した動作状況をと、記憶部に予め記憶された自装置の動作状況ごとの温度変化を示す動作温度情報とを用いて、不揮発性メモリのリフレッシュの要否を判定する判定手段102と、リフレッシュが必要であると判定手段102が判定した場合、不揮発性メモリをリフレッシュするリフレッシュ手段103と、を備える。

(もっと読む)

不揮発性半導体記憶装置

【課題】 BiCSメモリのような積層型メモリの書き込み動作を高速化することが可能な不揮発性半導体記憶装置を提供する。

【解決手段】 積層型のメモリセル構造を有する不揮発性半導体記憶装置であって、半導体基板上に、複数のメモリセルを積層してなるストリングを複数個配置したメモリセルアレイ11と、メモリセルアレイ11の任意のストリングをサンプルストリングとして選択し、該選択したサンプルストリングに対してデータの書き込みを行う回路12,14,16,30と、サンプルストリングの各メモリセルに対する書き込み回数をレイヤー毎に保持する書き込み回数記憶部31と、記憶部31に記憶されたレイヤー毎の書き込みパルス数を同一レイヤーの他のストリングのメモリセルの書き込み電圧の初期値に反映させる回路33とを備えている。

(もっと読む)

メモリシステム

【課題】

実施形態は、動作効率の低減を防止可能なメモリシステムを提供する。

【解決手段】

本実施形態のメモリシステムによれば、半導体チップの内部温度とアクセス可否とを対応づけたデータを保持する第1記憶部と、前記半導体チップの内部温度を計測する温度計測部と、前記データから、計測された内部温度に対応するアクセス可否を算出し、アクセス可の半導体チップに対して、シーケンスを実行し、アクセス否の半導体チップに対して、シーケンスを実行しない制御部とを備えることを特徴とする。

(もっと読む)

メモリシステム

【課題】読み出し動作開始から読み出し動作完了までの処理時間を可及的に低減する。

【解決手段】制御部は、不揮発性メモリに格納されているデータを読み出す際、読み出し電圧管理情報に記録されている読み出し電圧の値を用いて不揮発性メモリからデータを読み出して、誤り検出部が読み出されたデータに誤りを検出したとき、誤り検出部が読み出されたデータに誤りを検出しなくなるまで読み出し電圧を変更して前記不揮発性メモリからデータの再読み出しを行い、誤り検出部が読み出されたデータに誤りを検出しなくなったとき、読み出し電圧管理情報に記録されている読み出し電圧を更新する。

(もっと読む)

メモリシステム

【課題】書き換え回数制限下での実効的な書き換え容量を増大したメモリシステムを提供する。

【解決手段】実施形態のメモリシステム1は、2ビット以上の所定ビット数の記憶容量のメモリセルを複数個有する不揮発性メモリ2と、前記メモリセルの書き換え回数を管理する書き換え回数管理テーブル40を備える。実施形態のメモリシステムは、ホスト7からの書き込み要求に応じたビット数で前記メモリセルに書き込みを行い、前記書き換え回数管理テーブル40が管理する前記メモリセルの書き換え回数が所定の回数を超えた後は、前記メモリセルを前記記憶容量に依存したグループに分割し、ホストからの書き込み要求に応じたビット数の前記記憶容量に対応する前記グループの前記メモリセルに書き込みを行うコントローラ3を備える。

(もっと読む)

半導体記憶装置

【課題】1つの実施形態は、例えば、出荷後においてメモリセルの動作特性を変更できる半導体記憶装置を提供することを目的とする。

【解決手段】1つの実施形態によれば、メモリセルアレイと記憶部と選択部と起動処理部と動作制御部とを有することを特徴とする半導体記憶装置が提供される。メモリセルアレイでは、複数のメモリセルが配列されている。記憶部は、選択される候補となる複数の動作パラメータを予め記憶する。選択部は、ユーザからの変更指示に応じて、前記複数の動作パラメータのうち前記メモリセルを動作させるために使用すべき動作パラメータを選択する。起動処理部は、ユーザからの起動指示に応じて、電源を起動するとともに、前記選択部により選択された動作パラメータを前記記憶部から読み出して使用可能な状態に設定する。動作制御部は、前記起動処理部により使用可能な状態に設定された動作パラメータを使用して、前記メモリセルを動作させる。

(もっと読む)

メモリシステム

【課題】1つの実施形態は、例えば、不揮発性メモリデバイスの信頼性を改善できるメモリシステムを提供することを目的とする。

【解決手段】1つの実施形態によれば、不揮発性メモリデバイスとモニタ部と変更部とを有することを特徴とするメモリシステムが提供される。不揮発性メモリデバイスは、データを記憶する。モニタ部は、前記不揮発性メモリデバイスに対するデータの書き込み処理及び消去処理による前記不揮発性メモリデバイスの特性をモニタする。変更部は、前記モニタされた前記不揮発性メモリデバイスの特性に応じて、前記書き込み処理に要する時間が目標値に一致するように、書き込み動作とベリファイ動作とが交互に繰り返される前記書き込み処理における書き込み開始電圧の値と書き込み電圧の増加幅との少なくとも一方を変更する。

(もっと読む)

不揮発性半導体記憶装置

【課題】データ転送速度の切り替えが可能な不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置1は、不揮発性メモリ10と、第1の制御信号の立ち上がりエッジ及び立ち下がりエッジの一方に応答してデータ転送を行う第1のモードと、第2の制御信号の立ち上がりエッジ及び立ち下がりエッジの両方に応答してデータ転送を行う第2のモードとを有し、データ入力時に第1のモードを用いかつデータ出力時に第2のモードを用いるように第1及び第2のモードを切り替えるコントローラ17とを含む。

(もっと読む)

半導体メモリおよびシステム

【課題】 1つをメモリブロックの書き込み動作中に、別のメモリブロックの読み出し動作を実行することで、アクセス効率を向上する。

【解決手段】 半導体メモリは、複数ビットの書き込みデータおよび書き込みデータのパリティデータをビット毎に保持する複数のメモリ領域を有する複数のメモリブロックを有している。書き込みコマンドに応答して、メモリブロックの1つである書き込みメモリブロックのメモリ領域に、書き込みデータおよびパリティデータが順に書き込まれる。読み出しコマンドに応答して、書き込みメモリブロックを除くメモリブロックの1つにおいて、書き込みデータおよびパリティデータが供給されていないデータ線に対応するメモリ領域からデータが読み出され、書き込み動作により読み出させないデータが再生される。これにより、書き込み動作と並行して読み出し動作を実行できる。

(もっと読む)

半導体メモリ装置および復号方法

【課題】復号の処理速度が速いメモリカード3を提供する。

【解決手段】メモリカード3は、1個のメモリセルに記憶する、読み出し単位であるページが異なる3ビットのデータを、8個の閾値電圧分布に基づく確率を用いた反復計算により復号を行うときに、ハードビット読み出しのための7個の基準電圧のそれぞれと、ソフトビット読み出しのための、それぞれの基準電圧よりも低い電圧および高い電圧からなる複数の中間電圧と、からなる7組の電圧セットのうち、読み出すページに属する1ビットデータの読み出しに必要な電圧セットの電圧を選択し、選択した前記電圧セットの電圧を読み出し電圧として前記メモリセルに印加する制御を行うワード線制御部21と、対数尤度比を記憶する対数尤度比テーブル記憶部22と、読み出したデータを対数尤度比を用いてECCフレーム単位で復号をする復号器1と、を有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】リードディスターブを効率良く回避するための技術を提供する。

【解決手段】不揮発性半導体記憶装置(1)は、不揮発性記憶部(11)と、上記不揮発性記憶部の消去単位とされるブロック毎のデータを、当該ブロックとは異なるブロックに書き直すためのリフレッシュ処理を制御可能なコントローラ(12)とを含む。上記コントローラは、上記不揮発性記憶部に、第1領域とそれとは異なる第2領域とを設定し、上記第1領域のデータについてのリフレッシュ頻度が、上記第2領域のデータについてのリフレッシュ頻度に比べて高くなるように、リフレッシュトリガが発生される毎に上記第1領域及び上記第2領域についてのリフレッシュ処理を実行する。これにより、リードアクセスが繰り返される場合のリードディスターブを効率良く回避することができる。

(もっと読む)

半導体メモリおよびシステム

【課題】 プリチャージ動作を不要にすることで、読み出しアクセス時間を短縮する。

【解決手段】 メモリセルは、第1電圧線と第2電圧線の間に接続ノードを介して直列に接続され、相補の論理を記憶する一対のセルトランジスタを有する。第1制御回路は、読み出し動作時に、一対のセルトランジスタのコントロールゲートを活性化レベルに設定する。第2制御回路は、読み出し動作時に、第1電圧線を第1電圧に設定し、第2電圧線を第1電圧より高い第2電圧に設定する。読み出し回路は、読み出し動作時に、接続ノードに生成される電圧に応じて、メモリセルに保持されている論理を判定する。これにより、読み出し動作において、メモリセルに保持されている論理に応じて、接続ノードを第1電圧または第2電圧に設定できる。

(もっと読む)

不揮発性メモリ装置及びメモリコントローラとこれらの動作方法、メモリシステムの動作方法、並びにウェアレベリング方法

【課題】メモリセルの劣化度を正確に検出することができる不揮発性メモリ装置及びメモリコントローラとこれらの動作方法、メモリシステムの動作方法、並びにウェアレベリング方法を提供する。

【解決手段】本発明の不揮発性メモリ装置の動作方法は、コントローラから出力されたブロックアドレスとイレース命令とを受信する段階と、ブロックアドレスに相応するブロックに対して、イレース命令によって行われるイレース動作が完了するまで、イレース動作に関連したパラメータ値を変更する段階と、最後に変更されたパラメータ値に相応する情報を保存する段階と、コントローラから出力された命令によって、情報をコントローラに伝送する段階と、を有する。

(もっと読む)

ワードライン昇圧回路、記憶装置、集積回路装置、及び電子機器

【課題】メモリーセルの特性変動やばらつき等に追従してワードラインに供給する昇圧電圧を調整するワードライン昇圧回路、記憶装置、集積回路装置、及び電子機器等を提供する。

【解決手段】メモリーセルを選択するためのワードラインに昇圧電圧を供給するためのワードライン昇圧回路140は、ワードラインに供給する昇圧電圧を生成する昇圧回路200と、昇圧電圧に基づいて、メモリーセルの読み出し電流に対応したレベル検出用電流を生成するレベル検出用電流生成回路212と、レベル検出用電流に基づいて昇圧回路200の昇圧動作の停止制御を行う昇圧停止制御回路214とを含む。

(もっと読む)

不揮発性メモリ装置

【課題】一定の上昇傾斜を有する駆動信号をメモリセルアレイに提供することによって、読出しマージン減少による信頼性の下落を防止できる不揮発性メモリ装置が提供される。

【解決手段】本発明の実施形態による不揮発性メモリ装置は、基板と直交する方向に積層された複数のメモリセルを含むメモリセルアレイと、ワードラインを通じて前記メモリセルアレイに連結された行選択回路と、前記ワードラインに提供される電圧を発生する電圧発生回路と、を含み、前記電圧発生回路は、目標電圧レベルまで段階的に増加させる方式に前記電圧を発生する。本発明の実施形態による不揮発性メモリ装置は、一定の上昇傾斜を有する駆動信号をメモリセルアレイに提供できる。したがって、読出しマージン減少による信頼性の下落が防止され得る。

(もっと読む)

1 - 20 / 317

[ Back to top ]