Fターム[5C024GX16]の内容

光信号から電気信号への変換 (72,976) | 撮像素子の細部(構造) (7,971) | セル構造 (7,384) | 回路素子 (2,124) | 3端子能動素子 (1,174)

Fターム[5C024GX16]に分類される特許

1,161 - 1,174 / 1,174

CMOSイメージセンサ

【課題】 画素リーク電流による特性低下を防止したCMOSイメージセンサの提供。

【解決手段】 PN接合を有するフォトダイオードに接続されるMOSトランジスタの導電型を決定することで、フォトダイオードのPN接合逆方向リーク電流と、MOSトランジスタのPN接合逆方向リーク電流を相殺し、光電変換による信号電荷に加算されるノイズ成分を低減する構成とする。

(もっと読む)

光センサおよび固体撮像装置

【課題】高感度でかつダイナミックレンジの広い光センサおよび固体撮像装置を提供する。

【解決手段】 光センサ部12が受光部とホトン−パルス発生回路から構成し、受光部に入射したホトンが変換された光電子を検出する光電子検出部24を、第1量子ドット26と、第1量子ドット26の両側に互いに対向して配置された光電子蓄積領域28およびゲート電極29と、これらに対して垂直方向に配置され、抵抗R1を介して電源電圧が印加されたソース電極30およびドレイン電極31から構成する。第1量子ドット26に印加されるゲート電極29を第1量子ドット26が非導通となる電位に設定し、光電子蓄積領域28に保持された所定数の光電子の電位を付加することで第1量子ドット26を導通させ、ソース電極30−ドレイン電極31間に電流が流れる。その結果、ホトン数に応じたパルス信号が生成される。

(もっと読む)

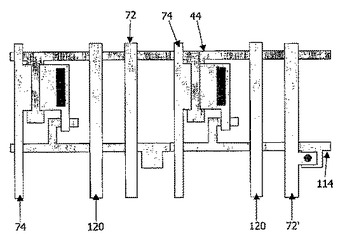

X線画像検出器

X線検出器装置が、複数のサブアレイに配置される検出器ピクセルのアレイを有する。各サブアレイにおけるピクセルは、ピクセルアレイの周囲に伸びる線量感知出力コンダクタに与えられる共通線量感知出力を共有する。ピクセルのあるサブアレイに対する線量感知出力コンダクタは、ピクセルの別のサブアレイにより占められる領域を通過し、そのことが望まないクロストークをもたらす場合がある。本発明は、複数の追加的なスクリーニング電極を、スクリーニング電極がピクセルの各サブアレイに対する線量感知出力コンダクタに実質的に隣接した状態で提供する。これらのスクリーニング電極は、線量感知出力と他のピクセル電極との間のクロストークを減らす。別の装置において、各ピクセルは、アレイの上部領域に形成される各ピクセルに対するピクセル電極を更に有し、線量感知出力コンダクタは、アレイの下部領域に形成される。中間コンダクタ層が、ピクセルの他のサブアレイに対する線量感知出力コンダクタに重なり、かつピクセルのサブアレイにより占有される領域を通るよう与えられる。  (もっと読む)

(もっと読む)

固体撮像装置、ラインセンサ、光センサおよび固体撮像装置の動作方法

高感度高S/N比を維持したままで広ダイナミックレンジ化できる固体撮像装置、ラインセンサおよび光センサと、高感度高S/N比を維持したままで広ダイナミックレンジ化するための固体撮像装置の動作方法を提供するために、光を受光して光電荷を生成するフォトダイオードPDと、光電荷を転送する転送トランジスタTr1と、少なくとも転送トランジスタTr1を介してフォトダイオードPDに接続して設けられ、蓄積動作時にフォトダイオードPDから溢れる光電荷を少なくとも転送トランジスタTr1を通じて蓄積する蓄積容量素子CSとを有する画素がアレイ状に複数個集積されてなる構成とする。 (もっと読む)

固体撮像装置およびこれを用いたカメラ

固体撮像装置110は、入射光を電荷に変換する光電変換手段(フォトダイオードPD)と、電荷を電圧に変換して出力する増幅手段(増幅アンプQ13)とを含み、2次元配列される複数の画素部10と、列毎に設けられ、当該列に属する画素部10の増幅アンプQ13からの出力電圧に含まれる雑音を除去する複数の雑音信号除去手段(ノイズキャンセル部40)と、画素部10の増幅アンプQ13からの出力電圧を増幅し、増幅した電圧をノイズキャンセル部40に出力する複数の列増幅手段(コラムアンプ70)とを備え、低消費電力で高感度化と低ノイズ化を可能にすることを特徴とする。 (もっと読む)

カメラぶれ補正方法及び装置

本発明は、カメラぶれを補正する方法を提供する。この方法は、中間露出時間中、光に対して、第1位置に位置する第1グループ画素を露出して、前記光を表すアナログ信号を提供する段階と、前記アナログ信号を第2位置に位置する第2グループ画素に転送する段階と、を含み、前記第1位置と前記第2位置との間の関係は、推定された画像中シフトに応答し、この方法は、前記第2グループ画素を露出する段階などを含む。本発明は、カメラぶれを補正する装置を提供する。この装置は、(i)中間露出時間中に光を受信する2次元画素アレイであって、前記光を表すアナログ信号を提供するように応答し、さらに、以前の受信光を表す書き込み戻し信号の受信に応じて状態が変化する2次元画素アレイと、(ii)前記画素アレイ内の第1グループに受信される光を表すアナログ信号を受け取って記憶するアナログ・メモリと、(iii)前記記憶されたアナログ信号を、第2位置に位置する第2グループ画素に戻して書き込む、書き込み戻し回路と、を備え、前記第1位置と前記第2位置との間の関係は、推定された画像中シフトに応答する。  (もっと読む)

(もっと読む)

センサ回路の列回路における画素信号のビニングおよび補間

センサ回路内の列回路からの画素信号をサンプリングおよび補間するビニング回路と、それに関連する方法である。該ビニング回路は異なるセンサ回路列ラインからのアナログ画素信号とリセット信号をサンプリングする。ビニング回路において所定数の列ラインがサンプリングされると、サンプリングした画素信号を一工程で共に平均化し、別工程でリセット信号を共に平均化する。  (もっと読む)

(もっと読む)

MOS型イメージセンサ

【課題】 1画素内に2つの光電変換素子を設けた場合に、トランジスタ数や配線数の低減を図る。

【解決手段】 アレイ状に配列された複数の画素を半導体基板に設けると共に各画素間に配線を形成したMOS型イメージセンサにおいて、各画素30,40,50,60の夫々に2つの光電変換素子31,32,41,42,51,52,61,62を設けると共に、各画素内に設けられ前記光電変換素子の不要電荷を排出するリセット用のトランジスタ33,34及びフローティングディフュージョンアンプ用のトランジスタ35,36,37の数を計5個とする。

(もっと読む)

ゲート制御電荷蓄積を用いた撮像

画素セルは、電荷を生成する光電変換素子と、制御ゲートの制御下で光生成電荷を蓄積するゲート制御電荷蓄積領域とを含む。この電荷蓄積領域は、埋込みチャネルを有する単一CCDステージとすることができ、そのため効率のよい電荷転送および低い電荷損失を得ることができる。この電荷蓄積領域は、トランジスタのゲートに隣接している。トランジスタ・ゲートは光電変換素子に隣接し、制御ゲートと共に、光生成電荷を光電変換素子から電荷蓄積領域に転送する。  (もっと読む)

(もっと読む)

フローティング・ディフュージョン・ゲート・キャパシタ付き4TCMOSイメージ・センサ

フローティング・ディフュージョン・ノードに付随するゲート・キャパシタを用いて、フローティング・ディフュージョン・ノードの蓄積容量を選択的に増やす画素セルが提供される。ゲート・キャパシタは、画素セルの他のゲートを形成するのに用いる同じ工程段階のときに同時に形成されてよい。蓄積ノードの固有容量だけで、低輝度条件下では十分であることがある。高輝度条件では、ゲート・キャパシタの選択的な起動がなされることになり、したがって蓄積ノードの容量が、ゲート・キャパシタによって提供される付加容量と合わせて増やされてよい。本発明では、電荷分配または遅れ出力信号の無い広いダイナミック・レンジと高い出力信号を生成する。このような画素セルを形成する方法は、CMOSおよびCCD画像デバイス、CMOSおよびCCD画像デバイス内、ならびにCMOSおよびCCD撮像素子の画素配列に応用することができる。  (もっと読む)

(もっと読む)

自動露光制御及び相関二重サンプリング用CMOSイメージャ

本発明の実施例によれば、自動光制御と、相関二重サンプリング処理との双方を可能にするピクセルを提供する。このピクセルは、互いに別々に読出しうる第1及び第2の光変換装置を有する。第2の光変換装置は、例えば、光変換に適した領域及びドーピングプロファイルを有するピクセルの浮動拡散領域とすることができる。イメージセンサはピクセルのアレイを有し、これらピクセルのうちの幾つか又は全てが、2つの光変換装置を有し、イメージセンサは更に、ピクセルから信号を読出す周辺回路を有する。イメージセンサの読出し回路は、第2の光変換装置により発生された電荷をモニタリングして、第1の光変換装置からいつ信号を読出すかを決定しうるようにする。  (もっと読む)

(もっと読む)

CMOS技術を用いたマトリックス・イメージ・センサー

本発明は特にデジタル写真撮影向けのマトリックス・イメージ・センサーに関する。

本発明は全画素に共通の露光制御を可能とする各画素に関する制御回路を提供する。該回路は五つのトランジスタ(T1〜T5)と、一つのフォトダイオード(PD1)及び、供給導体(Vdd)と接地とは別に以下の

― マトリックスの全画素に共通の露光制御導体(TRA)と、

― いずれか一つの行の全画素に共通の行選択導体(SEL)と、

― いずれか一つの行の全画素に共通のリセット導体(RESET)と、

― マトリックスの画素内における感光発電された電荷の行ごとの読み取り中に、画素における信号読み取りを収集するための列導体(COL)の四つの制御導体を備える。

(もっと読む)

信号処理回路

【課題】 固体撮像装置を用いたシステムにおける小型軽量化及び低消費電力化を図ることが可能な信号処理回路を提供する。

【解決手段】 固体撮像装置12から出力されたアナログ映像信号のフィードスルーレベルVfとデータレベルVdとの差分を取ってノイズ成分を除去した差分信号を生成し、可変容量素子22の容量値及び可変容量素子24の容量値の容量比に応じた利得でその差分信号を可変に増幅するので、極めて簡単な回路構成で従来例と同様の機能を具備し、小型軽量化及び低消費電力化を図ることができる。

(もっと読む)

固体撮像装置

【課題】 画素にフローティングディフュージョン(FD)型アンプを内蔵したMOS型センサの消費電力を削減する。

【解決手段】 単位画素のドレイン領域(リセットトランジスタ3を介してFD部へパルス電圧を供給するための領域)を1行毎に異なるドレイン線7に接続し、1行毎に選択的に電源パルスを供給する。この電源パルスは、少なくともFD部の信号電荷をリセットする期間と、FD部の信号電荷を検出する期間とにおいてHIGHレベル電位に設定される。

(もっと読む)

1,161 - 1,174 / 1,174

[ Back to top ]