Fターム[5C024HX48]の内容

光信号から電気信号への変換 (72,976) | 回路構成 (15,472) | 電源 (560) | 電流源 (168)

Fターム[5C024HX48]に分類される特許

1 - 20 / 168

固体撮像装置

固体撮像装置

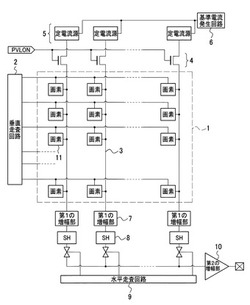

【課題】画質の劣化を抑制しつつ、消費電力を低減することができる固体撮像装置を提供することを課題とする。

【解決手段】固体撮像装置は、光電変換した信号をソースフォロワ回路により出力する複数の画素(11)と、前記複数の画素に接続される出力線(3)と、前記出力線に電流を供給する電流源回路部(5)と、前記画素のリセット状態の前記出力線の信号をクランプ容量にクランプし、その後の前記画素の非リセット状態の前記出力線の信号を増幅する第1の増幅部(7)とを有し、前記電流源回路部は、前記クランプの終了時刻より前に、前記出力線に電流を供給しない状態から前記出力線に電流を供給する状態に変化することを特徴とする。

(もっと読む)

固体撮像装置、撮像装置および撮像方法

【課題】ストリーキングを低減することができるようにする。

【解決手段】 入射された光に対応する画素読み出し信号を出力する複数の単位画素から出力された画素読み出し信号が信号線により伝達され、信号線に接続され、単位画素から画素読み出し信号を読み出すための読み出し電流を供給され、画素読み出し信号のレベルをディジタルデータに変換するための参照信号が生成され、信号線の電圧の振幅の変化を制限する閾値を参照信号のゲインに連動して切り替えて、信号線の電圧の振幅の変化が制限される。

(もっと読む)

半導体装置、X線カメラ及び電子機器

【課題】信号書き込み時間が長くなることを防ぎながら、信号振幅値が大きく、かつ、入出力関係が線形で動作する範囲を大きくすることが出来る半導体装置およびその駆動方法を提供する。

【解決手段】増幅用トランジスタ及びバイアス用トランジスタを有する半導体装置において、放電用トランジスタを設けて、プリ放電を行う。または、増幅用トランジスタ及びバイアス用トランジスタを有する半導体装置において、バイアス用トランジスタに接続されたバイアス側電源線の電位を、増幅用トランジスタに接続された増幅側電源線の電位に近づけることにより、プリ放電を行う。

(もっと読む)

固体撮像装置及びその駆動方法

【課題】列回路に係る電源線の電圧降下の違いに依存した横引きノイズや横スミアの発生を抑制することができる固体撮像装置を提供することを課題とする。

【解決手段】アレイ状に配置された複数の画素と、画素の列毎に配置されて画素からの信号を増幅する増幅回路と、ソースに電源電圧が供給され増幅回路にバイアス電流を供給する電流源トランジスタとを備える固体撮像装置にて、電流源トランジスタが飽和領域で動作しているときに、バイアス線より供給される電流源トランジスタのゲート電圧をサンプリングして保持し、電源電圧に対する電流源トランジスタのゲート電圧をサンプリングされた電圧に制御するようにして変動を抑制し、列回路に係る電源線における行毎の電圧降下の違いによる横引きノイズや横スミアの発生を抑制できるようにする。

(もっと読む)

撮像素子、制御方法、並びに、撮像装置

【課題】より多様なデータ出力を実現することができるようにする。

【解決手段】本開示の撮像装置は、行列状に構成される複数の画素のそれぞれにおいて入射された被写体の光を光電変換素子により光電変換する画素アレイと、その画素アレイの各画素の画素信号を出力するA/D変換部の数を選択する選択部と、前記選択部を制御し、要求に応じた数の前記A/D変換部を選択させる制御部とを備える。本開示は撮像素子、制御方法、並びに、撮像装置に適用することができる。

(もっと読む)

固体撮像装置及び撮像装置

【課題】S/N特性及び画質の劣化を抑制する。

【解決手段】本発明に係る固体撮像装置10Aは、行列状に配置された複数の画素セル11と、複数の垂直信号線22と、1以上の列毎に一つ設けられており、対応する列に配置された垂直信号線22に出力された信号電圧が入力される複数の列回路20とを備え、列回路20の各々は、定電流源トランジスタ115及び122を含むアンプ40と、定電流源トランジスタ115及び112とカレントミラー回路を構成するカレントミラートランジスタ172と、カレントミラートランジスタ172に電流を供給する基準電流源トランジスタ171とを備え、固体撮像装置10Aは、アンプ40に接続されている電源電圧線L11と、アンプ40及びカレントミラー回路に接続されているグランド線L12と、基準電流源トランジスタ171に接続されている電源電圧線L13とを備える。

(もっと読む)

撮像装置

【課題】製造容易化を図りつつ、画像品質の向上を図ることができる撮像装置を提供することを目的とする。

【解決手段】複数の受光素子1aを有する固体撮像素子1を備えた撮像装置であって、複数の受光素子1aおよび電圧発生回路10が形成された固体撮像素子用基板(第1半導体基板)100と、電圧発生回路10からの入力電圧を増幅して固体撮像素子用基板100に印加する基板電圧バッファ回路11の一部を構成するトランジスタQ16が形成された固体撮像素子用基板100とは別体の外部出力用デバイス基板(第2半導体基板)200とを備える。

(もっと読む)

イメージ・センサのピクセルおよびそのイメージ・センサを動作させる方法

【課題】改善された性能パラメータを有するイメージ・センサ、および、そのイメージ・センサを動作させる方法を提供する。

【解決手段】本実施例に従って、イメージ・センサのピクセルは、第1ステージ、およびそれに結合された第2ステージを含む。第2ステージは、サンプリング・キャパシタおよび減算キャパシタを含む。

(もっと読む)

固体撮像装置、固体撮像装置の制御方法、および撮像装置

【課題】複数枚のチップを接続することによって構成される固体撮像装置において、高輝度の光が入射した場合でも、ノイズの少ない良好なグローバル露光方式の画像を取得することができる固体撮像装置、固体撮像装置の制御方法、および撮像装置を提供する。

【解決手段】第1の基板と第2の基板とを電気的に接続する接続部によって、第1の基板と第2の基板とを電気的に接続する固体撮像装置であって、当該固体撮像装置が有する画素部は、第1の基板に含まれ、光電変換素子を具備する画素と、画素で発生した信号を第2の基板に供給する信号線と、第2の基板に含まれ、信号線を経由して供給された信号を蓄積する信号蓄積回路と、第2の基板に含まれ、信号蓄積回路に蓄積された信号を出力する出力回路と、を有し、当該固体撮像装置は、信号線の電圧が、所定の電圧以下にならないようにクリップするクリップ回路を、さらに有する。

(もっと読む)

補正処理装置、撮像装置および補正処理方法

【課題】より高品質の画像を得ることができ、且つ固体撮像装置が形成されるチップ面積の縮小化を図ることができる。

【解決手段】第1の基板と第2の基板とが接続部を介して電気的に接続される固体撮像装置を備える補正処理装置であって、前記固体撮像装置が有する画素は、前記第1の基板に含まれる光電変換素子と、前記第1の基板から前記接続部を介して前記第2の基板に送られた信号を出力する水平読み出し回路と、を有し、当該補正処理装置は、前記第1の基板と前記接続部との接合部分を示す接合領域の前記第1の基板上における配置パターンに応じて、前記画素から出力される信号の補正を制御する補正処理部をさらに有する。

(もっと読む)

光センサおよびそれを備えた携帯電話ならびにデジタルカメラ

【課題】低照度から高照度までの入力に対してリニアな出力を得ることが可能であるとともに、フォトダイオードの出力電流の温度依存性を補正することができる光センサを実現する。

【解決手段】光センサ(1)において、第1のアナログ−デジタル変換回路(11)に、第1のフォトダイオード(PD1)の出力電流の温度依存性を補正する温度係数を有する抵抗を備えた第1の基準電流源が備えられ、第2のアナログ−デジタル変換回路(12)に、第2のフォトダイオード(PD2)の出力電流の温度依存性を補正する温度係数を有する抵抗を備えた第2の基準電流源が備えられ、第1の基準電流源を用いて出力された第1の検出結果(ADCOUT1)と、第2の基準電流源を用いて出力された第2の検出結果(ADCOUT1)とから、第2のフォトダイオード(12)による可視波長域の受光強度を検出することによって照度を測定する。

(もっと読む)

固体撮像装置およびその駆動方法

【課題】画素電源用配線の寄生容量の影響を受けることなく、高速に画素信号を読み出すことができる固体撮像装置を提供する。

【解決手段】受光量に応じた信号を出力する画素セル2が2次元状に配列されて構成された撮像部1と、画素セル2を行単位で選択する行選択回路3と、行選択回路3で選択された画素セル2から出力される信号を、画素セル2の列ごとに、垂直信号線19を介して読み出す列回路7とを備え、列回路7は、信号を読み出すときに、画素セル2の列ごとに、垂直信号線19を介して、行選択回路3で選択された画素セル2に電流を供給する画素電流源回路4を備え、行選択回路3は、一行分の画素セル2からの信号の読み出し期間において、第1の行の画素セル2を選択することと、第1の行の画素セル2および第2の行の画素セル2を同時に選択することとを切り替える。

(もっと読む)

固体撮像装置及びその駆動方法

【課題】簡単な回路構成で参照ランプ電圧に対してオフセット電圧を付加することができる固体撮像装置を提供することを課題とする。

【解決手段】固体撮像装置は、複数の画素の各列に共通に接続される出力線(13)と、ランプ状に変化する参照ランプ電圧を生成する参照ランプ生成回路(17)と、参照ランプ電圧と出力線のアナログ電圧とを比較する比較器(15)と、比較器の比較開始後に比較器の出力信号が反転するまでの時間をデジタル値としてカウントするカウンタ部(18,19)とを有し、参照ランプ生成回路は参照ランプ電圧をオフセット電圧に設定し、その後、比較器の入力端子がリセットされ、その後、参照ランプ生成回路は、参照ランプ電圧をオフセット電圧からランプ開始電圧にリセットし、その後、参照ランプ生成回路はランプ開始電圧からランプ状の参照ランプ電圧を生成し、比較器は比較を開始する。

(もっと読む)

撮像素子、負荷電流源回路

【課題】画像の画質を向上させる。

【解決手段】複数の画素回路には、光信号の変換により生成される画素信号を読み出すための信号線が列単位で接続される。負荷電流源回路は、画素回路から画素信号を読み出すための負荷電流の大きさを定めるための電圧をサンプルホールドする保持回路を備える。この保持回路は複数の信号線で共有されて、負荷電流源回路は、保持回路が共有される複数の信号線ごとにサンプルホールドされた電圧に応じた負荷電流を画素信号を読み出す画素回路に対して供給する。

(もっと読む)

信号受信部テスト回路、撮像装置、信号受信部テスト方法、撮像装置のテスト方法

【課題】 複数列設けられた信号線に電気的に接続された信号受信部をテストする時、信号線に信号受信部テスト回路を電気的に接続して行うことがある。信号受信部テスト回路から各列の信号線までのインピーダンスが異なる場合に、テスト信号が伝送される信号線の列毎に信号受信部に供給されるテスト信号の信号レベルが異なってしまうという問題があった。

【解決手段】 複数列設けられた信号受信部に信号線を介してテスト信号を供給するテスト信号供給部を有する信号受信部テスト回路であって、テスト信号供給部は電圧バッファもしくは電流バッファであって複数設けられており、テスト信号供給部の一つと電気的に接続される前記信号線とは異なる前記信号線に電気的に接続される別の前記テスト信号供給部を少なくとも一つ有することを特徴とする信号受信部テスト回路である。

(もっと読む)

半導体装置、物理情報取得装置、及び、信号読出し方法

【課題】一部の単位素子の情報のみを必要とする素子選択モード時には通常モード時よりも消費電力を低減する。

【解決手段】素子アレイ部における1行分の単位素子の内の一部の単位素子の情報のみを必要とする素子選択モード時には、必要とされない単位素子と対応する信号処理回路が通常動作モード時よりも低消費電力状態となるように当該信号処理回路の機能を制御する。好ましくは、素子選択モード時に必要でない単位素子と対応する読出し信号の転送を禁止する。例えば、電源を供給したままで低消費電力状態となるように当該機能を制御してもよいし、電流源との関係がある機能部では電流源の電流を低減する方式を採用してもよい。電源の供給自体を停止することで当該機能を制御してもよい。電源を供給したままで当該機能を制御するよりも、電源の供給自体を停止する方が、消費電力の削減効果が高い。

(もっと読む)

放射線画像撮影装置および放射線画像撮影システム

【課題】装置自体で放射線の照射開始を的確に検出可能で、かつ、撮影前の読み出し処理における電力消費を低減することが可能な放射線画像撮影装置を提供する。

【解決手段】放射線画像撮影装置1の制御手段22は、放射線画像撮影前に、走査駆動手段15から全ての走査線5にオフ電圧を印加して各スイッチ手段8をオフ状態とした状態で読み出し回路17に読み出し動作を行わせて、スイッチ手段8を介して放射線検出素子7からリークした電荷qをリークデータdleakに変換するリークデータdleakの読み出し処理と、各放射線検出素子7のリセット処理とを交互に繰り返し行わせ、読み出したリークデータdleakが閾値dleak_thを越えた時点で放射線の照射が開始されたことを検出するとともに、放射線画像撮影前のリークデータdleakの読み出し処理と交互に行う各放射線検出素子7のリセット処理を定期的に中止する。

(もっと読む)

光電変換装置

【課題】フォトトランジスタの電流増幅率の低下が、製造要因などによりばらついた場合でも良好な光電変換特性を得ることができる光電変換装置を提供することを課題とする。

【解決手段】光電変換により電流を生成する光電変換素子(2)と、前記光電変換素子により生成された電流をベースに入力し、前記入力された電流を増幅してエミッタより出力するフォトトランジスタ(1)と、前記フォトトランジスタより出力された電流を対数変換する対数変換部(3)と、前記フォトトランジスタのベースに電流を出力する電流発生部(5)と、前記光電変換素子の遮光状態で前記対数変換部により対数変換された信号に基づき、前記電流発生部の出力電流を制御する電流制御部(6)とを有することを特徴とする光電変換装置が提供される。

(もっと読む)

固体撮像装置

【課題】低電源電圧動作時でも、画質の悪化なく、リセット電圧を昇圧する。

【解決手段】実施形態の固体撮像装置では、出力信号線電圧制御部3は、ゲートにバイアス電圧BIASが印加され、ソースが出力信号線12に接続され、ドレインが出力信号線電圧制御部電源ノードAVDDに接続される出力信号線電圧制御トランジスタ24を備える。負荷回路2は、出力信号線12の一端とソース電源ノードVssとの間に直接接続される電流源23を備える。FDノードは、出力信号線電圧制御トランジスタ24と電流源23とによるソースフォロア回路を機能させた後に、アンプトランジスタ17と電流源23とによるソースフォロア回路を機能させることにより昇圧される。FDノードが昇圧されたときの出力信号線12の電圧は、リセット電圧となる。

(もっと読む)

1 - 20 / 168

[ Back to top ]