Fターム[5E339EE03]の内容

プリント配線の製造 (8,867) | 特定の目的を持つ操作、工程 (174) | 検査、検出、制御 (22)

Fターム[5E339EE03]に分類される特許

21 - 22 / 22

回路形成システム

【課題】 基板に回路パターンを精度よく形成することのできる回路形成システムを提供する。

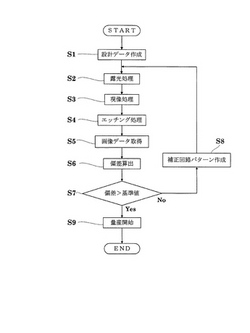

【解決手段】 ダイレクト露光装置が、予め作成した理論回路パターンの設計データに基づいて、基板上のレジストに直接に回路パターンを露光する(ステップS2)。その後、現像処理(ステップS3)およびエッチング処理(ステップS4)を施した後に、基板上に形成された実回路パターンの画像データを撮像装置で取得して所定のデータに変換し、回路パターンを所定の複数領域に分割する。この分割領域単位で、実回路パターンと理論回路パターンのパターン幅の偏差を求めて補正し、補正回路パターンを作成する(ステップS8)。

(もっと読む)

プリント配線板の製造方法および装置

【課題】 パターンの線幅を安定させてプリント配線板を製造できるようにする。

【解決手段】 ラミネート装置2が基板にレジスト層をラミネートするとともに、ラミネート日時を表す情報を基板に露光する。露光装置3が露光前にラミネート日時情報を読み取り、ラミネート後現在までの経過時間が所定のホールドタイム内にあるか否かを判断する。この判断が否定されると露光装置3は警報を行い、ラミネート後現在までの経過時間が所定のホールドタイム内にないことをオペレータに知らせる。オペレータはその基板については所望の線幅を得られないため、露光装置3から取り除くことができる。

(もっと読む)

21 - 22 / 22

[ Back to top ]