Fターム[5F003BP95]の内容

バイポーラトランジスタ (11,930) | 製法 (1,830) | エッチング (502) | 多工程のエッチング方法 (270) | リフトオフ (34)

Fターム[5F003BP95]に分類される特許

1 - 20 / 34

電子装置

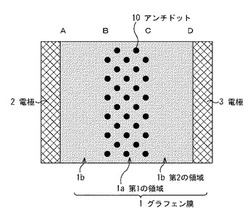

【課題】カーボンによるバンドギャップ・エンジニアリングを可能とし、カーボン原子に基づく多彩なエレクトロニクスを達成して、信頼性の高い電子装置を実現する。

【解決手段】電子装置は、単層のグラフェン膜1と、グラフェン膜1上の両端に設けられた一対の電極2,3とを有しており、グラフェン膜1では、電極2,3間の領域において、中央部位のBC間が複数のアンチドット10が形成されてなる第1の領域1aとされており、第1の領域1aの両側におけるAB間及びCD間がアンチドットの形成されていない第2の領域1bとされている。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】GaAsSb系の化合物半導体のベース層を有するInP系HBTにおいて、高周波特性を犠牲にすることなく、さらにオフ耐圧を向上させる。

【解決手段】InPからなる基板101の上に形成された第1コレクタ層102と、この上に形成された第2コレクタ層103と、この上に形成されてGa,As,およびSbから構成された化合物半導体からなるベース層104と、この上に形成されてInおよびPから構成された化合物半導体からなるエミッタ層105とを少なくとも備える。第2コレクタ層103は、第1コレクタ層102およびベース層104に接した状態で、ベース層104の伝導帯端のエネルギー準位よりも低く、第1コレクタ層102の伝導帯端よりも高い伝導帯端のエネルギー準位を有し、ベース層104の価電子帯端のエネルギー準位よりも低い価電子帯端のエネルギー準位を有したものとなっている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】セルフアライメントにより容易に電極を形成することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】エッチングストッパ層2の上方に、Sbを含み、所定の溶液に対するエッチング耐性がエッチングストッパ層2よりも低いSb含有層3bを形成し、Sb含有化合物半導体層3b上に、Asを含み、前記所定の溶液に対するエッチング耐性がエッチングストッパ層2よりも低いAs含有層3cを形成する。そして、前記所定の溶液を用いて、導電膜4をエッチングマスクとし、Sb含有層3b及びAs含有層3cをメサ状にウェットエッチングし、平面視でSb含有層3b及びAs含有層3cから離間した位置において化合物半導体層1の上方に導電膜5aを形成する。

(もっと読む)

ヘテロ接合バイポーラトランジスタの製造方法、及びヘテロ接合バイポーラトランジスタを用いた電力増幅器

【課題】InGaPをエミッタ層として有し、熱的安定性と通電に対する信頼性を両立することの出来るHBTを用いた電力増幅器を提供する。

【解決手段】InGaPエミッタ層を有するHBTにおいて、InGaPエミッタ層5とAlGaAsバラスト抵抗層7の間にGaAs層6を挿入し、ベース層4から逆注入された正孔がAlGaAsバラスト抵抗層7まで拡散、到達することを抑制する。

(もっと読む)

ヘテロ接合バイポーラトランジスタおよびその製法

【課題】高い電流増幅率を有し、高周波特性および素子寿命に優れたヘテロ接合バイポーラトランジスタおよびその製法を提供すること。

【解決手段】半絶縁性基板1上に、n型半導体より成る真性エミッタ層16と、p型ドーパントを高濃度でドーピングされ、真性エミッタ層16よりも狭いバンドギャップを有する半導体より成るベース層9と、ベース層9と同じ半導体より成るコレクタ層10とを、この順序で積層して成るへテロ接合バイポーラトランジスタにおいて、真性エミッタ層16の周囲に、高抵抗領域15が設けられ、高抵抗領域15と真性エミッタ層16との間に、真性エミッタ層16の半導体と同じ半導体から成るガードリング領域17が設けられ、真性エミッタ層16とベース層9との接合面が、ガードリング領域17の上面よりも下に位置することを特徴とするヘテロ接合バイポーラトランジスタを構成する。

(もっと読む)

半導体基板、半導体基板の製造方法、および電子デバイス

【課題】同一基板に形成されるHBTとFETとの相互影響を低減する。

【解決手段】第1半導体と、第1半導体の上方に形成された第2半導体とを備え、第2半導体は、P型の伝導型を示す不純物またはN型の伝導型を示す第1不純物原子と、第2半導体が第1不純物原子を有する場合のフェルミ準位を、第2半導体が第1不純物原子を有しない場合のフェルミ準位に近づける第2不純物原子とを有する半導体基板を提供する。一例として、当該第2半導体の多数キャリアは電子であり、第2不純物原子は、第1不純物原子を有する第2半導体のフェルミ準位を下降させる。第2半導体は3−5族化合物半導体であり、第2不純物原子が、ベリリウム、ボロン、炭素、マグネシウム、および亜鉛からなる群から選択された少なくとも1つであってもよい。

(もっと読む)

半導体積層体を含む半導体装置の製造方法

【課題】 半導体下層と半導体上層が積層された半導体積層体において、半導体下層の表面に損傷を与えることなく、半導体下層の一部を露出させる技術を提供する

【解決手段】 半導体下層18の表面の一部に、半導体上層15とは格子定数の異なる格子不整合層30を形成する工程と、格子不整合層30の表面と格子不整合層30で被覆されていない半導体下層18の表面に、半導体上層15を結晶成長させる工程と、格子不整合層30上の半導体上層15に形成された転位40を介してウェットエッチング液を導入し、格子不整合層30とその格子不整合層30上の半導体上層15を除去して半導体下層18の一部を露出させる工程を備える。ドライエッチングにより半導体下層18に損傷を与えることなく、半導体下層18の一部を露出させることができる。

(もっと読む)

半導体装置の製造方法、半導体装置および電子機器

【課題】InP基板に擬似格子整合もしくは格子整合させたデバイス層を形成し、そのデバイス層よりInP基板を剥離して、InP基板の再利用を可能とする。

【解決手段】インジウムリン(InP)基板11上に擬似格子整合もしくは格子整合する犠牲層12を形成する工程と、前記犠牲層12上にデバイス層13を形成する工程と、前記犠牲層12を除去することで前記InP基板11と前記デバイス層13とを分離する工程とを備えたことを特徴とする。

(もっと読む)

ヘテロ接合バイポーラトランジスタおよびその製造方法

【課題】良好なコンタクト特性を有するベース電極を再現性良く実現できるヘテロ接合バイポーラトランジスタとその製造方法を提供することにある。

【解決手段】

本発明のヘテロ接合バイポーラトランジスタは、半絶縁性InP基板1上に、N−型InGaAs/InAlGaAs/InPコレクタ層3、P+型InGaAsベース層4およびN型InPエミッタ層5が順次積層されている。更に、N型InPエミッタ層5はInPレッジ層構造7を備え、ベース電極10は、内部ベース電極12と外部ベース電極13から構成されており、内部ベース電極12は、コレクタメサ領域の外周部を自己整合的に規定しつつ、InPレッジ層構造7と接触し、外部ベース電極13の一部が、内部ベース電極12上に形成され、かつ、外部ベース電極13の残りの部分が、コレクタメサ領域外に形成された埋め込み層14上に形成されている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】信頼性に優れた半導体装置の製造方法および半導体装置を提供すること。

【解決手段】半絶縁性InP基板1上にInGaAsバッファー層2、InPサブコレクタ層3、InGaAsコレクタコンタクト層4、InP層5、InGaAsコレクタ層6、InGaAsベース層7、薄膜InP層8を順次積層し、薄膜InP層8上にシリコン窒化膜9を堆積し、それの開口部内においてInPエミッタ層10、InP層11、InGaAsエミッタコンタクト層12を順次エピタキシャル再成長させ、エミッタコンタクト層12表面全体を含むようにエミッタ電極メタル13を形成し、シリコン窒化膜9を開口部周辺の一部を残して除去し、露出した薄膜InP層8を除去し、ベース層7を露出させる工程を有するヘテロ接合バイポーラトランジスタの製造方法を構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板101の裏面から半導体基板101の表面にある金属配線108bまで至るよう形成されたビアホール116を有する半導体基板101と半導体基板101の表面にありビアホール116によって半導体基板101の表面に開口部を有する位置にある金属配線108bとの密着性を向上させた半導体装置100の構造およびその製造方法を提供する。

【解決手段】半導体基板上に形成された金属層と、前記金属層の下に前記半導体基板と前記金属層が合金化反応して形成された合金化反応層と、前記半導体基板の裏面側から前記金属層または前記合金化反応層に至るよう形成されたビアホールとを備えることを特徴とする。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】ベースコレクタ耐圧と電流増幅率を確保し、ベース抵抗を低減したヘテロ接合バイポーラトランジスタを提供する。

【解決手段】基板表面上に、エミッタコンタクト領域、第1の半導体材料からなるエミッタ領域、前記第1の半導体材料よりも禁制帯幅の小さな第2の半導体からなるベース領域、前記第1の半導体材料からなるコレクタ領域、コレクタコンタクト領域が前記基板表面に平行な方向に順次形成され、前記エミッタ領域、前記ベース領域、前記コレクタ領域と、前記基板表面との間に、前記第1の半導体材料よりも禁制幅の大きな第3の半導体材料からなるバッファ層を有するとともに、エミッタ電極、ベース電極、及びコレクタ電極がそれぞれ前記エミッタコンタクト領域、前記ベース領域、及び前記コレクタ領域に接して形成されたヘテロ接合バイポーラトランジスタである。

(もっと読む)

ヘテロ接合バイポーラトランジスタ及びその製造方法

【課題】HBTの動作の信頼性向上と動作の高速性向上とを同時に実現する。

【解決手段】 半絶縁性基板11上にコレクタコンタクト層12、コレクタ層13、ベース層14、エミッタ層15,16、エミッタコンタクト層17、エミッタ電極18,19が形成され、ベース層上、コレクタコンタクト層上にベース電極21、コレクタ電極25を取付けたHBTにおいて、エミッタ層を、ベース層側の第1のエミッタ層15とエミッタコンタクト層側の第2のエミッタ層16とで形成し、第1のエミッタ層の延設部23に空乏化されたリッジを形成する。さらに、第2のエミッタ層、エミッタコンタクト層及びエミッタ電極は、エミッタ電極に対するアンダーカット31を有したエミッタメサ22を形成し、ベース電極をエミッタメサに対してセルフアライン形成する。

(もっと読む)

バイポーラトランジスタ及び電力増幅器

【課題】 HBTセル内での発熱均一性を保ち、かつ、高周波帯域の利得特性を向上させたバイポーラトランジスタを提供する。

【解決手段】 ベースメサフィンガー(エミッタレッジ層15、ベース層16及びコレクタ層17)を2本のコレクタフィンガー(コレクタ電極13)で挟み、ベースメサフィンガー上に1本のベースフィンガー(ベース電極12)及びその両側の2本のエミッタフィンガー(エミッタ層14及びエミッタ電極11)を形成した構造である。2本のエミッタフィンガーは、ベースフィンガーを基準に対称の位置に形成される。

(もっと読む)

バイポーラトランジスタ及び電力増幅器

【課題】 HBTセル内での発熱均一性を保ち、かつ、高周波帯域の利得特性を向上させたバイポーラトランジスタを提供する。

【解決手段】 ベースメサフィンガー(エミッタレッジ層15、ベース層16及びコレクタ層17)を2本のコレクタフィンガー(コレクタ電極13)で挟み、ベースメサフィンガー上に1本のベースフィンガー(ベース電極12)及びその両側の2本のエミッタフィンガー(エミッタ層14及びエミッタ電極11)を形成した構造である。2本のエミッタフィンガーは、ベースフィンガーを基準に対称の位置に形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】 ベース/コレクタ接合容量およびベース層の引き出し抵抗を減少させることのできる電極構造を有する半導体素子を含む半導体装置及びその製造方法を提供すること。

【解決手段】 半絶縁性基板1の上にエピタキシャル成長法によって、サブコレクタ層2、コレクタ層3、ベース層4、エミッタ層5、エミッタキャップ層6の構成材料層を形成し、これらをメサ構造に加工してヘテロ接合バイポーラトランジスタ(HBT)素子20を形成する。HBT素子20では、ベース電極8をセンターに配置し、この幅方向両側にエミッタメサおよびエミッタ電極9を各2本形成する。ベース電極8の上には厚さが厚く、低抵抗なベース引き出し配線18を直接形成する。この際、ベース層4およびコレクタ層3の一部をその積層方向に同一パターンに除去し、この除去領域21を含む領域上にベース電極8およびベース引き出し配線18を形成する。

(もっと読む)

ヘテロ接合型半導体装置及びその製造方法

【課題】 ベース・コレクタ間容量及びベースコンタクト抵抗を共に減少させて、高周波特性等の特性の向上を図ることができる、ヘテロ接合型半導体装置及びその製造方法を提供すること。

【解決手段】少なくともコレクタ層3とベース層4とエミッタ層5とからなる積層体を有するヘテロ接合型バイポーラトランジスタ24aであって、エミッタキャップ層6、エミッタ層5及びコレクタ層3がアンダーカット形状をなし、各アンダーカット部に有機絶縁膜9A、9Bが充填されていると共に、エミッタ電極7に対して自己整合的に形成されたベース層4の側面から上面の一部にかけてベース電極12が全方向蒸着後のリフトオフによって形成されている、ヘテロ接合型バイポーラトランジスタ24a。

(もっと読む)

ヘテロ接合半導体装置及びその製造方法

【課題】 熱伝導性が改善された、メタモルフィックバッファ層を有するヘテロ接合半導体装置及びその製造方法を提供すること。

【解決手段】 半絶縁性基板1の上にエピタキシャル成長法によって、メタモルフィックバッファ層2を形成し、その上にコレクタ層3、ベース層4、エミッタ層5、およびエミッタキャップ層6を順次積層し、コレクタ電極7をメタモルフィックバッファ層2の上部層2cに接して設ける。メタモルフィックバッファ層2には、結晶成長中における不純物ドープ法によって、従来のサブコレクタ層と同等またはそれ以上の不純物を導入し、メタモルフィックバッファ層2がコレクタ電流をコレクタ電極7へ導く役割を果たすことができるようにする。熱抵抗の大きい三元混晶などで形成されることの多いサブコレクタ層を省略できるので、半導体装置内で発生した熱を速やかに基板1へ放熱することができる。

(もっと読む)

窒化ガリウム系半導体素子及びその製造方法

【課題】マグネシウムの活性化率が改善された窒化ガリウム系半導体素子およびその製造方法を提供する。

【解決手段】MOCVDにより窒素よも水素が多いキャリアガス雰囲気でマグネシウムがドープされた第一窒化ガリウム系半導体膜を成長し、その後3族原料ガスの供給を一旦停止し、水素よりも窒素が多いキャリアガス雰囲気でマグネシウムがドープされた第二窒化ガリウム系半導体を成長することにより、前記第一窒化ガリウム系半導体膜においては、マグネシウム濃度分布及び水素原子濃度分布は実質的に平坦であり、かつマグネシウム濃度が水素原子濃度より高く、前記第二窒化ガリウム系半導体膜においては、表面に向かってマグネシウム濃度及び水素原子濃度が増大する第1の領域が設けられ、前記第1の領域におけるマグネシウム濃度は水素原子濃度より高いと共に、前記第一窒化ガリウム系半導体膜におけるマグネシウム濃度よりも高い構造とする。

(もっと読む)

ヘテロ接合バイポーラトランジスタ及びその製造方法

【課題】 エミッタサイズを縮小でき、且つ製造コストを低減することができるHBTを実現する。

【解決手段】 高濃度n型の第1サブコレクタ層102上に、バンドギャップの小さい材料からなる高濃度n型の第2サブコレクタ層108と、i型又は低濃度n型のコレクタ層103と、高濃度p型のベース層104と、バンドギャップの大きい材料からなるn型のエミッタ層105と、高濃度n型のエミッタキャップ層106と、バンドギャップの小さい材料からなる高濃度n型のエミッタコンタクト層107とが順次形成されている。エミッタコンタクト層107からは、エミッタ電極を兼ねる配線115Aが引き出され、エミッタ層105からは、ベース電極を兼ねる配線115Bが引き出され、第2サブコレクタ層108からは、コレクタ電極を兼ねる配線115Cが引き出されている。

(もっと読む)

1 - 20 / 34

[ Back to top ]