Fターム[5F005BA03]の内容

Fターム[5F005BA03]に分類される特許

1 - 7 / 7

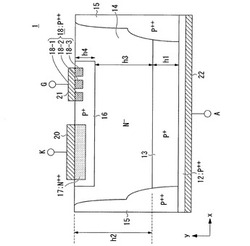

サイリスタ

【課題】ゲート電極の接触抵抗の値を制御できるサイリスタを提供することを目的としている。

【解決手段】第1導電型半導体基板14の一方の表面近傍に第1の第2導電型半導体領域16が形成され、第1の第2導電型半導体領域の表面近傍にカソード電極20と接合する第1導電型半導体領域17およびゲート電極21と接合する第2の第2導電型半導体領域18が形成され、第1導電型半導体基板の他方の表面近傍にアノード電極22と接合する第3の第2導電型半導体基板13が形成されたサイリスタにおいて、ゲート電極と第2の第2導電型半導体領域とが接合してオーミック接触を形成し、ゲート電極と第1の第2導電型半導体領域とが接合して非オーミック接触を形成する。

(もっと読む)

逆阻止型サイリスタ

【課題】本発明は、高い周波数のスイッチング動作に対応でき、且つ、電力損失を低減できる逆阻止型サイリスタを提供することを目的とする。

【解決手段】P領域(1a、1b)とN領域(2a、2b)とP領域3とN領域4とが順に接合された逆阻止型サイリスタ100は、P領域(1a、1b)からN領域4に順方向電圧が印加された場合にP領域(1a、1b)とN領域4の間を導通させる前の最大電圧値を示すブレークオーバ電圧が、N領域4からP領域(1a、1b)に逆方向電圧が印加された場合にN領域4とP領域(1a、1b)の間の導通を阻止する限界の電圧値を示すブレークダウン電圧より低くなるように電圧差を生じさせる電圧差生成領域30を有する。

(もっと読む)

ESD保護回路及び半導体装置

【課題】信号電圧が電源電圧を正負両方向に越えるようなチップ端子に対し適切に動作するESD保護回路を提供する。

【解決手段】ESD保護回路は、端子に一端のP側が接続されグラウンドに他端のN側が接続されるPNPN接合と、グラウンドにP側が接続されるPN接合のN側にソース及びゲートが接続され、前記の端子にドレインが接続されるPMOSトランジスタとを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】3次元的に形成したトランジスタやサイリスタのリーク電流を低減する半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板10の主面に対してほぼ垂直に形成されたシリコンピラー12と、シリコンピラー12の下部及び上部にそれぞれ設けられた第1及び第2の不純物拡散層14,16と、シリコンピラー12を水平方向に貫いて設けられたゲート電極18と、ゲート電極18とシリコンピラー12との間に設けられたゲート絶縁膜20と、シリコンピラー12に隣接して設けられたバックゲート電極48と、バックゲート電極48とシリコンピラー12との間に設けられたバックゲート絶縁膜46とを備える。

(もっと読む)

半導体装置

【課題】消費電力が小さく、かつ臨界電圧上昇率を向上させたサイリスタを得る。

【解決手段】このトライアック10を制御する電極は、主電極となるT1電極(第1の主電極)11、T2電極(第2の主電極)12と、ゲート電極13である。トライアック10を構成する半導体層20は、図に示すように、P1層(第1の半導体層:p型層:ベース)21、N1層(n型層:ベース)22、P2層(p型層:ベース)23、N2層(第3の半導体層:n型層:エミッタ)24、N3層(n型層:エミッタ)25、N4層(第2の半導体層:n型層)26で構成される。このトライアック10においては、シリコンのダイオード31、32が、ゲート電極13からT1電極11に向かう方向が順方向となるべく、T1電極11とゲート電極13との間に直列に設置される。

(もっと読む)

双方向サイリスタ

【課題】双方向サイリスタの感度の向上と誤動作の防止との両方を良好に達成することが困難であった。

【解決手段】双方向サイリスタを構成するために、半導体基板1に第1、第2、第3及び第4のN型半導体領域N1、N2、N3、N4と第1及び第2のP形半導体領域P1、P2とを設ける。半導体基板1の一方の表面2に第1の主電極T1とゲ−ト電極Gとを配置する。半導体基板1の他方の主面3に第2の主電極T2を設ける。第4のN形半導体領域N4に浅く拡散された第1の部分N4aと深く拡散された第2の部分N4bとを設ける。第2の部分N4bを第1及び第2の主サイリスタの中心から遠い位置に配置する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】スイッチング速度、とくにオン状態からオフ状態への高速でのスイッチングが可能なサイリスタ構成の半導体装置、さらにはこのような半導体装置の駆動方法および製造方法を提供する。

【解決手段】p型領域p1、n型領域n1、p型領域p2、およびn型領域n2がこの順に接して設けられた半導体層101と、両端部に配置されたp型領域p1に接続されたアノード電極Aと、n型領域n1に接続されたカソード電極K電極と、中央に配置されたp型領域p2に接続されたゲート電極G1,G2とを備えた半導体装置1において、ゲート電極は、p型領域p2を構成する半導体層101部分を挟んで対向配置されている。

(もっと読む)

1 - 7 / 7

[ Back to top ]