Fターム[5F033UU00]の内容

半導体集積回路装置の内部配線 (234,551) | レイアウト、シミュレーション (1,514)

Fターム[5F033UU00]の下位に属するFターム

配線の設計、レイアウト (1,445)

シミュレーション (64)

Fターム[5F033UU00]に分類される特許

1 - 5 / 5

光電変換装置およびその製造方法

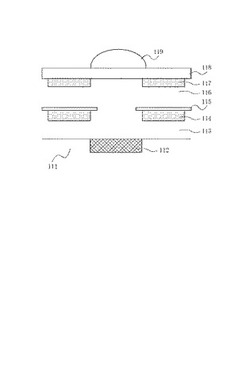

【課題】 配線材料の層間絶縁膜への拡散を抑制する拡散抑制膜による多層配線構造を設けた光電変換装置において、工程を増加させることなく、受光効率を高める。

【解決手段】 本発明は、半導体基板に配された光電変換素子と、前記半導体基板上に層間絶縁膜を介して複数の配線層が配された多層配線構造を有する光電変換装置であって、最上配線層の上部に、前記最上配線層を構成する材料の拡散を抑制する拡散抑制膜が配され、前記拡散抑制膜は、前記最上配線層及び前記層間絶縁膜の前記光電変換素子に対応する領域を覆って配されており、前記拡散抑制膜の前記光電変換素子に対応する領域にレンズが配されていることを特徴とする。

(もっと読む)

ヘテロ接合バイポーラ・トランジスタ及びその製造方法

【課題】 ヘテロ接合バイポーラ・トランジスタ及びその製造方法を提供する。

【解決手段】 ヘテロ接合バイポーラ・トランジスタに関連する、半導体構造体及び半導体の製造方法が提供される。この方法は、同じ配線レベルにある金属導線によって接続される2つのデバイスを形成することを含む。2つのデバイスの第1のものの金属導線は、銅配線構造体上に金属キャップ層を選択的に形成することによって形成される。

(もっと読む)

設計データ作成方法、設計データ作成プログラム、及び半導体装置の製造方法

【課題】作成された設計データを用いて製造される半導体装置の歩留まりを向上させる設計データ作成方法、設計データ作成プログラム、及び半導体装置の製造方法を提供すること。

【解決手段】本発明の一形態の設計データ作成方法は、半導体装置の設計データを作成する設計データ作成方法であって、パターンレイアウトに含まれるコンタクトホール層パターンを挟む上層配線パターンと下層配線パターンとのAND領域を抽出し(S31)、前記AND領域に含まれるコンタクトホール層パターンを抽出し(S32)、前記AND領域の中心と前記コンタクトホール層パターンの中心とが一致するように前記コンタクトホール層パターンを移動する(S33)。

(もっと読む)

半導体装置およびその製造方法

【課題】製造工程時間の増加を招くことなく、複数の凹部に埋め込まれた部材表面の平坦性を向上することのできる技術を提供する。

【解決手段】相対的に面積の大きい第1ダミーパターンDP1と相対的に面積の小さい第2ダミーパターンDP2とをダミー領域FAに配置することによって、素子形成領域DAとダミー領域FAとの境界BL近くまでダミーパターンを配置することができる。これにより、分離溝内に埋め込まれた酸化シリコン膜の表面の平坦性をダミー領域FAの全域において向上することができる。さらに、ダミー領域FAのうち相対的に広い領域を上記第1ダミーパターンDP1で占めることで、マスクのデータ量の増加を抑えることができる。

(もっと読む)

半導体装置の設計方法および信頼性評価方法

【課題】 所望の信頼性を有する半導体装置を設計する。

【解決手段】 半導体装置100は、第一の配線112上にビア124が形成された構成を有する。半導体装置100の設計方法は、銅配線(配線金属膜110)中において、ボイド150が一の起点から成長すると仮定したときの、所定温度でSIV保証時間topenに広がるボイド150の成長領域の想定値xopenを算出するステップと、想定値xopenと第一の配線112とビア124との接触領域のサイズとを比較することにより、ビア124の形状因子を規定するステップと、を含む。接触領域のサイズは、d+2h(dはビア124の直径、hはビア124が第一の配線112内に埋め込まれる深さ)とすることができる。

(もっと読む)

1 - 5 / 5

[ Back to top ]