Fターム[5F038AR24]の内容

Fターム[5F038AR24]に分類される特許

1 - 11 / 11

半導体装置

【課題】半導体装置の信頼性を確保する。

【解決手段】基板と、基板に埋め込まれ、複数の開口部を有する絶縁膜と、複数の開口部内に位置する基板に設けられた複数のダミー拡散層20と、抵抗素子形成領域40において、平面視でダミー拡散層20と重ならないように絶縁膜上に設けられ、かつ第1方向に延伸する複数の抵抗素子10と、抵抗素子形成領域40において、絶縁膜上およびダミー拡散層20上に設けられ、かつ第1方向に延伸する複数のダミー抵抗素子12と、を備え、ダミー抵抗素子12は、平面視で、第1方向と基板に水平な面内において垂直な第2方向に並ぶ少なくとも二つのダミー拡散層20と重なっている。

(もっと読む)

半導体装置及びその製造方法

【課題】素子分離酸化膜上に所望の形状の抵抗素子を形成して、抵抗値の精度を高めて信頼性を向上させる。

【解決手段】半導体基板1の表面に形成された所定領域の素子分離酸化膜2上に複数の抵抗素子4が形成された半導体装置であって、抵抗素子4と近接する位置に活性領域3を設けた。抵抗素子4近傍の素子分離酸化膜2を必要な範囲に区切ることができ、CMP法による素子分離酸化膜2の研磨の際に素子分離酸化膜2の中央部に凹みが形成されてしまうことを抑止できるため、抵抗素子4の形状の寸法精度を向上させることが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】チップサイズの縮小化と抵抗値のばらつきの低減化とが両立された抵抗体を有する半導体装置及びその製造方法を提供する。

【解決手段】アナログ回路を構成する半導体装置21であって、シリコン基板1と、シリコン基板1上に形成されたシリコンを主成分とする線状の抵抗体3と、抵抗体3の両端部のうちいずれかの端部に接して形成された金属シリサイドからなる複数のコンタクト形成領域7と、抵抗体3及び複数のコンタクト形成領域7の上に形成された層間絶縁膜4と、層間絶縁膜4を貫通し、複数のコンタクト形成領域7のそれぞれと層間絶縁膜4上に形成された金属配線6とを電気接続する複数のコンタクトプラグ5とを有し、複数のコンタクト形成領域7のそれぞれの面内パターンは、抵抗体3から、少なくとも2箇所で面内屈曲していることにより、コンタクト形成領域7の一部が抵抗体3に並行して形成されている。

(もっと読む)

半導体装置

【課題】本発明は、配線抵抗成分をセンス抵抗として利用しながら、過電流保護回路の検出精度を向上することが可能な半導体装置を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、監視対象となる電流ラインの配線抵抗成分であるセンス抵抗Rsと、センス抵抗Rsでの降下電圧と所定の閾値電圧を比較して過電流保護信号Socpを生成する過電流保護回路OCPと、前記電流ラインの形成工程と同一の工程により、他の回路要素から電気的に分離して形成されたダミーラインの配線抵抗成分であって、センス抵抗Rsよりも大きな抵抗値を有するダミー抵抗Rdと;ダミー抵抗Rdの両端に各々接続されたダミーパッドT1、T2と;を集積化して成り、過電流保護回路OCPは、前記閾値電圧を調整するための閾値電圧調整部を有する構成とされている。

(もっと読む)

半導体装置及びその製造方法

【課題】 抵抗値が所望の設計値に対して1%以下で、かつ寄生容量が小さく、比較的大きな電流を流すことができる、抵抗値調整可能な抵抗素子を容易に得る。

【解決手段】 半導体基板に抵抗素子1、3が内蔵された半導体装置において、前記抵抗素子1、3はその抵抗値を一定範囲で調整可能な構造を有し、前記第1の抵抗素子と一対の第2の抵抗素子2が500マイクロメートル以内に隣接して配置されていて、かつ前記第2の抵抗素子の両端子には各々2つのパッド端子が引き出されている。

(もっと読む)

トリミング回路及び半導体装置

【課題】ツェナーダイオードを用いることなく基準抵抗との合成抵抗値の増減が可能なトリミング回路及び半導体装置を提供することを目的としている。

【解決手段】本発明のトリミング回路410は、抵抗とフューズにより構成されるトリミング回路411とトリミング回路412とを備える。そして、トリミング回路411を基準抵抗Rsと直列に接続し、トリミング回路412を基準抵抗Rsと並列に接続することにより、ツェナーダイオードを用いずに端子P1−接地間の合成抵抗値の増減を可能とした。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 段差及び高温工程の影響を抑制し、抵抗素子の抵抗ばらつきを低減することができる半導体装置を提供する。

【解決手段】 絶縁膜21上に設けられた第1の抵抗体13、第1の抵抗体13の上面及び側面、並びに絶縁膜21の上面にある抵抗体間絶縁膜23、及び、側面が、抵抗体間絶縁膜23を介して第1の抵抗体13の側面に対向し、上面が、第1の抵抗体13の上面に形成された抵抗体間絶縁膜23の上面と同一面をなす第2の抵抗体15とを有し、第1の抵抗体13と第2の抵抗体15とが配線材35で直列に接続されている。

(もっと読む)

終端抵抗を備えたインターフェース回路並びにそれを内蔵した集積回路装置及び電子機器

【課題】 絶対値精度が求められる終端抵抗の抵抗値を調整可能とすること。

【解決手段】 インターフェース回路に設けられる終端抵抗132は、互いに並列接続された第1〜第Nの抵抗素子140−1〜140−Nと、各々が第1〜第Nの抵抗素子のうちのn(1≦n<N)個の各々とそれぞれ直列接続された第1〜第nの切断素子142−1〜12−nとを含む。第1〜第nの切断素子142−1〜142−nの何れかを切断して、絶対値精度が求められる終端抵抗132の抵抗値を調整する。

(もっと読む)

半導体装置

【課題】デザインルールが縮小しても高抵抗で抵抗精度の高い抵抗素子と不揮発性半導体記憶素子とを合理的に実現する半導体装置を提供する。

【解決手段】半導体基板に設けられた第1の半導体領域に形成された不揮発性半導体記憶素子と、前記半導体基板に設けられた第2の半導体領域と、前記第2の半導体領域上に形成され前記第1の絶縁膜より厚い第3の絶縁膜と、前記第3の絶縁膜上に前記第1の電極と同一の材料で形成された導電体層と、前記第2の半導体領域、第3の絶縁膜及び導電体層を自己整合的に分離する第2の素子分離と、前記導電体層の上面に形成された第4の絶縁膜と、前記導電体層の両端の前記第4の絶縁膜上に形成され、前記第2の電極の少なくとも一部と同一の材料を含み、前記導電体層に接続された第3及び第4の電極とを具備する抵抗素子とを具備することを特徴とする。

(もっと読む)

半導体装置

【課題】半導体装置の組立製造時に発生する当該半導体装置に対する内部および外部応力による半導体装置の電気特性劣化箇所およびモードを検出することができ、さらに半導体装置製造直後の電気特性劣化を検出する。

【解決手段】電極パッド1の最上層の直下に、SiN材で構成された層間絶縁膜3を介して抵抗配線4,6を設け、この抵抗配線4,6を断面方向に対して数層に渡って設ける。各抵抗配線4,6は、その幅および長さを電極パッド1内の一定範囲ごとに変化させ、かつ配線抵抗値の差を各配線にもたせておく。これにより回路構成の端子に電流および電圧を印加すると、電極パッド1直下の特定の範囲において、配線の断線、あるいは異なる抵抗値を有する配線間におけるショート、あるいは電極パッドと配線間にリークが発生した場合に、回路全体の抵抗値変動が発生する。これを検出することにより、半導体装置の電気特性劣化箇所などを検出することができる。

(もっと読む)

半導体装置

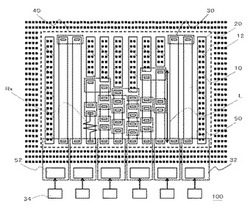

【課題】 半導体基板上のパターン密度の疎密によるトランジスタ特性のばらつきを抑制する。

【解決手段】 半導体基板1上の正規のPoly−R12等の回路素子に加えて、回路素子のパターン密度が均一になるように、半導体チップ内のほぼ全面にわたって、ダミーの機能素子となるPoly−R12aのパターンを配置する。さらに、このダミー用のPoly−R12aを、アルミ被りによる抵抗値の変動を抑制するためにLP−SiN膜17に覆われた構造とし、アルミ配線による抵抗値の変動を抑えるとともに、パターン密度の疎密による抵抗値、トランジスタ特性の変動を低減する。これにより、パターン密度の疎密によるトランジスタ特性のばらつきをなくし、さらに、アルミ被りによるPoly−Rへの影響や、赤外線吸収の素子疎密によるウェーハ内温度差を抑制する。

(もっと読む)

1 - 11 / 11

[ Back to top ]