Fターム[5F046EB09]の内容

半導体の露光(電子、イオン線露光を除く) (57,085) | 位置合わせマークの配置 (959) | 配線上、電極上、ボンディングパッド上 (7)

Fターム[5F046EB09]に分類される特許

1 - 7 / 7

半導体装置の製造方法

【課題】精度よく検出可能なアライメントマークを簡便に形成する。

【解決手段】半導体基板の素子形成領域に素子分離絶縁膜を形成するとともに周辺領域に下地絶縁膜を形成し、ゲート材料膜を形成し、このゲート材料膜をエッチングしてゲートパターンを形成するとともに前記下地絶縁膜上のゲート材料膜を除去してアライメントマーク形成用領域を形成し、層間絶縁膜を形成し、この層間絶縁膜をエッチングしてコンタクトホールを形成するとともにアライメントマーク形成用領域にマークホールを形成し、コンタクトホールが充填されマークホールが充填されないように第1導電膜を形成し、コンタクトホール及びマークホールの外部の第1導電膜を除去してコンタクトプラグを形成し、このマークホールが充填されないように第2導電膜を形成し、このマークホール内に残した凹部による段差を利用してリソグラフィのアライメントを行う。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】製造効率を高めることができる半導体装置の製造方法等を提供する。

【解決手段】半導体装置1の製造方法は、絶縁層12のダイシング領域に溝部120を形成し、内部回路形成領域にビアホール126を形成する工程、絶縁層12上に第一のレジスト膜13を設ける工程、第一のレジスト膜13を覆う第二のレジスト膜14を設ける工程、第二のレジスト膜14の内部回路形成領域を覆う領域に配線用開口141を形成し第二のレジスト膜14のダイシング領域を覆う領域に位置合わせ用開口142を形成する工程、溝部120と位置合わせ用開口142との位置関係を検出し第二のレジスト膜14の配線用開口141が絶縁層12のビアホール126に対し所定の位置にあるかどうか検出する工程を含む。第二のレジスト膜14を選択的に除去する工程では、位置合わせ用開口142の領域が絶縁層12中の溝部120を覆うように位置合わせ用開口142を形成する。

(もっと読む)

調整可能なアライメントジオメトリ

【課題】 従来技法の欠点を解決すべく非対称なターゲットの測定やモデル化、ターゲットジオメトリ(幾何学構造)の特殊な設計および/または微妙な調整を可能にするアライメントシステムを提供すること。

【解決手段】 1つまたは複数のサブターゲットをアライメントターゲット上に形成することによってアライメントターゲットにジオメトリデザインを持たせ、アライメントシステムにより1つまたは複数のサブターゲットの全てに関してアライメントを実施し、プロセスのキャラクタライズとアライメントシステムのアライメントの計算のためのアルゴリズムを使用する。

(もっと読む)

基準パターン抽出方法、位置決め方法及び装置、並びに露光装置

【課題】埃等の不着の無い部分から基準パターンの抽出を行えるようにする。

【解決手段】実質的に同一の加工が施された複数の所定領域を有する物体上の該所定領域内に任意に設定される該所定領域よりも小さい面積を有する被計測領域内でユニークな信号特徴を有する基準パターンを抽出する基準パターン抽出方法である。前記複数の所定領域のうち任意に選択される第1所定領域内で、前記被計測領域の信号情報を計測する工程(S12)と、この工程で計測された信号情報に基づいて、前記被計測領域内でユニークな信号特徴を有する候補パターンを抽出する工程(S17)と、前記複数の所定領域のうちの前記第1所定領域とは異なる第2所定領域内で、前記被計測領域を計測する工程S22と、この工程で計測された信号情報に基づいて、前記候補パターンに対応する比較パターンを抽出する工程S23と、前記比較パターンに基づいて、前記候補パターンの前記基準パターンとしての適性を判断する工程S25とを備えている。

(もっと読む)

配線基板

【課題】 半導体装置の組み立てや実装工程において、アライメントマークを使って配線基板の設置状態の位置、方向を測定する際に、ビアランドに接続する配線の状態に係わらず、ビアランドをアライメントマークと誤って認識すること(誤認識)を防止し、位置あわせ不良を解消することを目的とする。

【解決手段】 ビアランド2に誤認識防止用の配線8を付加することにより、半導体装置の組み立てや実装工程において、アライメントマーク3を使って配線基板の設置状態の位置、方向を測定する際に、ビアランド2に接続する配線の状態に係わらず、ビアランド2をアライメントマーク3と誤って認識すること(誤認識)を防止し、位置あわせ不良を解消することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】写真製版工程等における精度の良好な重ね合わせを実現するアライメントマークを備えた半導体装置及びその製造方法を得ること。

【解決手段】基板上に第1層と第2層を形成する工程と、素子形成領域及びアライメントマーク形成領域に第1トレンチを形成する工程と、第1トレンチのうちアライメントマーク形成領域の第1トレンチをさらにエッチングして第2トレンチを形成するとともにアライメントマーク形成領域の第2層の厚みを薄くする工程と、第1トレンチ及び第2トレンチを埋め込むように第2層上に絶縁膜を堆積する工程と、アライメントマーク形成領域の第2層上に絶縁膜を残留させた状態に絶縁膜を平坦化する工程と、アライメントマーク形成領域の第2層上に残留した絶縁膜をエッチングマスクとして素子形成領域の第2層をエッチング除去する工程と、アライメントマーク形成領域の絶縁膜をエッチング除去する絶縁膜除去と、を含む。

(もっと読む)

半導体装置

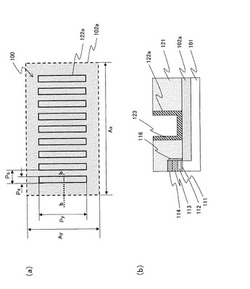

【課題】 ダイ領域の層間絶縁膜の平坦性を確保すると共に、スクライブ領域を多機能化或いは小型化する。

【解決手段】 多層配線構造を有する半導体装置であって、ダイ領域11及びスクライブ領域12を有する基板上に形成された層間絶縁膜と、ダイ領域11の層間絶縁膜内に形成された多層の金属配線層(配線パターン)13と、金属配線層13と同じ層に形成され、かつ、ダイ領域11の層間絶縁膜内に形成されたダミーパターン15とを備え、ダミーパターン15内にリソグラフィ・マークパターンとしての合わせマーク16が形成されている。

(もっと読む)

1 - 7 / 7

[ Back to top ]