Fターム[5F048BD01]の内容

MOSIC、バイポーラ・MOSIC (97,815) | チャネル (4,415) | 形状 (1,258)

Fターム[5F048BD01]の下位に属するFターム

チャネル長(幅) (272)

Fターム[5F048BD01]に分類される特許

981 - 986 / 986

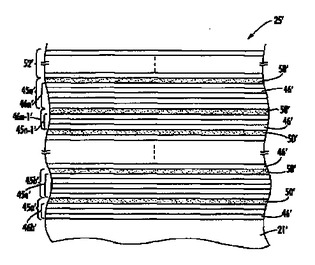

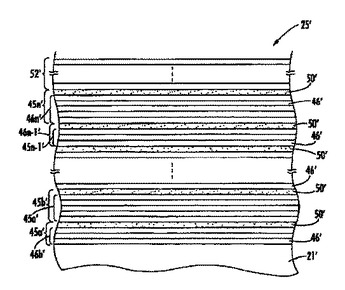

バンド設計超格子を有するMOSFETを有する半導体装置

半導体装置は、基板と、該基板に隣接する少なくとも一つのMOSFETとを有する。MOSFETは、超格子チャンネルを有し、該超格子チャンネルは、複数の積層された層群を有する。またMOSFETは、超格子チャンネルと水平方向に隣接するソースおよびドレイン領域と、超格子上に設置されたゲートと、を有し、超格子チャンネルを通って、積層された層群と平行な方向に電荷キャリアの輸送が生じる。超格子チャンネルの各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。エネルギーバンド調整層は、基本半導体部分に隣接する結晶格子内に取り込まれた、少なくとも一つの非半導体分子層を有し、超格子チャンネルは、平行な方向において、エネルギーバンド調整層がない場合に比べて大きな電荷キャリア移動度を有する。

(もっと読む)

(もっと読む)

バンド設計超格子を有する半導体装置を製作する方法

複数の積層された層群を有する超格子を形成するステップによって、半導体装置を製作する方法である。また当該方法は、前記超格子を通って、前記積層された層群と平行な方向に、電荷キャリアの輸送が生じる領域を形成するステップを有する。超格子の各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。前記エネルギーバンド調整層は、基本半導体部分に隣接する結晶格子内に取りこまれた、少なくとも一つの非半導体分子層を有し、前記超格子は、超格子が存在しない場合に比べて、前記平行な方向において大きな電荷キャリア移動度を有する。また前記超格子は、共通のエネルギーバンド構造を有しても良い。

(もっと読む)

(もっと読む)

バンド設計超格子を有する半導体装置

半導体装置は、複数の積層された層群を有する超格子を有する。超格子の各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。さらにエネルギーバンド調整層は、少なくとも一つの非半導体分子層を有し、この層は、連接する基本半導体部分の結晶格子内に閉じ込められる。従って超格子は、平行な方向において、エネルギーバンド調整層がない場合に比べて大きな電荷キャリア移動度を有する。  (もっと読む)

(もっと読む)

三次元集積回路構造及びこれを作る方法

垂直方向の半導体装置は、電気装置そして/または相互接続を含む分離して作られた基板に付加される。多くの垂直方向の半導体装置は物理的に互いに分離され、そして同一半導体本体又は半導体基板内には配置されない。多くの垂直方向の半導体装置は取り付けられた後に個別のドープされたスタック構造を生成するため、エッチングされた数個のドーピングされた半導体領域を含む薄い層として分離して作られた基板へ付加される。あるいは多くの垂直方向の半導体装置が分離して作られた基板に取り付けるのに先立ち製作される。ドープされたスタック構造は、ダイオードキャパシタ、n‐MOSFET、p‐MOSFET、バイポーラトランジスタ、及び浮遊ゲートトランジスタのベースを形成する。強誘電体メモリー装置、強磁性体メモリー装置、カルコゲニド位相変更装置が分離して作られた基板と連結して使用するために、堆積可能なアッド‐オン層に形成される。堆積可能なアッド‐オン層は相互接続ラインを含む。

(もっと読む)

(もっと読む)

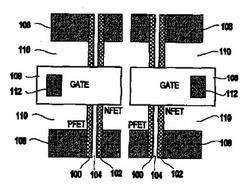

並列相補型FinFETの対を有する集積回路構造体及び該形成方法

【課題】 従来の単一のFinFETのスペースに2またはそれ以上のFinFETを形成すること。

【解決手段】 相補的フィン型電界効果トランジスタ(FinFET)を用いる集積回路構造体のための方法および構造体を開示する。本発明は、第1フィン(100)を含む第1型FinFETと、第1フィン(100)に並列に延在する第2フィン(102)を含む第2型FinFETを含む。また、本発明は、第1型FinFETおよび第2型FinFETのソース/ドレイン領域(130)の間に配置される絶縁体フィンを含む。第1型FinFETと第2型FinFETとの間隔が1個のフィンの幅とほぼ等しくなるように、絶縁体フィンは、第1フィン(100)および第2フィン(102)とほぼ同じ寸法の幅にされる。また、本発明は、第1型FinFETおよび第2型FinFETのチャネル領域を覆うように形成された共通ゲート(106)を含む。ゲート(106)は、第1型FinFETに隣接する第1不純物ドーピング領域と、第2型FinFETに隣接する第2不純物ドーピング領域とを含む。第1不純物ドーピング領域と第2不純物ドーピング領域の差異が、ゲートに、第1型FinFETと第2型FinFETとの差異に関係した異なる仕事関数を与える。第1フィン(100)および第2フィン(102)はほぼ同じ幅である。

(もっと読む)

半導体集積回路

【課題】CMOS回路の集積度を高め、かつMOSトランジスタのゲート幅の変動を抑えることが可能な半導体集積回路を提供する。

【解決手段】PMOS及びNMOSトランジスタ1個から成るインバータを構成するレイアウトとして、素子領域の中央付近にNMOSトランジスタ領域8が配置され、その上下に2分割された状態でPMOSトランジスタ領域1a及び1bが配置され、それぞれのトランジスタ領域1a及び1bと領域8にゲート電極3が延在するように配置されている。NMOSトランジスタ領域8の位置にマスク合わせずれが生じたとしても、各トランジスタのゲート幅に変化がなく、特性を低下させずに集積度を向上させることができる。

(もっと読む)

981 - 986 / 986

[ Back to top ]