Fターム[5F048DA18]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 製造方法 (5,886) | イオン注入時ゲート保護層(最外レジストを除く) (203) | SiO2 (73)

Fターム[5F048DA18]に分類される特許

1 - 20 / 73

半導体装置

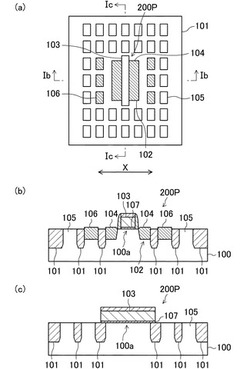

【課題】Si混晶層における選択成長用マスクの開口率の違いによりエピタキシャル成長が不均一となることを防止すると共に、半導体素子のキャリア移動度を向上できるようにする。

【解決手段】半導体装置は、半導体基板100の上部に形成された素子分離膜101と、素子分離膜に囲まれてなる素子活性領域102と、該素子活性領域102に形成され正孔をキャリアとするチャンネル領域100aとを有するP型MIS−FET200Pと、素子分離膜における素子活性領域102の周辺部に形成された複数のダミー活性領域105とを備えている。複数のダミー活性領域105のうち、正孔の移動方向と対向する位置に形成されたダミー活性領域のみをシリコンとゲルマニウムとを含むSiGe付きダミー活性領域106としている。

(もっと読む)

半導体集積回路装置の製造方法

【課題】低抵抗で、かつ接合リーク電流の少ないCoシリサイド層を形成することのできるサリサイドプロセスを提供する。

【解決手段】Co純度が99.99%以上で、FeおよびNiの含有量が10ppm以下、より好ましくはCo純度が99.999%の高純度Coターゲットを用いたスパッタリング法によってウエハの主面上に堆積したCo膜をシリサイド化することにより、MOSFETのゲート電極(8n、8p)、ソース、ドレイン(p+型半導体領域13、n+型半導体領域14)の表面に低抵抗で接合リーク電流の少ないCoSi2層(16b)を形成する。

(もっと読む)

半導体装置の製造方法

【課題】NMOSトランジスタに対する半導体基板のエッチングによる影響を考慮して、寄生抵抗の増大を防止することで電流駆動能力の低下を防止し、半導体集積回路の動作速度の低下を防止した半導体装置の製造方法を提供する。

【解決手段】ゲート電極41を注入マスクとしてシリコン基板1内にヒ素あるいはリンをイオン注入して、シリコン基板1の表面内に1対のエクステンション層51を形成し、その後、シリコン基板1の全面に、CVD法によりシリコン酸化膜で厚さ1〜20nmの保護絶縁膜14を形成する。そして、ゲート電極42を注入マスクとして保護絶縁膜14の上部からシリコン基板1内にボロンあるいはBF2をイオン注入して、シリコン基板1の表面内に1対のエクステンション層52を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】歪み発生層に緩和が生じにくい半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11の上に形成されたゲート電極15と、ゲート電極15の両側面上に形成され、断面L字状の内側サイドウォール17Bと、半導体基板11におけるゲート電極15の両側方の領域に埋め込まれた歪み発生層19とを備えている。内側サイドウォール17Bは、5×1019/cm3以上の炭素を含む炭素含有シリコン酸化膜からなる。歪み発生層19は、1%以上の炭素を含む炭素含有シリコンエピタキシャル層を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置を高集積化および高性能化することのできる技術を提供する。

【解決手段】SOI−MISFETは、SOI層3と、SOI層3上にゲート絶縁膜15を介して設けられたゲート電極35aと、ゲート電極35aの両側壁側のSOI層3上に、SOI層3からの高さがゲート電極35aよりも高く設けられ、ソース・ドレインを構成する積上げ層24とを有している。また、バルク−MISFETは、シリコン基板1上にゲート絶縁膜15より厚いゲート絶縁膜16を介して設けられたゲート電極35bと、ゲート電極35bの両側壁側の半導体基板1上に設けられたソース・ドレインを構成する積上げ層25とを有している。ここで、積上げ層24の厚さが、積上げ層25の厚さよりも厚く、ゲート電極35a、35bの全体、SOI−MISFETのソース・ドレインの一部、およびバルク−MISFETのソース・ドレインの一部がシリサイド化されている。

(もっと読む)

半導体装置及びその製造方法

【課題】n型MISトランジスタ及びp型MISトランジスタの双方において、所望のシリサイド組成比を有する金属シリサイド膜からなるフルシリサイド化ゲート電極を精度良く実現する。

【解決手段】半導体装置は、第1の活性領域10a上に形成された第1のゲート絶縁膜13a、第1のゲート絶縁膜13a上に形成された第1のフルシリサイド化ゲート電極24a、及び第1のサイドウォール17aとを有するn型MISトランジスタと、第2の活性領域10b上に形成された第2のゲート絶縁膜13b、第2のゲート絶縁膜13b上に形成された第2のフルシリサイド化ゲート電極24b、及び第2のサイドウォール17bとを有するp型MISトランジスタとを備える。第1のフルシリサイド化ゲート電極24aの上面高さは、第2のフルシリサイド化ゲート電極24bの上面高さよりも低い。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化が進みゲート長のバリエーションが増大した場合にも、高駆動力MISFETを搭載した高性能デバイスを安定して実現できる簡便なFUSI化技術を提供する。

【解決手段】第1のゲート長(相対的に短いゲート長)を持つ第1のゲート電極105Aがフルシリサイド化されているのに対して、第2のゲート長(相対的に長いゲート長)を持つ第2のゲート電極105Bはフルシリサイド化されていない。

(もっと読む)

半導体装置およびその製造方法

【課題】金属とシリコンおよび/またはゲルマニウムを必須として含む金属半導体化合物をゲート電極とする金属絶縁膜半導体電界効果トランジスタを利用した半導体装置において、ゲート絶縁膜やチャネル等によらずに複数の閾値電圧を設定する。

【解決手段】半導体装置が、MAxで表される組成を有する第1のゲート電極を含む第1のトランジスタと、MAyで表される組成を有する第2のゲート電極を含む第2のトランジスタを少なくとも含むMIS電界効果トランジスタを含む(式中、MはW、Mo、Ni、Pt、Ta、Pd、Co、およびTiからなる群より選択される少なくとも1種の金属元素であり、Aはシリコンおよび/またはゲルマニウムであり、0<x≦3、および0<y≦3であり、xとyは異なる)。

(もっと読む)

静電放電保護装置、半導体装置及び静電放電保護装置の製造方法

【課題】バラスト抵抗の抵抗値の変動を抑制することのできる静電放電保護装置、半導体装置及び静電放電保護装置の製造方法を提供することにある。

【解決手段】基板40上にゲート酸化膜41を介してゲート電極42を形成した。このゲート電極42を挟んで基板40中のソース形成領域S及びドレイン形成領域Dに、n−型拡散領域44S,44Dをそれぞれ形成し、そのn−型拡散領域44S,44Dの下にn+型拡散領域45S,45Dをそれぞれ形成した。n−型拡散領域44Dの表面に、ゲート電極42のサイドウォール43からシリサイドブロック領域52分だけ離間してドレイン電極51を形成した。このドレイン電極51の真下領域であってn+型拡散領域45Dの下端と深さ方向において重なるかたちでp+型拡散領域55を形成した。

(もっと読む)

半導体装置の製造方法

【課題】第1および第2のトランジスタ形成領域の各々にゲートを有するトランジスタを備えた半導体装置の製造方法であって、半導体基板の表面がエッチングされて不均一な凹部が生じることを防ぐことができる半導体装置の製造方法を提供する。

【解決手段】半導体基板SB上に絶縁膜ILが堆積される。第2のトランジスタ形成領域R2において金属膜MGが形成される。シリコン膜SGおよびハードマスク膜HMが堆積される。ゲートの平面パターンを有するハードマスク膜HMとシリコン膜SGとの積層膜パターンMPが形成される。第1のトランジスタ形成領域R1が被覆されるように第1のレジスト膜PRiが形成される。第2のトランジスタ形成領域R2において金属膜MGが積層膜パターンMPのハードマスク膜HMをマスクとしてパターニングされる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】リソグラフィ工程を追加することなく、様々な線幅およびレイアウトで配置された電極を、均一な組成でフルシリサイド化させることが可能な製造方法を提供する。

【解決手段】シリコン基板1上にポリシリコンからなるゲート電極5をパターン形成する。シリコン基板1上を絶縁膜11で覆った状態で、絶縁膜11から露出させたゲート電極5を覆ように第1金属材料を主成分とする第1金属膜31を成膜する。熱処理によってゲート電極5の表面層のみを第1金属膜と反応させる第1回目のシリサイド化を行い上層シリサイド膜33を形成する。次いで第1金属膜を除去する。上層シリサイド膜33を覆う状態で、第1金属材料よりも拡散速度の速い第2金属材料を主成分とする第2金属膜35を成膜する。上層シリサイド膜33で表面が覆われたゲート電極5の全層を熱処理によって第2金属膜と反応させる第2回目のシリサイド化を行い、ゲート電極5をフルシリサイド化させる。

(もっと読む)

MOSトランジスタ、そのMOSトランジスタの製造方法、そのMOSトランジスタを利用したCMOS型半導体装置、及び、そのCMOS型半導体装置を利用した半導体装置

【課題】

本発明の目的は、上記のストレッサーが発生する応力がより効率的にMOSトランジスタのチャネル部に印加されるように、ストレッサーを配置したMOSトランジスタ、そのMOSトランジスタの製造方法、及び、そのMOSトランジスタを利用したCMOS型半導体装置を提供することにある。

【解決手段】

本発明は、シリコン基板と、シリコン基板上のゲート絶縁膜と、ゲート絶縁膜上のゲート電極と、ゲート電極の両側に形成されたソース・ドレイン領域と、シリコン基板表面から離間し、前記ソース・ドレイン領域に挟まれた領域であって、ゲート電極下部のシリコン基板内部に形成され、応力発生物質が埋め込まれた、応力発生物質埋込領域と、を備えるMOSトランジスタ、そのMOSトランジスタの製造方法、及び、そのMOSトランジスタを利用したCMOS型半導体装置を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート長に依存することなく均一な組成のFUSI構造を持つゲート電極を有するMISFETを得られるようにする。

【解決手段】第1のゲート電極114の両端部は、その他の部分よりも低く形成されており、当該両端部の側面及び上面を覆うように第1のサイドウォールスペーサ105Aが形成されている。第1のゲート電極114よりもゲート長が大きい第2のゲート電極115の両端部も、その他の部分よりも低く形成されており、当該両端部の側面及び上面を覆うように第2のサイドウォールスペーサ105Bが形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】同一基板上において誘電率の異なる複数種類のゲート絶縁膜を必要性に応じて使い分けた半導体装置の構造、及び当該構造を実現する簡便な製造方法を提供する。

【解決手段】基板1の活性領域1a上に高誘電率ゲート絶縁膜4を介してゲート電極7Aが形成されている。基板1の活性領域1b上にゲート酸化膜6を介してゲート電極7Bが形成されている。ゲート電極7A及び7Bのそれぞれの側面に同一構造の絶縁性サイドウォールスペーサ8A及び8Bが形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】仕事関数の値及び閾値が安定したフルシリサイドゲート電極を有する半導体装置を実現できるようにする。

【解決手段】本発明に係る半導体装置は、半導体基板の上に形成されたゲート絶縁膜15aと、ゲート絶縁膜の上に形成されたゲート電極23とを備えている。ゲート電極23は、層状の複数の結晶粒が積層されてなる金属シリサイド膜を有するフルシリサイドゲート電極である。

(もっと読む)

電子デバイス及びその製造方法

【課題】金属シリサイドゲート電極を有する電子デバイスにおいてリーク電流の増加を抑制する。

【解決手段】シリコン基板1上にゲート絶縁膜4を介して金属シリサイドからなるゲート電極105及び106が形成されている。金属シリサイドの形成時における金属の拡散を防止する導電性拡散防止層15がゲート電極105及び106の下側にゲート絶縁膜4と接するように形成されている。

(もっと読む)

半導体及びその製造方法

【課題】 既存のシリコン・プロセスを用いて容易に形成可能な方法によって、pMOSFETの駆動電流を増大させた半導体装置及びその製造方法を提供する。

【解決手段】 (100)シリコン基板11上の<100>方向にチャネルを有するpMOSFETを作製し、STI16によりチャネルと垂直方向から圧縮応力を印加する。

(もっと読む)

半導体装置

【課題】25V耐圧MISFET、6V耐圧MISFETおよび1.5V耐圧MISFETを備えたLCDドライバを縮小化する。

【解決手段】n型ウエル5dに形成された6V耐圧の中耐圧pMIS(Q2p)と、p型ウエル8に形成された6V耐圧の中耐圧nMIS(Q2n)とから中耐圧CMISが構成されている。中耐圧pMIS(Q2p)、中耐圧nMIS(Q2n)および中耐圧CMISの周囲には、それぞれガードバンド(G1p)、ガードバンド(G1n)およびガードバンド(G2)が設けられている。このガードバンド(G2)は、その一部がガードバンド(G1p)の一部と重複している。

(もっと読む)

半導体装置

【課題】製造工程時間の増加を招くことなく、複数の凹部に埋め込まれた部材表面の平坦性を向上することのできる技術を提供する。

【解決手段】相対的に面積の大きい第1ダミーパターンDP1と相対的に面積の小さい第2ダミーパターンDP2とをダミー領域FAに配置することによって、素子形成領域DAとダミー領域FAとの境界BL近くまでダミーパターンを配置することができる。これにより、分離溝内に埋め込まれた酸化シリコン膜の表面の平坦性をダミー領域FAの全域において向上することができる。さらに、ダミー領域FAのうち相対的に広い領域を上記第1ダミーパターンDP1で占めることで、マスクのデータ量の増加を抑えることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の製造歩留まりを向上することのできる技術を提供する。

【解決手段】ゲート電極4aの側壁にサイドウォール6aが形成され、ゲート電極4bの側壁にサイドウォール6bが形成されている。これらゲート電極4a、4bを覆うように基板1の主面上に酸化膜を堆積する。次いで、基板1の表面が露出するまで異方性エッチングを用いた後、等方性エッチングを用いて、ゲート電極4b上の一部に前記酸化膜からなるキャップ膜8cを形成すると共に、ゲート電極4aの側壁に前記酸化膜からなるサイドウォール8aおよびゲート電極4bの側壁に前記酸化膜からなるサイドウォール8bを形成する。

(もっと読む)

1 - 20 / 73

[ Back to top ]