Fターム[5F049MB04]の内容

受光素子−フォトダイオード・Tr (21,418) | 素子本体材料 (2,026) | 材料 (1,897) | IV族 (950) | 微結晶 (45)

Fターム[5F049MB04]に分類される特許

1 - 20 / 45

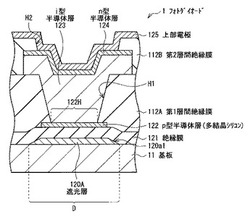

光電変換素子および光電変換装置

【課題】ノイズ光の影響を軽減することが可能な光電変換素子および光電変換装置を提供する。

【解決手段】フォトダイオードは、基板上に、第1導電型(例えばp型)半導体層、i型半導体層および第2導電型(例えばn型)半導体層をこの順に備え、基板と第1導電型半導体層との間に遮光層を有している。第2導電型半導体層側から入射する光に基づいて信号電荷が取り出される(光電変換がなされる)。基板と第1導電型半導体層との間に遮光層が設けられていることにより、第2導電型半導体層側から入射した光のうち、吸収されずに第1導電型半導体層を透過して基板側へ出射した光が遮断されると共に、基板側から第1導電型半導体層へ向かう光が遮断される。

(もっと読む)

光電変換装置

【課題】電気的若しくは物理的な作用によりストレスが加えられても動作特性が劣化することが少ない、薄膜を積層して形成する光電変換装置を提供する。

【解決手段】第1の電極202と第2の電極207の間に光電変換層を備えた光電変換装置であって、第1の電極202は、光電変換層と一部で接触する構造を有し、その接触部における第1の電極202の断面形状をテーパー形状とする。この場合において、一導電型の第1の半導体層203の一部が、第1の電極202と接触する構造を有している。また、第1の電極202の端部の平面形状は、角が無く、面取りをした形状若しくは曲面形状とすることが好ましい。

(もっと読む)

半導体装置

【課題】光電変換層に汚染物質を混入させず、分光感度特性がよく、かつ出力電流にばら

つきのない光電変換装置を得ることを課題とする。光電変換装置を有する半導体装置にお

いて、信頼性の高い半導体装置を得ることを課題とする。

【解決手段】絶縁表面上に、第1の電極と第2の電極と、前記第1の電極と第2の電極と

の間にカラーフィルタと、前記カラーフィルタを覆ってオーバーコート層と、前記オーバ

ーコート層上に、p型半導体膜、i型半導体膜及びn型半導体膜を有する光電変換層と、

前記光電変換層の端部の一方は、前記第1の電極と接しており、前記カラーフィルタの端

部は、前記光電変換層の端部の他方より内側にある半導体装置に関する。

(もっと読む)

センサアレイ基板、これを含む表示装置およびこれの製造方法

【課題】センサアレイ基板、これを含む表示装置およびこれの製造方法を提供する。

【解決手段】本発明の一実施形態によるセンサアレイ基板は、基板と、前記基板上のゲート配線およびデータ配線が交差して定義される複数の画素領域および前記複数の画素領域上に形成される複数の第1センサ部および複数の第2センサ部を含み、前記複数の第1センサ部は赤外線波長帯の光を感知し、前記複数の第2センサ部は可視光線波長帯の光を感知し、前記データ配線方向に隣接して配置された2個の第1センサ部は第1ユニットを形成し、前記データ配線方向に隣接して配置された2個の第2センサ部は第2ユニットを形成し、前記第1ユニットと前記第2ユニットが前記データ配線方向およびゲート配線方向に交互に配置される。

(もっと読む)

光電変換素子およびその製造方法

【課題】クラックに起因する暗電流の増加を抑制することが可能な光電変換素子を提供する。

【解決手段】光電変換素子10は、基板11上の選択的な領域に設けられたp型半導体層14と、n型半導体層17との間にi型半導体層16を備えたものである。i型半導体層16は、p型半導体層14に非接触な角部16eを少なくとも1つ有する。i型半導体層16において、例えばその形状等に起因する応力(ストレス)の影響を受けてクラックが発生した場合、i型半導体層16が上記のような角部16eを有していることにより、クラックは、その角部16eを起点(または終点)として発生し易くなる。この角部16eが、p型半導体層14に非接触であることにより、発生したクラックがリークパスとなることが抑制される。

(もっと読む)

フォトセンサ装置

【課題】アモルファスシリコン、あるいは微結晶シリコンで作製したフォトダイオードを使用し、構造が簡単で、かつ低電圧で駆動可能なフォトセンサ装置を提供する。

【解決手段】複数のフォトダイオードがアレイ状に配置されたフォトダイオードアレイと、前記フォトダイオードアレイの各行のフォトダイオードの第1電極に接続される複数の走査線と、前記フォトダイオードアレイの各列のフォトダイオードの第2電極に接続される複数の読出線と、前記複数の走査線に接続され、1水平走査期間毎に、前記各走査線に順次選択走査信号を供給する走査回路と、前記複数の読出線に接続され、信号読み出し時に、1水平走査期間の前記各読出線の電圧変動を信号電圧として取り込む信号処理回路とを備え、前記各フォトダイオードは、アモルファスシリコンあるいは微結晶シリコンで作製されており、信号読み出し時に、前記各フォトダイオードに対して、順方向のバイアス電圧が印加される。

(もっと読む)

膜厚の決定方法、半導体装置の作製方法、半導体装置

【課題】光電変換層のキャリア生成効率を上昇させることを目的とする。

【解決手段】光電変換層を複数種類の半導体を積層した構造とすることによって、広い波長範囲に渡って光を吸収することができるので、キャリア生成効率を上昇させることができる。さらに、複数種類の半導体を積層した光電変換層は膜厚比を最適化することによってキャリア生成効率を向上させることができる。具体的には、吸収係数を求め、透過光の強度式に代入し、透過光の積分強度が最小となる膜厚比を決定し、その膜厚比を膜厚となるように上記複数種類の半導体を成膜すればよい。

(もっと読む)

光電変換装置の製造方法

【課題】高い均一性を備える銀薄膜を熱処理により凝集させて凸凹を形成する場合、温度や表面状態により、一箇所に凝集し、銀薄膜が無くなってしまう領域と、銀が「だま」状に集中してしまう場所ができてしまう場合がある。この場合、本来の目的である乱反射領域にはならず、不良品となる課題がある。

【解決手段】多結晶ITO層20aを積層し、フォトリソグラフ工程によりレジストマスクを形成した後、多結晶ITO層20aを例えば塩酸系のエッチング液を用いてエッチングする。ここで、レジストマスクに覆われた部分は配線層として機能する。この場合粒界から選択的にエッチングが進行し、特定の面方位のグレインが残り、エッチングマスクとして機能する残渣20bが形成される。この残渣20bをマスクとして第2層間絶縁層19をドライエッチングすることでテクスチャー構造を得ることができる。

(もっと読む)

多接合型光学素子

【課題】従来の多接合型太陽電池等において、太陽電池セルを積層するため半導体層の構造上の制約が多く十分な特性が得られないという問題があったので、積層構造の自由度を高め、光電変換効率を増大させることを目的とする。

【解決手段】複数の光吸収スペクトルの異なる太陽電池セルを積層した多接合型太陽電池において、太陽電池セルは、両面に開口する貫通孔を有する透明基板上に形成され、透明基板の貫通孔内部及び太陽電池セルの形成されていない側の面が、透明導電膜で被覆されていることを特徴とする。

(もっと読む)

光電変換素子、光電変換装置、及びイメージセンサ

【課題】例えば、感度が高められた光電変換素子、及び光電変換装置、並びにイメージセンサを提供する。

【解決手段】下電極(151e)は、基板(10)上に形成されたゲート絶縁膜(41)、絶縁膜(42)、(43)及び(44)のうちアクリル樹脂の有機樹脂から構成された絶縁膜(43)上に形成されている。下電極(151e)は、基板(10)上における断面形状が凹凸形状であり、且つ入射光に対して斜めに交差する光反射面を有している。したがって、下電極(151e)によれば、フォトセンサ(151)の上側からフォトセンサ(151)に入射した入射光のうちn型半導体層(151b)、受光層(151c)及びp型半導体層(151d)を透過した光を、入射光の入射方向とは別の方向に散乱させることが可能である。

(もっと読む)

光センサ

【課題】一つの部品で多方向からの光を検知することが可能な光センサを提供する。

【解決手段】透光性を有する基板101に複数の検出素子を有し、該検出素子は並列に接続され、ITO(酸化インジウム酸化スズ合金)、酸化インジウム酸化亜鉛合金(In2O3)―ZnO)、酸化亜鉛(ZnO)等の透光性を有する導電膜で形成された第1の透明電極102を有し、第1の透明電極102に接続される配線103、第1の半導体膜104、金属電極(極性:マイナス)105、及び金属電極105に接続される配線106によって第1の検出素子を構成し、第1の透明電極(極性:プラス)102、第1の透明電極102に接続される配線103、第2の半導体膜107、第2の透明電極(極性:マイナス)108、及び第2の透明電極108に接続される配線109によって第2の検出素子を構成する。

(もっと読む)

安定高感度光検出器のための材料、作製機器、および方法、それにより作製される画像センサ

感光デバイスは、それぞれが仕事関数を有する第1のコンタクトおよび第2のコンタクトと、第1のコンタクトと第2のコンタクトとの間の感光物質とを備えるデバイスを含む。感光物質はp型半導体またはn型半導体を含み、感光物質は仕事関数を有する。回路が第1のコンタクトと第2のコンタクトとの間にバイアス電圧を印加する。バイアスが第1のコンタクトと第2のコンタクトとの間に印加されたとき、感光物質は、第1のコンタクトから第2のコンタクトまでの電子走行時間より長い電子寿命を有する。第1のコンタクトは電子の注入を提供し、正孔の抽出を阻止する。第1のコンタクトと感光物質間の界面は、1cm/s未満の表面再結合速度を提供する。  (もっと読む)

(もっと読む)

光電変換装置、及び当該光電変換装置を具備する電子機器

【課題】強光を受光することで出力電流が低下した際に生じる実際の光強度とのばらつきを補正して出力することのできる光電変換装置を提供することを課題とする。

【解決手段】光電変換素子と、光電変換素子に照射される入射光量に応じた第1の電流を流すための回路を具備する光電流出力回路と、透過率a(0<a<1)の遮光膜で遮光された補正用光電変換素子を具備し、補正用光電変換素子に照射される入射光量に応じた光電流を1/a倍にした第2の電流を流すための回路を具備する光電流補正回路と、第2の光電流と第1の電流との差に応じた第3の電流を1/(1−a)倍にした第4の電流を流すための回路を具備する光電流加算回路と、第1の電流及び第4の電流の和に応じた電流を増幅して出力する回路を具備する増幅回路と、とを有する。

(もっと読む)

光電変換装置、光電変換装置の製造方法、及び電子機器

【課題】珪素系PIN−PDの暗電流を減らすため、PIN−PDのI層を挟むP層、またはN層に炭素を加えバンドギャップを大きくし、I層からの暗電流を抑える方法では、炭化珪素と珪素とでは25%程度格子定数が異なっており、珪素中に炭素を添加することで大きな応力が生じ、この応力により欠陥が発生し暗電流が増える。また、側面からのリークを下げるのみでは、暗電流を抑制は限定的なものとなる。

【解決手段】AlNdを用いたPIN−PD10の第1導電層20をエッチング液で処理しテクスチャー構造を作り、さらにこの工程で生成されたAlNd酸化物を下バリア層21として用いる。この際、第1半導体層22と第1導電層20との間はFN電流により電荷が伝達される。FN電流が少ない黒状態では下バリア層21の微分抵抗は高く、暗電流の通過を阻止する。白状態では微分抵抗は低くなり、光電流は通過するので、画像のSN比が上がる。

(もっと読む)

光電変換素子、光電変換装置、及びイメージセンサ

【課題】フォトセンサの赤外光検出性能を高めると共に、リーク電流を低減する。

【解決手段】受光層151cは、マイクロクリスタルシリコン(以下、“μ−CSi”と称す。)等の微結晶半導体から構成されている。このような受光層151cは、アモルファスシリコン等の非晶質半導体層を用いる場合に比べて、赤外光の受光感度を向上させることが可能である。第1半導体層151a及び受光層151c間に介在する第1中間層151bは、、第1半導体層(151a)及び受光層151cと接合層を構成している。第1中間層151bは、アモルファスシリコン等の非晶質半導体から構成されている。したがって、フォトセンサ151は、第1中間層151bの存在によって、受光層151cにμC−Si等の微結晶半導体を用いることによって生じるリーク電流の増大を抑制できる。

(もっと読む)

半導体装置、電気光学装置及び電子機器

【課題】光センサー素子の応答速度を早め、検出精度を向上させた半導体装置を実現する。

【解決手段】検出回路510に繋がる第1の導電領域としての第1のp型半導体領域532−1、第1の導電領域としての第2のp型半導体領域532−2の面積を電源配線521に接続される第2の導電領域としての第1のn型半導体領域533−1〜第3のn型半導体領域533−3の面積に比べて小さく構成する。具体的には第1の導電領域を構成するサブ領域の個数は第2の導電領域のサブ領域の個数より少ないように構成する。また、第1の導電領域をn型、第2の導電領域をp型半導体で構成して電位勾配の発生をおさえる。

(もっと読む)

光センサ内蔵表示装置

【課題】表示画面の輝度設定に影響を与えずに光センサの検出精度を向上できる光センサ内蔵表示装置を提供する。

【解決手段】この光センサ内蔵表示装置は、TFT(TFT:薄膜トランジスタ)アレイ基板40aの各画素部に、微結晶シリコンTFTで構成された画素駆動用TFT22と、微結晶シリコンTFTで構成された第1の光電変換用TFT20と、非晶質シリコンTFTで構成され、第1の光電変換用TFT20と並列接続された第2の光電変換用TFT21とを備える。

(もっと読む)

表示装置、および、その製造方法

【課題】フォトセンサ素子の感度を向上可能する。

【解決手段】n層47nとi層47iとp層47pとのそれぞれを液晶パネル200の面の法線方向zにおいて、順次、積層することで、フォトセンサ素子32を形成する。ここでは、ポリシリコンよりも光吸収係数が高い微結晶シリコンによって、i層47iを形成する。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】薄膜トランジスタを有する半導体装置を安価に大量生産することを可能にする、半導体装置の製造方法を提供する。

【解決手段】プラスチック基板11等の基板上にアモルファスシリコン層13を形成する工程と、アモルファスシリコン層13をパターニングして、薄膜トランジスタとなる所定のパターンを形成する工程と、その後、パターニングされたアモルファスシリコン層13を結晶化する工程とを有して、薄膜トランジスタを有する半導体装置を製造する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】外部ストレスによる亀裂、ヒビ、カケなど外観上の不良を低減された半導体装置を提供することを課題の一とする。また、薄型化された半導体装置の製造歩留まりを向上させることを課題の一とする。

【解決手段】基板と、基板の一方の面に設けられた半導体集積回路部と、基板の他方の面、側面、及び半導体集積回路部の側面を連続的に覆う樹脂層とを有する。複数の半導体集積回路部が形成された基板の半導体集積回路部形成面と、固定基板とをワックスにより固定し、半導体集積回路部ごとに基板を分断する。個々に分断された半導体集積回路部が形成された基板を覆うように樹脂層を形成する。

(もっと読む)

1 - 20 / 45

[ Back to top ]