Fターム[5F064FF01]の内容

ICの設計・製造(配線設計等) (42,086) | 切り換え、選択 (3,709) | 切り換え、選択目的 (1,053)

Fターム[5F064FF01]の下位に属するFターム

冗長系における切り換え (279)

特性、機能の切り換え (623)

試験、監視 (143)

Fターム[5F064FF01]に分類される特許

1 - 8 / 8

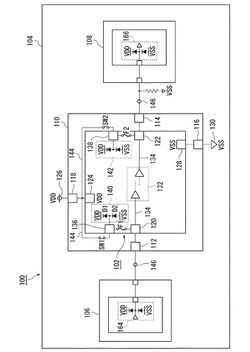

半導体集積回路および電子回路

【課題】簡易な工程で保護ダイオードが有する寄生容量を内部回路から分離し、半導体集積回路の高速化を実現することが可能な半導体集積回路および電子回路を提供することを目的とする。

【解決手段】信号端子120と内部回路132とを接続する信号ライン134と、信号ライン134から分岐して接続されるヒューズ素子F1と、ヒューズ素子F1を介して信号ライン134と接続し、正電源VDDまたは負電源VSSが直接接続される通電端子136と、ヒューズ素子F1の通電端子136側に接続され、信号ライン134と正電源VDDまたは負電源VSSとの間をそれぞれ逆方向に接続する保護ダイオードD1、D2と、を備えることを特徴とする。

(もっと読む)

半導体集積回路

【課題】チップ面積が増大することなく設計において大きな後戻りをしなくてすむ半導体集積回路を提供すること。

【解決手段】一列に配列された各IOバッファ1〜5と、各IOバッファ1〜5に対応して配列されたパッド接続用配線21〜25と、各IOバッファ1〜5に対応して一列に配列されるとともに、IOバッファ1〜5及びパッド接続用配線21〜25と異なる層にて対応するパッド接続用配線の一部と重なるように配置され、かつ、対応するパッド接続用配線の隣の他のパッド接続用配線まで延長して配線されたIOバッファ切替用配線31〜35と、を備え、各IOバッファ切替用配線31〜35は、隣の他のIOバッファ切替用配線と短絡しないように同じ形状に形成され、各IOバッファ1〜5は、同じ位置にて対応するIOバッファ切替用配線31〜35と電気的に接続される。

(もっと読む)

カレントミラー回路

【課題】 インプロセス中で生じるチャージの影響を低減させることで、精度の良いカレントミラー比が得られるカレントミラー回路の構成を提供する。

【解決手段】 カレントミラーを構成する隣合うMOSトランジスタのゲート同士を、直接多結晶シリコンを用いて接続し、基板に接続されたヒューズをゲート部に接続することで、インプロセス中でカレントミラー回路を構成する隣り合うMOSトランジスタのゲートが受けるチャージの影響を同量に緩和させることを特徴とする。

(もっと読む)

半導体集積回路

【課題】半導体集積回路において、マスクを作り直すことなく、必要に応じて静電気放電(ESD)の耐性を向上させること。

【解決手段】コア回路5内に保護用セル(PC_1〜PC_7)が形成される。ESD耐性の必要度に応じて、各保護用セルと、ESDトリガ検出回路10の出力端子TR_OUTとを接続するための配線LSが配線層に形成される。

(もっと読む)

半導体デバイス及び半導体デバイスの配線方法

【課題】配線遅延を削減して動作速度を向上させた半導体デバイスを提供する。

【解決手段】半導体デバイス1は、基板2に形成されたCLB3a及びCLB3iと、CLB3aとCLB3iとの間に形成されて組み替え可能なSWM4a〜4lと、SWM4a〜4lの速度ばらつきをそれぞれ測定する速度ばらつき測定回路5と、速度ばらつき測定回路5によってそれぞれ測定されたSWM4a〜4lの速度ばらつきに基づいて、CLB3aとCLB3iとの間の配線経路を決定する配線経路決定部6とを備える。

(もっと読む)

自動設計装置、自動設計方法及び自動設計プログラム

【課題】配線やビア等を含む基本図形に対し、製造上の要求から付加された付加図形と回路特性上の要求から付加された付加図形とを明確に区別でき、設計精度及び設計効率の向上が可能な自動設計装置、自動設計方法及び自動設計プログラムを提供する。

【解決手段】チップ領域上に配置された配線及びビアを含む複数の基本図形に付加する複数の付加図形を計算し、配線記憶部32に記憶させる計算部16と、複数の付加図形の計算結果を配線記憶部から読み出して、付加図形の区分及び特性により、複数の付加図形を、チップ領域上で基本図形を製造するために製造上必要な付加図形と回路特性上必要な付加図形とに少なくとも分類し、分類結果を分類記憶部34に記憶させる分類部14と、分類結果により、解析の目的に応じて複数の付加図形の少なくとも一部を抽出して、基本図形の特性を解析する解析部16とを備える。

(もっと読む)

半導体集積回路

【課題】環状配線から電力の供給を受けるマクロセルを有し、消費電力を低減することが可能な半導体集積回路を提供する。

【解決手段】この半導体集積回路は、所定の機能を実現するためのマクロセルMC1と、マクロセルMC1を囲むように配置され、マクロセルMC1に接続された環状配線L1と、環状配線L1を囲むように配置され、電源電位VDDに接続された環状配線L2と、環状配線L2を囲むように配置され、電源電位VSSに接続されるとともにマクロセルMC1に接続された環状配線L3と、制御信号に従って環状電源L1と環状電源L2との間又は環状配線L1と環状配線L3との間を接続するためのスイッチ回路としてのCMOSインバータINV1,INV2とを具備する。

(もっと読む)

半導体装置

【課題】 ヒューズ配線の搭載によるチップ面積の増大を抑制することが可能な半導体装置を提供する。

【解決手段】 半導体装置は、半導体基板上に少なくとも1つの絶縁層を介して配置された、レーザにより切断可能な少なくとも1つのヒューズ配線を有する。この半導体装置において、ヒューズ配線と半導体基板との間に、ヒューズ配線と少なくとも1つの絶縁層を介して対向するように配置された、レーザを吸収する第1のレーザ吸収層を設ける。

(もっと読む)

1 - 8 / 8

[ Back to top ]