Fターム[5F064FF02]の内容

ICの設計・製造(配線設計等) (42,086) | 切り換え、選択 (3,709) | 切り換え、選択目的 (1,053) | 冗長系における切り換え (279)

Fターム[5F064FF02]に分類される特許

1 - 20 / 279

半導体装置及びトリミング方法

【課題】ヒューズ素子の列数増に伴うトリミング時間の伸長を抑制する。

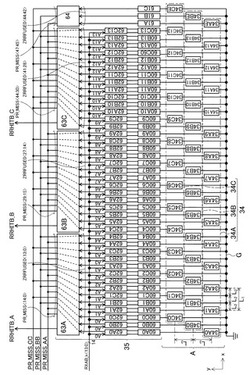

【解決手段】x方向に延伸する接地配線Gと、接地配線のy方向の一方側に設けられたヒューズ素子領域Aにx方向に沿って3列に並べて配置され、かつそれぞれの一端が接地配線Gに共通に接続される複数のヒューズ素子と、ヒューズ素子領域Aを挟んで接地配線Gの反対側に設けられ、ヒューズ素子領域Aに配置された複数のヒューズ素子それぞれの他端と接続される救済回路とを備え、上記複数のヒューズ素子は、それぞれ1つの欠陥選択線を示すアドレス情報を記憶する複数のヒューズ素子グループに所定個ずつグループ化され、同一のヒューズ素子グループに属する所定個のヒューズ素子は、同一列に配置されることを特徴とする

(もっと読む)

半導体ウエハ、半導体装置、および、半導体装置の製造方法

【課題】半導体チップのチップ面積の削減を図るとともに、半導体チップへの入力を記憶させる時間を短縮する。

【解決手段】本発明の半導体ウエハ1は、チップ領域10に形成され、絶縁膜を有し、電圧の印加による絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズ14を有するアンチヒューズ回路12と、チップ領域10を区画するダイシング領域20に複数のアンチヒューズ14の各々に対応して形成され、配線を有し、レーザー照射による配線の切断により非導通状態となる複数のレーザーヒューズ24を有するレーザーヒューズ回路22と、複数のアンチヒューズ14のうち、半導体チップへの入力に応じて非導通状態とされたレーザーヒューズ22に対応するアンチヒューズ14の有する絶縁膜に、電源からの電圧を印加させて、そのアンチヒューズ14を導通状態とする制御回路13と、を有する。

(もっと読む)

半導体装置

【課題】ヒューズ開口部からの水分侵入による電特異常及び配線腐食を防止する半導体装置を提供する。

【解決手段】シリコン基板1上に絶縁膜2とゲート酸化膜3を設け、ゲート酸化膜2上の一部にヒューズ配線4の両端にヒューズ端子15を有するヒューズを設ける。ヒューズを構成するヒューズ配線4の上方には酸化膜5を介して窒化膜14が形成された凸領域があり、ヒューズ端子15は第1金属配線7と電気的に接続している。

(もっと読む)

再構成可能な集積回路ユニットを備えた論理回路及びその論路回路のエラー修正方法

【課題】エラー箇所の特定を実施する際に、システムを停止しないでエラー発生前の高信頼性までシステム性能を復帰させる。

【解決手段】同一動作を行う複数個の再構成可能な集積回路ユニットを備え、複数の該集積回路ユニットのそれぞれに複数のバンクを有する論理回路において、入力されたデータを、複数個の前記集積回路ユニットの各バンクに振り分けて入力する入力データ制御部と、複数個の集積回路ユニットの各バンクから出力されるデータを比較して、データ間の不一致を検出するエラー解析部と、エラー解析部から、データ間の不一致の通知を受けた場合に、複数個の集積回路ユニットの該当するバンクの再構成を行う構成情報制御部と、を備える。

(もっと読む)

ヒューズ、半導体装置、半導体装置の製造方法

【課題】高電圧が不要で安定した状態を得ること。

【解決手段】半導体装置10に形成されたヒューズ素子11は、概略的に、拡散領域22と、拡散領域22と一部重なるように拡散領域22より上方に形成された導電体25を含む。半導体装置10の半導体基板21には、拡散領域22が形成されている。半導体基板21には素子分離領域23が形成されている。拡散領域22を含む半導体基板21上には絶縁膜24が形成されている。絶縁膜24上には、導電体25が形成されている。導電体25上には、カバー膜26が形成されている。カバー膜26は、導電体25の上面及び側面を覆うように形成されている。カバー膜26は、絶縁膜24より高い引っ張り応力を持つ。

(もっと読む)

半導体集積回路

【課題】半導体集積回路において消費電力を低減するとともに、ノイズの発生を低減する。

【解決手段】半導体集積回路は、複数のDFFを有し、その少なくとも1つが冗長回路とされる。半導体集積回路が通常動作モードである際に、ANDゲート1によって冗長回路であるDFF3−3に印加されるクロック信号を停止する。冗長回路へのクロック信号が停止されると、当該冗長回路においてクロック信号が停止された状態における冗長回路のドレイン−グランド間容量よりもその容量を増加させる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】半導体チップを積層して半導体装置を製造する際に、当該半導体チップの回路の不良電子素子を救済し、半導体装置の歩留まりを向上させる。

【解決手段】ウェハ10を厚み方向に貫通する一対の貫通電極50〜52を形成し、デバイス層11に一対の貫通電極50〜52を短絡する共有配線24、26、28を形成し、デバイス層11の表面11aにおいて異なる場所につながる一対のフロントバンプ20〜22を形成する。一対の貫通電極50〜52に対して異なる極性で電圧を印加し、一対の貫通電極50〜52のうちの一の貫通電極50〜52上にバックバンプ80〜82を形成する。ウェハ10を積層し、一のウェハ10上のバックバンプ80〜82と、他のデバイス層11上のフロントバンプ20〜22とを接続する。

(もっと読む)

ヒューズ回路及びトリミング良否判定方法

【課題】ヒューズ開口部の端部に必ず切断すべきヒューズを配設することにより、レーザー照射後のその切断/未切断をもって、端部のポリイミド膜の膜厚の良否を容易に判定する。

【解決手段】ヒューズ回路は、ヒューズ開口部FAの、ポリイミド膜の厚さが不本意に厚く残りやすい端部に配設された2つの切断確認用ヒューズ1a,1bと、ポリイミド膜の厚さ変動が端部に比べ少ない領域RAに配設された複数の実使用ヒューズ7a〜7dと、2つの切断確認用ヒューズ1a,1bからの信号を入力して当該ヒューズ1a,1bが確実に切断されているかを判定するヒューズ未切断判定回路2と、を備えている。なお、ヒューズ未切断判定回路2は、更にテストモード信号を入力すると共に、出力回路(例えばDQ回路)に判定結果を出力している。

(もっと読む)

半導体装置

【課題】回路規模が増大化する。

【解決手段】抵抗値が順に小さい値となって直列接続される複数のヒューズを備えるヒューズ部と、前記ヒューズ部の複数のヒューズのそれぞれ一端と、第1の電源電圧との間に接続される複数の選択スイッチと、前記第1の電源電圧から所定の電位差を有するヒューズ溶断用電圧を、前記ヒューズ部の最も小さい抵抗値のヒューズ側に出力するヒューズ溶融電圧出力回路と、ヒューズ溶断時に、前記ヒューズ溶融電圧出力回路が前記ヒューズ溶断用電圧を出力し、前記ヒューズ部の最も大きい抵抗値のヒューズに接続される選択スイッチから最も小さい抵抗値のヒューズに接続される選択スイッチまでを順に導通させる制御回路と、を備える半導体装置。

(もっと読む)

半導体装置

【課題】占有面積の小さな直線状の電気ヒューズを有する半導体装置を提供する。

【解決手段】複数の突出部10fは、電気ヒューズ部10aの中央位置からずれた位置、より具体的には、ビア10dに近くかつビア10eから遠い位置に設けられている。また、複数の突出部20fは、電気ヒューズ部20aの中央位置からずれた位置、より具体的には、ビア20dから遠くかつビア20eに近い位置に設けられている。つまり、突出部10fおよび突出部20fは、ジグザグ状に配置されている。

(もっと読む)

半導体装置

【課題】本発明は単一半導体装置を構成する複数個のチップでヒューズ信号を伝送できる半導体装置を提供する。

【解決手段】半導体装置は伝送制御信号生成部と、ヒューズ信号伝送部と、受信制御信号の生成部と、ヒューズ信号の受信部を備える。前記伝送制御信号生成部は、クロック信号を受信して複数個の分周クロック信号を生成し、前記複数個の分周クロックから伝送制御信号を生成する。前記ヒューズ信号の伝送部は前記伝送制御信号に同期してヒューズ信号を伝送する。前記受信制御信号生成部は前記クロック信号を受信して前記複数個の分周クロック信号を生成し、前記複数個の分周クロックから受信制御信号を生成する。前記ヒューズ信号受信部は前記受信制御信号に同期して前記ヒューズ信号を受信する。

(もっと読む)

半導体集積回路及び電源電圧適応制御システム

【課題】フリップフロップを備える半導体集積回路において、エラーフリップフロップを効率的に検出する。

【解決手段】半導体集積回路は、冗長フリップフロップを含む複数のフリップフロップと、セレクタ部と、エラー検出部とを備える。セレクタ部は、再構成情報に応じて選択フリップフロップを選択し、入力端子に入力されたデータが選択フリップフロップのそれぞれによって出力端子に出力されるようにデータの流れを切り替える。テストモード時、フリップフロップはスキャンチェーンを構成し、そのスキャンチェーンにはスキャンデータが入力される。そして、エラー検出部は、それぞれのフリップフロップの入出力に基づいてエラーフリップフロップを検出し、当該エラーフリップフロップが選択フリップフロップから除外されるように再構成情報を作成する。

(もっと読む)

半導体装置

【課題】安定した特性のヒューズ素子を有する半導体装置を提供する。

【解決手段】半導体装置100は、基板10と、基板10の上方に形成され、空洞部20を画成する被覆構造体30と、空洞部20に収容されたヒューズ素子40a,40b,40cと、を含み、被覆構造体30は、導電層を有し、ヒューズ素子40a,40b,40cの材質は、導電層の材質と同じである。

(もっと読む)

半導体装置の製造方法

【課題】ヒューズ(FUSE)を備えた半導体装置の信頼性を向上する。

【解決手段】半導体基板11の主面上に形成にされた多層配線を構成する層M1〜M6のうちの層M4に設けられた電気溶断型の救済用のヒューズ4aおよび試験用のヒューズ4bと、ヒューズ4aの近傍であって層M2および層M6に設けられた一対の導電板10aと、ヒューズ4bの近傍であって層M3および層M5に設けられた一対の導電板10bとから構成する。ヒューズ4bと導電板10bとの間が、ヒューズ4aと導電板10aとの間より近いものとする。

(もっと読む)

複数のレーザビームスポットを使用する半導体構造加工

【課題】複数のレーザビームを使って、半導体基板の上又は内部の導電性のあるリンクを加工する。

【解決手段】2又は3以上のNについて、スループットの利益を得るためにN組のレーザパルスを使う。前記リンクは、ほぼ長手方向に延びる実質的に平行な複数の列510、520をなして配置される。前記N組のレーザパルスは選択された構造の上に投射するまでN本のそれぞれのビーム光軸に沿って伝搬する。得られたレーザビームスポットのパターンは、N本の別個の列内のリンクか、同一の列内の別個のリンクか、同一のリンクかの上に、部分的に重複するか完全に重複するかのいずれかである。得られたレーザスポットは、互いからの前記列の長手方向のオフセットと、前記列の長手方向と垂直な方向のオフセットとの一方又は両方を有する。

(もっと読む)

半導体記憶装置

【課題】 省スペースによって従来よりも多くの論理回路及びヒューズブロックを設けることができる半導体記憶装置を提供する。

【解決手段】 ヒューズ露出窓を介して外部に露出して互いに並置された複数のヒューズ片を各々が含む複数のヒューズブロックがゲートアレイの近傍において縦列に配置され、電源配線と接地配線とが当該ヒューズ片の並置方向に沿って延在しており、ヒューズブロックの配置のために当該ゲートアレイの近傍のスペースを活用した半導体記憶装置。

(もっと読む)

半導体チップ、半導体装置及びLSI設計装置

【課題】チップコストの低下とチップ歩留りの向上とを同時に実現する。

【解決手段】実施形態に係わる半導体チップは、パッド領域11及び方形でないゲート領域12を備える第1のレイアウトL1と、第1のレイアウトL1を180°回転させた第2のレイアウトL2とを備える。第1及び第2のレイアウトL1,L2は、点対称かつ重なり合わずに結合されることによりチップレイアウトを構成する。チップレイアウトは、方形のチップ領域内に配置され、第1及び第2のレイアウトL1,L2は、それぞれ独立に動作するLSIを構成する。

(もっと読む)

自己修正可能な半導体、および自己修正可能な半導体を備えたシステム

【課題】歩留りの向上を実現できる、自己修正可能な半導体を提供する。

【解決手段】自己修正可能な半導体は、同じ機能を実行しかつ副機能ユニットを有する、多数の機能ユニットを備える。半導体は、完全または部分的な1つ以上のスペア機能ユニットを備え、当該スペア機能ユニットは、半導体へと集積される、副機能ユニットの欠陥が検出されると、その副機能ユニットは、切り替えられて、完全または部分的なスペア機能ユニットにおける副機能ユニットと、置き換えられる。この再構成は、副機能ユニットと関連付けられたスイッチング・デバイスによって実現される。欠陥のある機能ユニットや副機能ユニットは、組立後に電源を投入している最中に動作中に周期的に検出されてよく、および/又は手動で検出してもよい。

(もっと読む)

半導体装置及びその制御方法

【課題】様々な導通状態にある電気ヒューズを其々誤判定なく読み出すことのできる半導体装置及び半導体装置の制御方法を提供する。

【解決手段】選択トランジスタ903を介して検出ノードAに接続された電気ヒューズ902と、選択トランジスタ903をオフさせた状態で検出ノードAをプリチャージするプリチャージトランジスタ904と、選択トランジスタ903をオンさせ、プリチャージトランジスタ904をオフさせた状態で、検出ノードAにバイアス電流を流すバイアストランジスタ905と、検出ノードAにバイアス電流が流れている状態で検出ノードAの電位を検出する検出回路906とを備え、バイアストランジスタ905は、バイアス電流の量を段階的又は連続的に減少させる。

(もっと読む)

半導体装置及びその制御方法

【課題】様々な導通状態にある複数の電気ヒューズを有する半導体装置において、複数の電気ヒューズによりプログラミングされた結果を誤判定なく読み出すことのできる半導体装置及び半導体装置の制御方法を提供する。

【解決手段】其々がプログラム状態又は非プログラム状態である複数のヒューズ素子と、複数のヒューズ素子のプログラム状態又は非プログラム状態に対応する判定結果信号FLDa,FLDbを其々出力する複数のヒューズ判定回路92a,92bと、第1のタイミング信号LOAD_ENDを共通に受け、第1のタイミング信号LOAD_ENDに同期して複数の判定結果信号FLDa,FLDbを其々ラッチ及び出力する複数のラッチ回路93a,93bとを備える。

(もっと読む)

1 - 20 / 279

[ Back to top ]